## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**User's Manual**

# Phase-out/Discontinued

## μ**PD98501**

**Communication Controller**

Document No. S14767EJ2V0UM00 (2nd edition) Date Published April 2002 NS CP(K)

© NEC Corporation 2000 Printed in Japan

## SUMMARY OF CONTENTS

| CHAPTER 1  | INTRODUCTION                     |

|------------|----------------------------------|

| CHAPTER 2  | VR4120A CPU                      |

| CHAPTER 3  | SYSTEM CONTROLLER                |

| CHAPTER 4  | ATM CELL PROCESSOR               |

| CHAPTER 5  | ETHERNET CONTROLLER              |

| CHAPTER 6  | USB CONTROLLER                   |

| CHAPTER 7  | UART                             |

| CHAPTER 8  | TIMER                            |

| CHAPTER 9  | MICRO WIRE                       |

|            | MIPS III INSTRUCTION SET DETAILS |

| APPENDIX E | 3 VR4120A COPROCESSOR 0 HAZARDS  |

### **①** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

## **②** HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

## **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

VR4100, VR4102, VR4111, VR4120A, VR4300, VR4305, VR4310, VR4400, VR5000, VR10000, VR Series, VR4000 Series, VR4100 Series, and EEPROM are trademarks of NEC Corporation. Micro Wire is a trademark of National Semiconductor Corp. iAPX is a trademark of Intel Corp. DEC VAX is a trademark of Digital Equipment Corp. UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company, Ltd. Ethernet is a trademark of Xerox Corp. MIPS is a trademark of MIPS Technologies, Inc.

- The information in this document is current as of April, 2002. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC semiconductor products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades:

"Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products

developed based on a customer-designated "quality assurance program" for a specific application. The

recommended applications of a semiconductor product depend on its quality grade, as indicated below.

Customers must check the quality grade of each semiconductor product before using it in a particular

application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

(1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

(2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

M8E 00.4

## Major Revisions in This Edition

| Page          | Description                                                                                   |

|---------------|-----------------------------------------------------------------------------------------------|

| Throughout    | Elimination of descriptions to MIPS16 instruction mode, N-Wire Interface, ABR and GFR         |

| p.34          | 1.6 Pin Configuration (Bottom View)                                                           |

|               | Change of pin name of AC14, AC17, AD15, AD16, AD17, AD18, AE15, AE16, AE17, AF15, AF16, AF18  |

| pp.35, 41     | Addition of 1.7.1 Power Supply, 1.7.12 IC-Open, 1.7.13 IC-PDn, 1.7.14 IC-PDnR, 1.7.15 IC-PUp, |

|               | and 1.7.16 IC-PUpR                                                                            |

| pp.35 to 40   | 1.7 Pin Function                                                                              |

|               | Addition of description to functions of PSAVD, PSDVD, PUAVD, PUDVD, PSMD_B, PSTBY,            |

|               | PUMD_B, PUSTBY, MIRCLK, MITCLK, MI2RCLK, MI2TCLK, USBCLK, URCLK                               |

| pp.42 to 47   | 1.8 I/O Register Map                                                                          |

|               | Change of register name of ATM (F0B0H-F0B3H), Ether (234H-23CH), USB (100H-FFCH) 2.1.10 Cache |

| p.61          | Change of the instruction/data cache size                                                     |

| pp.80 to 96   | 2.3 Pipeline                                                                                  |

| pp.00 to 00   | Elimination of description to $\Phi$ 1 and $\Phi$ 2. Elimination of description to IT stage   |

| pp.97 to 127  | 2.4 Memory Management System                                                                  |

|               | Change of description                                                                         |

| p.134         | 2.5.3.5 Status register (12)                                                                  |

|               | Change of description to status register diagnostic status field                              |

| p.143         | Table 2-39. Exception Priority Order                                                          |

|               | Change of description                                                                         |

| p.167         | 2.7.2 Cache organization                                                                      |

|               | Change of description of cache line size for instruction cache                                |

| p.185         | Addition of 3.1.5 EEPROM                                                                      |

| pp.188 to 199 | 3.2 Registers                                                                                 |

| n 200         | Change of description 3.3.1 Overview                                                          |

| p.200         | Addition of description to 8-word burst R/W                                                   |

| pp.203 to 220 | 3.4 Memory Interface                                                                          |

| pp.200 to 220 | Change of description                                                                         |

| pp.227 to 274 | CHAPTER 4 ATM CELL PROCESSOR                                                                  |

|               | Elimination of description to IP flow                                                         |

|               | Change of description of registers                                                            |

| pp.277 to 297 | 5.2 Registers                                                                                 |

|               | Change of description                                                                         |

| pp.309 to 327 | 6.2 Registers                                                                                 |

|               | Change of description                                                                         |

| pp.369 to 379 | 7.3 Registers                                                                                 |

|               | Change of description                                                                         |

| pp.433 to 523 | APPENDIX A MIPS III INSTRUCTION SET DETAILS                                                   |

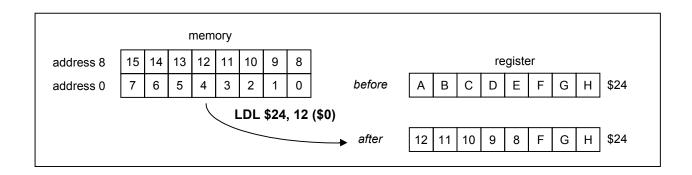

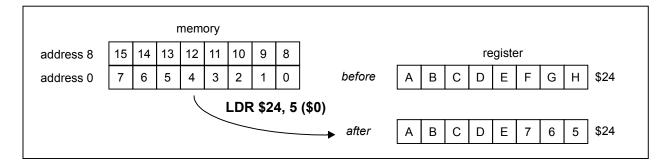

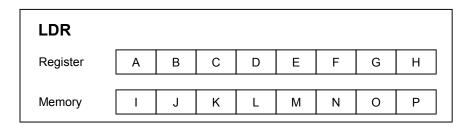

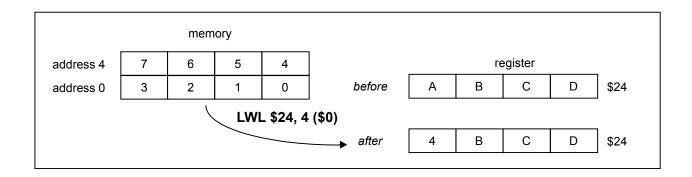

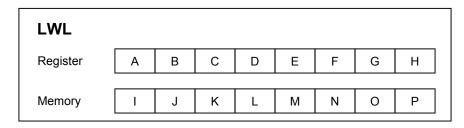

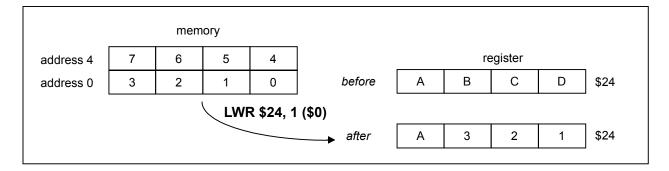

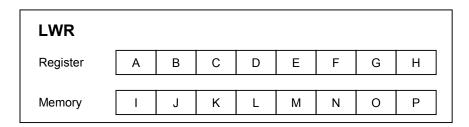

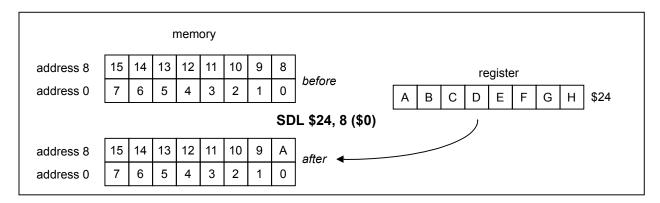

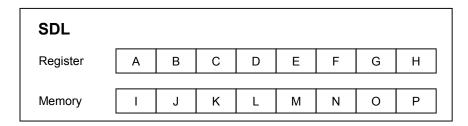

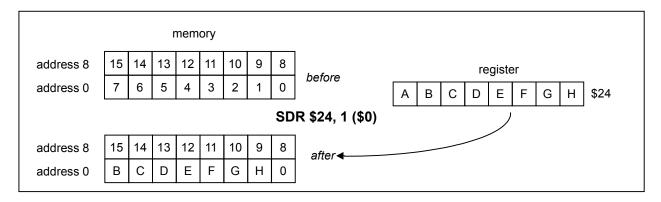

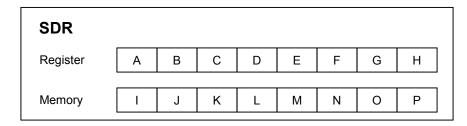

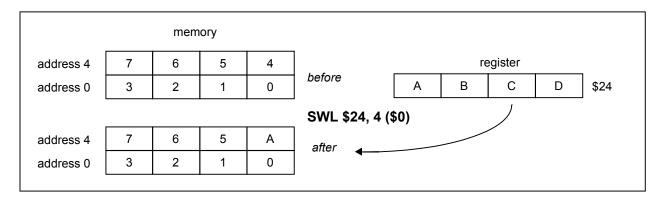

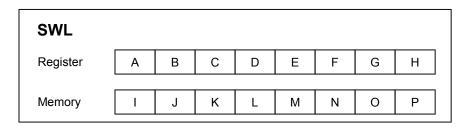

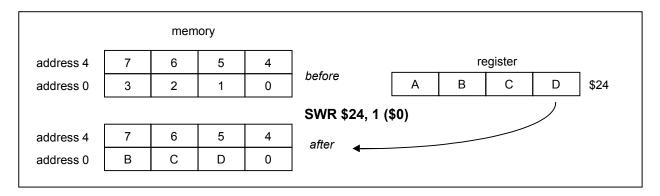

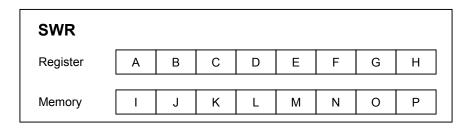

|               | Change of description to DMACC, LDL, LDR, LWL, LWR, SDL, SDR, SWL, SWR                        |

| p.547         | Table B-1 VR4120A CPU Coprocessor 0 Hazards                                                   |

|               | Elimination of description to TLB shut down                                                   |

## PREFACE

| Readers          |                                                              | r engineers who need to be familiar with the capability of evelop application systems based on it. |

|------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Purpose          | The purpose of this manual (listed below) of the $\mu$ PD985 | al is to help users understand the hardware capabilities 501.                                      |

| Configuration    | This manual consists of the                                  | following chapters:                                                                                |

|                  | Introduction                                                 |                                                                                                    |

|                  | <ul> <li>VR4120A<sup>™</sup> CPU</li> </ul>                  |                                                                                                    |

|                  | System controller                                            |                                                                                                    |

|                  | <ul> <li>ATM cell processor</li> </ul>                       |                                                                                                    |

|                  | <ul> <li>Ethernet<sup>™</sup> controller</li> </ul>          |                                                                                                    |

|                  | USB controller                                               |                                                                                                    |

|                  | • UART                                                       |                                                                                                    |

|                  | Timer                                                        |                                                                                                    |

|                  | <ul> <li>Micro Wire™</li> </ul>                              |                                                                                                    |

| Guidance         | Readers of this manual sho                                   | uld already have a general knowledge of electronics, logic                                         |

|                  | circuits, and microcomputer                                  | S.                                                                                                 |

|                  | To gain an overall understa                                  | nding of the function of the $\mu$ PD98501:                                                        |

|                  | ightarrow Read through all the chap                          | pters, in sequence.                                                                                |

|                  | To check the electrical chara                                | acteristics of the $\mu$ PD98501:                                                                  |

|                  | ightarrow Refer to the separate dat                          | ta sheet.                                                                                          |

| Notation         | This manual uses the follow                                  | ing conventions:                                                                                   |

|                  | Data bit significance:                                       | High-order bits on the left side;                                                                  |

|                  | g                                                            | low-order bits on the right side                                                                   |

|                  | Active low:                                                  | XXXX_B (Pin and signal names are suffixed with _B.)                                                |

|                  | Note:                                                        | Explanation of an indicated part of text                                                           |

|                  | Caution:                                                     | Information requiring the user's special attention                                                 |

|                  | Remark:                                                      | Supplementary information                                                                          |

|                  | Numerical value:                                             | Binary xxxx or xxxxB                                                                               |

|                  |                                                              | Decimal xxxx                                                                                       |

|                  |                                                              | Hexadecimal xxxxH                                                                                  |

| Related Document | Use this manual in combina                                   | tion with the following document.                                                                  |

|                  |                                                              | cated in this publication may include preliminary versions.                                        |

|                  | However, preliminary versio                                  |                                                                                                    |

|                  | <ul> <li>μPD98501 Data Sheet: S</li> </ul>                   | S14828E                                                                                            |

|                  | <ul> <li>μPD98501 Application No</li> </ul>                  | ote ATM Cell Processor Control: S15812E                                                            |

## CONTENTS

| CHAPTER 1 INTRODUCTION                        |    |

|-----------------------------------------------|----|

| 1.1 Features                                  |    |

| 1.2 Ordering Information                      |    |

| 1.3 System Configuration                      |    |

| 1.4 Block Diagram (Summary)                   |    |

| 1.5 Block Diagram (Detail)                    |    |

| 1.5.1 VR4120A RISC processor core             |    |

| 1.5.2 IBUS                                    |    |

| 1.5.3 System controller                       |    |

| 1.5.4 ATM cell processor                      |    |

| 1.5.5 Ethernet controller                     |    |

| 1.5.6 USB controller                          |    |

| 1.6 Pin Configuration (Bottom View)           |    |

| 1.7 Pin Function                              |    |

| 1.7.1 Power Supply                            |    |

| 1.7.2 System PLL power supply                 |    |

| 1.7.3 USB PLL power supply                    |    |

| 1.7.4 System control interface                |    |

| 1.7.5 Memory interface                        |    |

| 1.7.6 ATM interface                           |    |

| 1.7.7 Ethernet interface                      |    |

| 1.7.8 USB interface                           |    |

| 1.7.9 UART/Micro Wire interface               |    |

| 1.7.10 Parallel port interface                |    |

| 1.7.11 Boundary scan interface                |    |

| 1.7.12 I.C Open                               |    |

| 1.7.13 I.C Pull Down                          |    |

| 1.7.14 I.C Pull Down with Resistor            |    |

| 1.7.15 I.C Pull Up                            |    |

| 1.7.16 I.C Pull Up with Resistor              |    |

| 1.8 I/O Register Map                          |    |

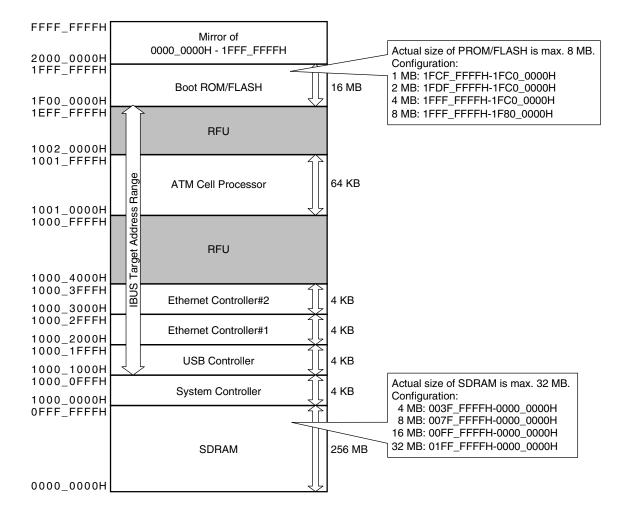

| 1.9 Memory Map                                |    |

| 1.10 Reset Configuration                      |    |

| 1.11 Interrupts                               |    |

| 1.12 Clock Control Unit                       |    |

| CHAPTER 2 VR4120A                             |    |

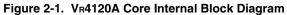

| 2.1 Overview for VR4120A                      |    |

| 2.1.1 Internal block configuration            |    |

| 2.1.2 VR4120A registers                       |    |

| 2.1.3 VR4120A instruction set overview        |    |

| 2.1.4 Data formats and addressing             |    |

| 2.1.5 Coprocessors (CP0)                      |    |

| 2.1.6 Floating-point unit (FPU)               |    |

| 2.1.7 CPU core memory management system (MMU) | 60 |

| 2.1.8 Translation lookaside buffer (TLB)              | 60 |

|-------------------------------------------------------|----|

| 2.1.9 Operating modes                                 | 61 |

| 2.1.10 Cache                                          | 61 |

| 2.1.11 Instruction pipeline                           | 61 |

| 2.2 MIPS III Instruction Set Summary                  | 62 |

| 2.2.1 MIPS III ISA instruction formats                | 62 |

| 2.2.2 Instruction classes                             | 63 |

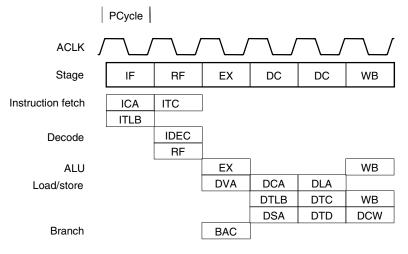

| 2.3 Pipeline                                          | 80 |

| 2.3.1 Pipeline stages                                 | 80 |

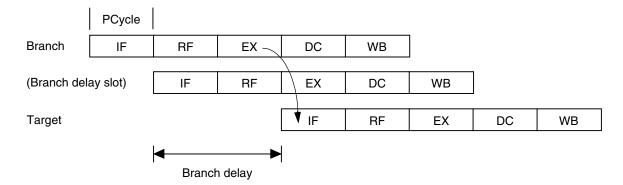

| 2.3.2 Branch delay                                    | 83 |

| 2.3.3 Load delay                                      | 83 |

| 2.3.4 Pipeline operation                              | 84 |

| 2.3.5 Interlock and exception handling                | 90 |

| 2.3.6 Program compatibility                           |    |

| 2.4 Memory Management System                          |    |

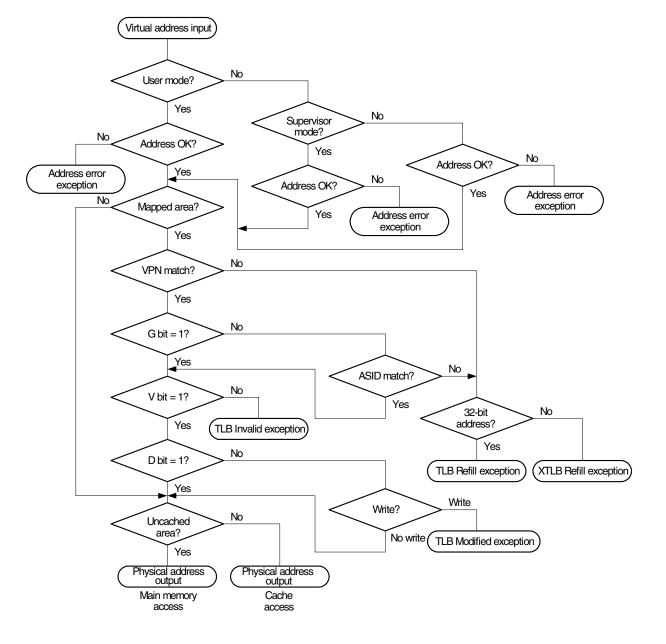

| 2.4.1 Translation lookaside buffer (TLB)              |    |

| 2.4.2 Virtual-to-physical address transition          |    |

| 2.4.3 Virtual address space                           |    |

| 2.4.4 Physical address space                          |    |

| 2.4.5 System control coprocessor                      |    |

| 2.4.6 Memory management registers                     |    |

| 2.5 Exception Processing                              |    |

| 2.5.1 Exception processing operation                  |    |

| 2.5.2 Precision of exceptions                         |    |

| 2.5.3 Exception processing registers                  |    |

| 2.5.4 Details of exceptions                           |    |

| 2.5.5 Exception processing and servicing flowcharts   |    |

| 2.6 Initialization Interface                          |    |

| 2.6.1 Cold reset                                      |    |

| 2.6.2 Soft reset                                      |    |

| 2.6.3 VR4120A processor modes                         |    |

| 2.7 Cache Memory                                      |    |

| 2.7.1 Memory organization                             |    |

| 2.7.2 Cache organization                              |    |

| 2.7.3 Cache operations                                |    |

| 2.7.4 Cache states                                    |    |

| 2.7.5 Cache state transition diagrams                 |    |

| 2.7.6 Cache data integrity                            |    |

| 2.7.7 Manipulation of the caches by an external agent |    |

| 2.8 CPU Core Interrupts                               |    |

| 2.8.1 Non-maskable interrupt (NMI)                    |    |

| 2.8.2 Ordinary interrupts                             |    |

| 2.8.3 Software interrupts generated in CPU core       |    |

| 2.8.4 Timer interrupt                                 |    |

| 2.8.5 Asserting interrupts                            |    |

| HAPTER 3 SYSTEM CONTROLLER                            |    |

| 3.1 Overview                                          |    |

|                                                    | <b>Phase-out/Discontinued</b> |

|----------------------------------------------------|-------------------------------|

| 3.1.1 CPU interface                                |                               |

| 3.1.2 Memory interface                             |                               |

| 3.1.3 IBUS interface                               |                               |

| 3.1.4 UART                                         |                               |

| 3.1.5 EEPROM                                       |                               |

| 3.1.6 Timer                                        |                               |

| 3.1.7 Interrupt controller                         |                               |

| 3.1.8 DSU (Deadman's SW unit)                      |                               |

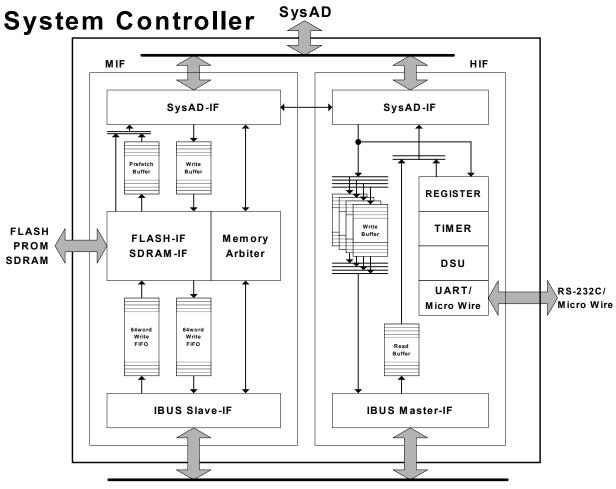

| 3.1.9 System block diagram                         |                               |

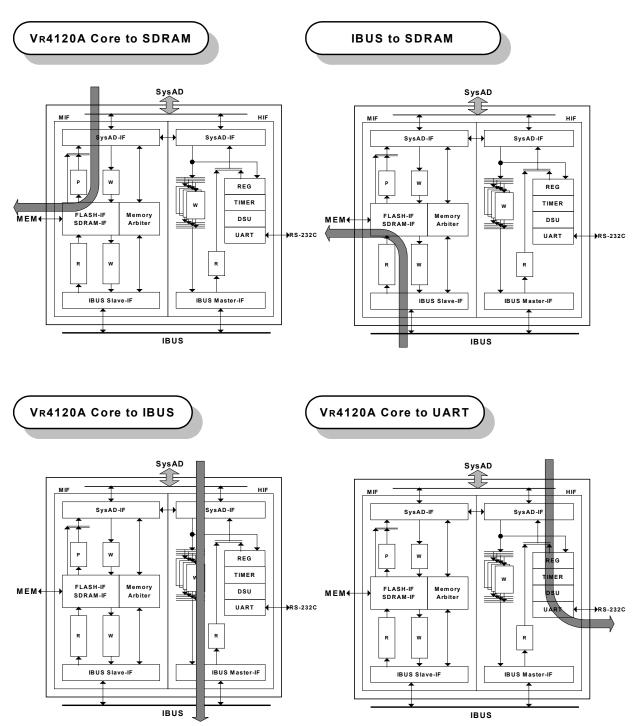

| 3.1.10 Data flow diagram                           |                               |

| 3.2 Registers                                      |                               |

| 3.2.1 Register summary                             |                               |

| 3.2.2 General registers                            |                               |

| 3.3 CPU Interface                                  |                               |

| 3.3.1 Overview                                     |                               |

| 3.3.2 Data rate control                            |                               |

| 3.3.3 Address decoding                             |                               |

| 3.3.4 Endian conversion                            |                               |

| 3.3.5 I/O performance                              |                               |

| 3.4 Memory Interface                               |                               |

| 3.4.1 Overview                                     |                               |

| 3.4.2 Memory regions and devices                   |                               |

| 3.4.3 Memory signal connections                    |                               |

| 3.4.4 Memory performance                           |                               |

| 3.4.5 Memory control registers                     |                               |

| 3.4.6 Boot ROM / Extended chip select              |                               |

| 3.4.7 SDRAM                                        |                               |

| 3.4.8 SDRAM refresh                                |                               |

| 3.4.9 Memory-to-CPU prefetch FIFO                  |                               |

| 3.4.10 CPU-to-memory write FIFO                    |                               |

| 3.4.11 SDRAM memory initialization                 |                               |

| 3.5 IBUS Interface Register                        |                               |

| 3.5.1 ITCNTR (IBUS timeout timer control register) |                               |

| 3.5.2 ITSETR (IBUS timeout timer set register)     |                               |

| 3.6 DSU (Deadman's SW Unit)                        |                               |

| 3.6.1 Overview                                     |                               |

| 3.6.2 Registers                                    |                               |

| 3.6.3 DSU register setting flow                    |                               |

| 3.7 Endian Mode Software Issues                    |                               |

| 3.7.1 Overview                                     |                               |

| 3.7.2 Endian modes                                 |                               |

| CHAPTER 4 ATM CELL PROCESSOR                       |                               |

| 4.1 Overview                                       |                               |

| 4.1.1 Function features                            |                               |

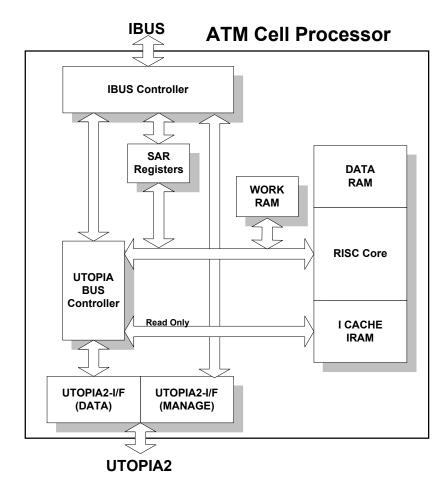

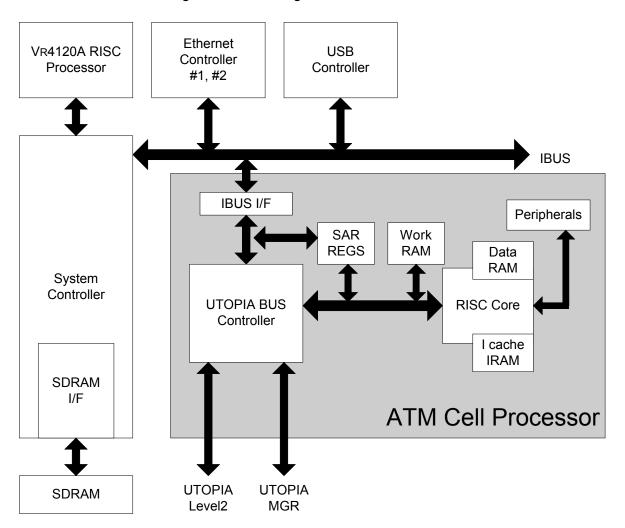

| 4.1.2 Block diagram of ATM cell processor          |                               |

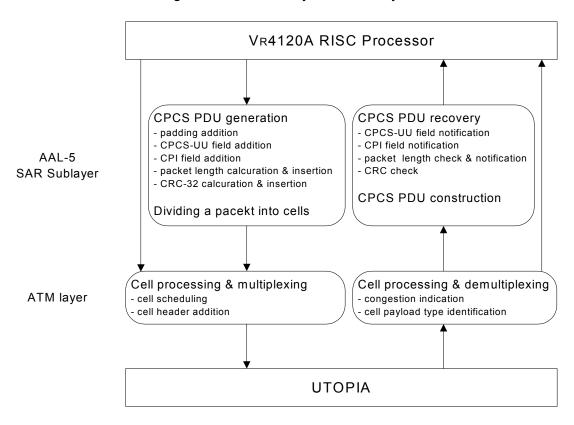

| 4.1.3 ATM cell processing operation overview       |                               |

| 4.2 Memory Space                                   |                               |

| 4.2.1 Work RAM and register space                                | 235 |

|------------------------------------------------------------------|-----|

| 4.2.2 Shared memory                                              | 235 |

| 4.3 Interruption                                                 | 235 |

| 4.4 Registers for ATM Cell Processing                            | 236 |

| 4.4.1 Register map                                               | 236 |

| 4.4.2 A_GMR (General Mode Register)                              | 238 |

| 4.4.3 A_GSR (General Status Register)                            | 238 |

| 4.4.4 A_IMR (Interrupt Mask Register)                            | 239 |

| 4.4.5 A_RQU (Receiving Queue Underrun Register)                  | 240 |

| 4.4.6 A_RQA (Receiving Queue Alert Register)                     | 240 |

| 4.4.7 A_VER (Version Register)                                   | 240 |

| 4.4.8 A_CMR (Command Register)                                   | 240 |

| 4.4.9 A_CER (Command Extension Register)                         | 240 |

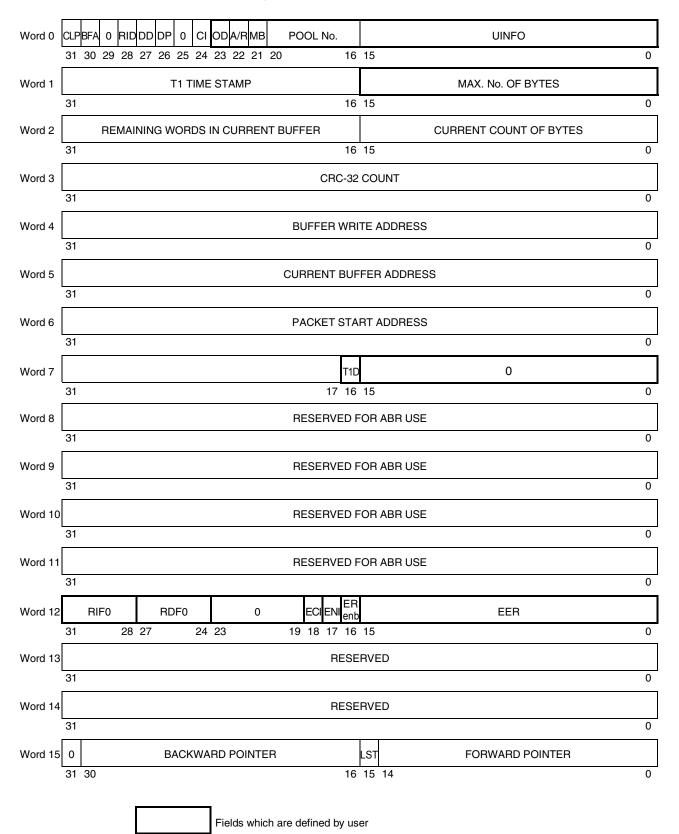

| 4.4.10 A_MSA0 to A_MSA3 (Mailbox Start Address Register)         | 241 |

| 4.4.11 A_MBA0 to A_MBA3 (Mailbox Bottom Address Register)        | 241 |

| 4.4.12 A_MTA0 to A_MTA3 (Mailbox Tail Address Register)          | 241 |

| 4.4.13 A_MWA0 to A_MWA3 (Mailbox Write Address Register)         |     |

| 4.4.14 A_RCC (Valid Received Cell Counter)                       |     |

| 4.4.15 A_TCC (Valid Transmitted Cell Counter)                    |     |

| 4.4.16 A_RUEC (Receive Unprovisioned VPI/VCI Error Cell Counter) |     |

| 4.4.17 A_RIDC (Receive Internal Dropped Cell Counter)            |     |

| 4.4.18 A_T1R (T1 Time Register)                                  |     |

| 4.4.19 A_TSR (Time Stamp Register)                               |     |

| 4.4.20 A_IBBAR (IBUS Base Address Register)                      |     |

| 4.4.21 A_INBAR (Instruction Base Address Register)               |     |

| 4.4.22 A_UMCMD (UTOPIA Management Interface Command Register)    |     |

| 4.5 Data Structure                                               | 245 |

| 4.5.1 Tx buffer structure                                        |     |

| 4.5.2 Rx pool structure                                          | 248 |

| 4.6 Initialization                                               | 253 |

| 4.6.1 Before starting RISC core                                  |     |

| 4.6.2 After RISC core's F/W is starting                          |     |

| 4.7 Commands                                                     |     |

| 4.7.1 Set_Link_Rate command                                      |     |

| 4.7.2 Open_Channel command                                       |     |

| 4.7.3 Close_Channel command                                      |     |

| 4.7.4 Tx_Ready command                                           |     |

| 4.7.5 Add_Buffers command                                        |     |

| 4.7.6 Indirect_Access command                                    |     |

| 4.8 Operations                                                   |     |

| 4.8.1 Work RAM usage                                             |     |

| 4.8.2 Transmission function                                      |     |

| 4.8.3 Receiving function                                         |     |

| 4.8.4 Mailbox                                                    |     |

|                                                                  |     |

| IAPTER 5 ETHERNET CONTROLLER                                     |     |

| 5.1 Overview                                                     |     |

| 5.1.1 Features                                                   | 275 |

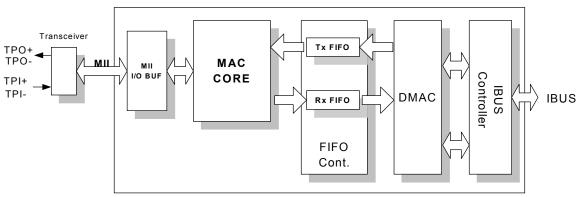

| 5.1.2 Block diagram of Ethernet controller block     | 275 |

|------------------------------------------------------|-----|

| 5.2 Registers                                        | 277 |

| 5.2.1 Register map                                   | 277 |

| 5.2.2 En_MACC1 (MAC Configuration Register 1)        | 283 |

| 5.2.3 En_MACC2 (MAC Configuration Register 2)        | 284 |

| 5.2.4 En_IPGT (Back-to-Back IPG Register)            |     |

| 5.2.5 En_IPGR (Non Back-to-Back IPG Register)        | 284 |

| 5.2.6 En_CLRT (Collision Register)                   | 285 |

| 5.2.7 En_LMAX (Maximum Packet Length Register)       | 285 |

| 5.2.8 En_RETX (Retry Count Register)                 | 285 |

| 5.2.9 En_LSA2 (Station Address Register 2)           | 285 |

| 5.2.10 En_LSA1 (Station Address Register 1)          | 285 |

| 5.2.11 En_PTVR (Pause Timer Value Read Register)     | 286 |

| 5.2.12 En_VLTP (VLAN Type Register)                  |     |

| 5.2.13 En_MIIC (MII Configuration Register)          |     |

| 5.2.14 En_MCMD (MII Command Register)                | 286 |

| 5.2.15 En_MADR (MII Address Register)                | 287 |

| 5.2.16 En_MWTD (MII Write Data Register)             | 287 |

| 5.2.17 En_MRDD (MII Read Data Register)              |     |

| 5.2.18 En_MIND (MII Indicate Register)               |     |

| 5.2.19 En_AFR (Address Filtering Register)           |     |

| 5.2.20 En_HT1 (Hash Table Register 1)                |     |

| 5.2.21 En_HT2 (Hash Table Register 2)                |     |

| 5.2.22 En_CAR1 (Carry Register 1)                    | 289 |

| 5.2.23 En_CAR2 (Carry Register 2)                    | 290 |

| 5.2.24 En_CAM1 (Carry Register 1 Mask Register)      |     |

| 5.2.25 En_CAM2 (Carry Register 2 Mask Register)      | 292 |

| 5.2.26 En_TXCR (Transmit Configuration Register)     | 292 |

| 5.2.27 En_TXFCR (Transmit FIFO Control Register)     | 293 |

| 5.2.28 En_TXDPR (Transmit Descriptor Pointer)        |     |

| 5.2.29 En_RXCR (Receive Configuration Register)      |     |

| 5.2.30 En_RXFCR (Receive FIFO Control Register)      | 295 |

| 5.2.31 En_RXDPR (Receive Descriptor Pointer)         | 295 |

| 5.2.32 En_RXPDR (Receive Pool Descriptor Pointer)    | 296 |

| 5.2.33 En_CCR (Configuration Register)               | 296 |

| 5.2.34 En_ISR (Interrupt Service Register)           | 296 |

| 5.2.35 En_MSR (Mask Service Register)                | 297 |

| 5.3 Operation                                        | 298 |

| 5.3.1 Initialization                                 | 298 |

| 5.3.2 Buffer structure for Ethernet Controller block | 298 |

| 5.3.3 Buffer descriptor format                       | 299 |

| 5.3.4 Frame transmission                             | 301 |

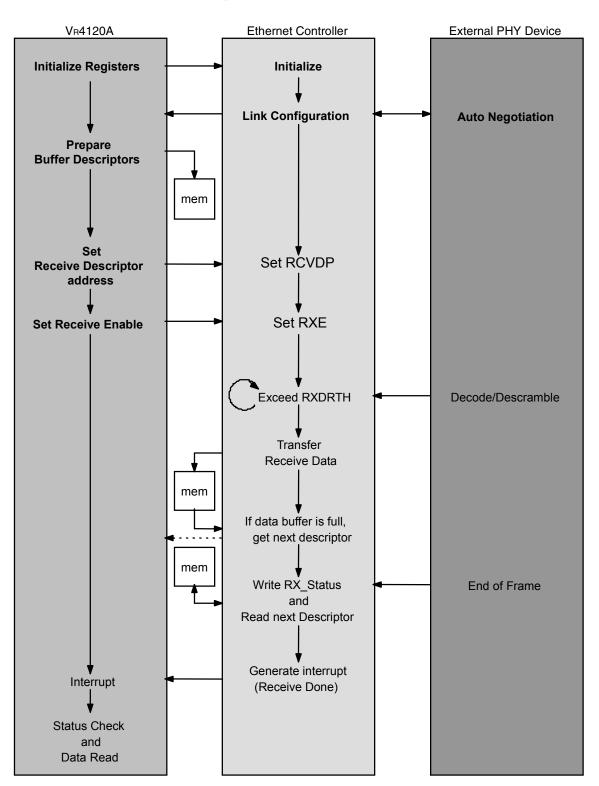

| 5.3.5 Frame reception                                | 303 |

| 5.3.6 Address Filtering                              | 305 |

|                                                      |     |

| CHAPTER 6 USB CONTROLLER                             | 307 |

| 6.1 Overview                                         | 307 |

| 6.1.1 Features                                       | 307 |

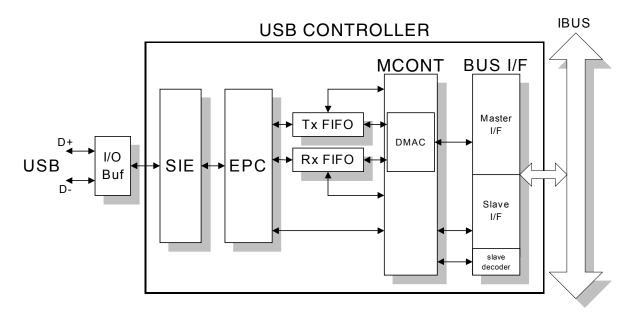

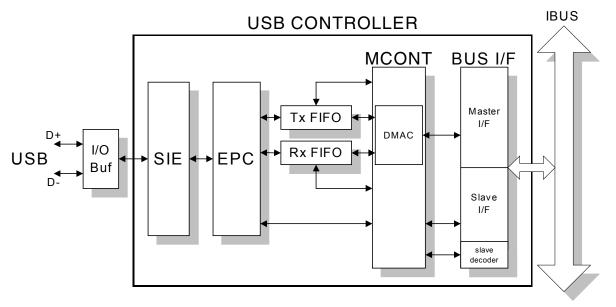

| 6.1.2 Internal block diagram                           |     |

|--------------------------------------------------------|-----|

| 6.2 Registers                                          | 309 |

| 6.2.1 Register map                                     |     |

| 6.2.2 U_GMR (USB General Mode Register)                | 311 |

| 6.2.3 U_VER (USB Frame Number/Version Register)        | 311 |

| 6.2.4 U_GSR1 (USB General Status Register 1)           | 312 |

| 6.2.5 U_IMR1 (USB Interrupt Mask Register 1)           | 314 |

| 6.2.6 U_GSR2 (USB General Status Register 2)           | 316 |

| 6.2.7 U_IMR2 (USB Interrupt Mask Register 2)           | 317 |

| 6.2.8 U_EP0CR (USB EP0 Control Register)               | 318 |

| 6.2.9 U_EP1CR (USB EP1 Control Register)               | 319 |

| 6.2.10 U_EP2CR (USB EP2 Control Register)              |     |

| 6.2.11 U_EP3CR (USB EP3 Control Register)              |     |

| 6.2.12 U_EP4CR (USB EP4 Control Register)              |     |

| 6.2.13 U_EP5CR (USB EP5 Control Register)              |     |

| 6.2.14 U_EP6CR (USB EP6 Control Register)              |     |

| 6.2.15 U_CMR (USB Command Register)                    |     |

| 6.2.16 U_CA (USB Command Address Register)             |     |

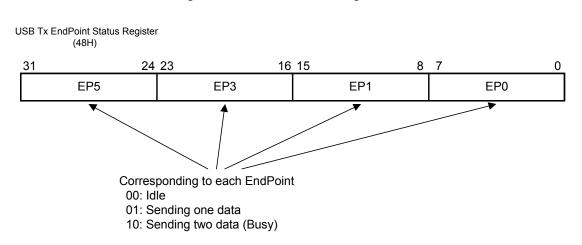

| 6.2.17 U_TEPSR (USB Tx EndPoint Status Register)       |     |

| 6.2.18 U_RP0IR (USB Rx Pool0 Information Register)     |     |

| 6.2.19 U_RP0AR (USB Rx Pool0 Address Register)         |     |

| 6.2.20 U_RP1IR (USB Rx Pool1 Information Register)     |     |

| 6.2.21 U_RP1AR (USB Rx Pool1 Address Register)         |     |

| 6.2.22 U_RP2IR (USB Rx Pool2 Information Register)     |     |

| 6.2.23 U_RP2AR (USB Rx Pool2 Address Register)         |     |

| 6.2.24 U_TMSA (USB Tx MailBox Start Address Register)  |     |

| 6.2.25 U_TMBA (USB Tx MailBox Bottom Address Register) |     |

| 6.2.26 U_TMRA (USB Tx MailBox Read Address Register)   |     |

| 6.2.27 U_TMWA (USB Tx MailBox Write Address Register)  |     |

| 6.2.28 U_RMSA (USB Rx MailBox Start Address Register)  |     |

| 6.2.29 U_RMBA (USB Rx MailBox Bottom Address Register) |     |

| 6.2.30 U_RMRA (USB Rx MailBox Read Address Register)   |     |

| 6.2.31 U_RMWA (USB Rx MailBox Write Address Register)  |     |

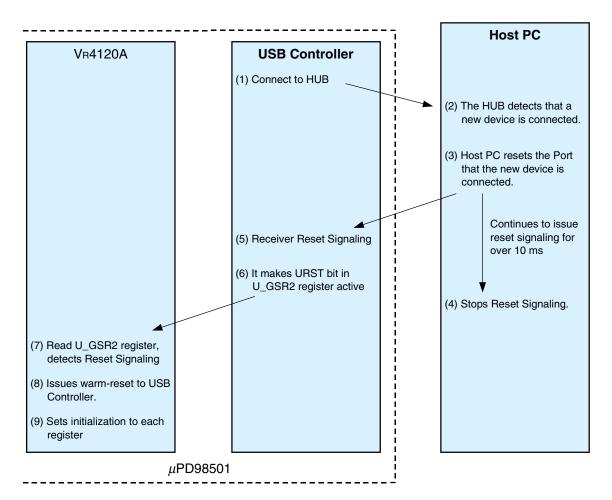

| 6.3 USB Attachment Sequence                            |     |

| 6.4 Initialization                                     |     |

| 6.4.1 Receive pool settings                            |     |

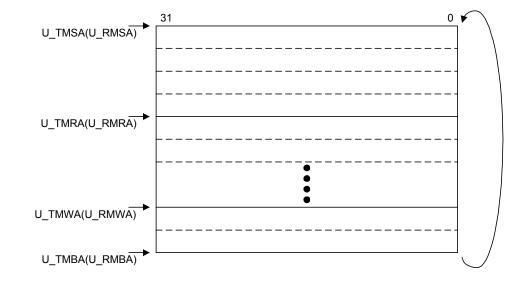

| 6.4.2 Transmit/receive MailBox settings                |     |

| 6.5 Data Transmit Function                             |     |

| 6.5.1 Overview of transmit processing                  |     |

| 6.5.2 Tx buffer configuration                          |     |

| 6.5.3 Data transmit modes                              |     |

| 6.5.4 VR4120A processing at data transmitting          |     |

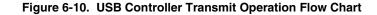

| 6.5.5 USB controller processing at data transmitting   |     |

| 6.5.6 Tx indication                                    |     |

| 6.6 Data Receive Function                              |     |

| 6.6.1 Overview of receive processing                   |     |

| 6.6.2 Rx Buffer configuration                          |     |

| 6.6.3 Receive pool settings                            |     |

|                                                        |     |

| 6.6.4 Data receive mode                                            | 346 |

|--------------------------------------------------------------------|-----|

| 6.6.5 VR4120A receive processing                                   | 349 |

| 6.6.6 USB controller receive processing                            | 350 |

| 6.6.7 Detection of errors on USB                                   |     |

| 6.6.8 Rx data corruption on Isochronous EndPoint                   |     |

| 6.6.9 Rx FIFO overrun                                              | 359 |

| 6.6.10 Rx indication                                               | 360 |

| 6.7 Power Management                                               | 362 |

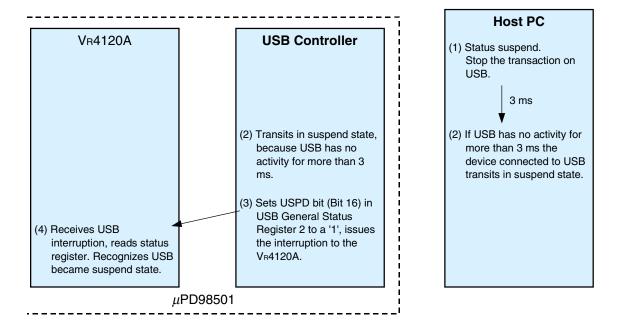

| 6.7.1 Suspend                                                      | 362 |

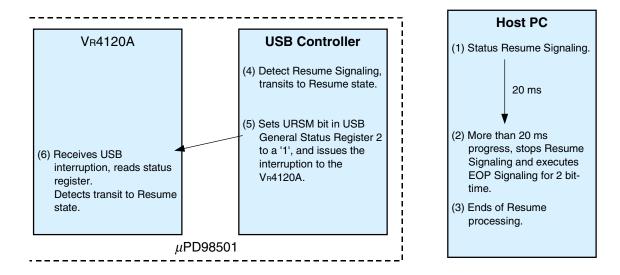

| 6.7.2 Resume                                                       | 363 |

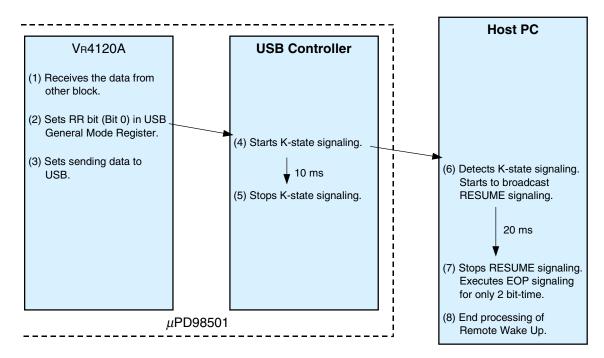

| 6.7.3 Remote wake up                                               |     |

| 6.8 Receiving SOF Packet                                           |     |

| 6.8.1 Receiving SOF Packet and updating the Frame Number           | 365 |

| 6.8.2 Updating Frame Number automatically                          |     |

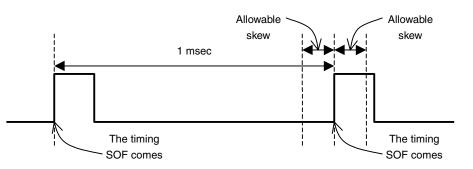

| 6.8.3 Checking if the skew of SOF arrival time is allowable of not |     |

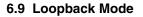

| 6.9 Loopback Mode                                                  |     |

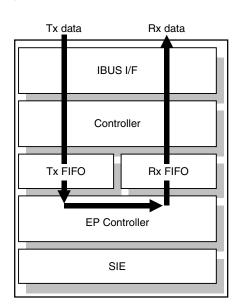

| 6.10 Example of Connection                                         | 367 |

|                                                                    |     |

| CHAPTER 7 UART                                                     |     |

| 7.1 Overview                                                       |     |

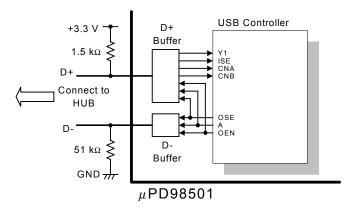

| 7.2 UART Block Diagram                                             |     |

| 7.3 Registers                                                      |     |

| 7.3.1 Register map                                                 |     |

| 7.3.2 UARTRBR (UART Receiver data Buffer Register)                 |     |

| 7.3.3 UARTTHR (UART Transmitter data Holding Register)             |     |

| 7.3.4 UARTIER (UART Interrupt Enable Register)                     |     |

| 7.3.5 UARTDLL (UART Divisor Latch LSB Register)                    |     |

| 7.3.6 UARTDLM (UART Divisor Latch MSB Register)                    |     |

| 7.3.7 UARTIIR (UART Interrupt ID Register)                         |     |

| 7.3.8 UARTFCR (UART FIFO Control Register)                         |     |

| 7.3.9 UARTLCR (UART Line Control Register).                        |     |

| 7.3.10 UARTMCR (UART Modem Control Register)                       |     |

| 7.3.11 UARTLSR (UART Line Status Register)                         |     |

| 7.3.12 UARTMSR (UART Modem Status Register)                        |     |

| 7.3.13 UARTSCR (UART Scratch Register)                             |     |

| CHAPTER 8 TIMER                                                    | 200 |

| 8.1 Overview                                                       |     |

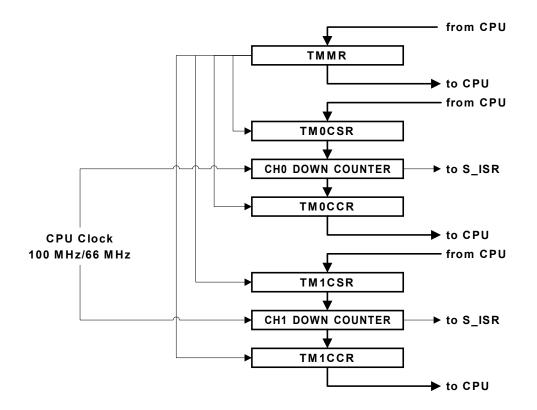

| 8.2 Block Diagram                                                  |     |

| -                                                                  |     |

| 8.3 Registers                                                      |     |

| 8.3.2 TMMR (Timer Mode Register)                                   |     |

| 8.3.3 TM0CSR (Timer CH0 Count Set Register)                        |     |

| 8.3.4 TMICSR (Timer CH1 Count Set Register)                        |     |

| 8.3.5 TM0CCR (Timer CH0 Current Count Register)                    |     |

| 8.3.6 TMICCR (Timer CH1 Current Count Register)                    |     |

|                                                                    |     |

| CHAPTER 9 MICRO WIRE                                               |     |

| 9.1 Overview                                                                                                             |  |

|--------------------------------------------------------------------------------------------------------------------------|--|

| 9.2 Operations                                                                                                           |  |

| 9.2.1 Data read at the power up load                                                                                     |  |

| 9.2.2 Accessing to EEPROM                                                                                                |  |

| 9.3 Registers                                                                                                            |  |

| 9.3.1 Register map                                                                                                       |  |

| 9.3.2 ECCR (EEPROM Command Control Register)                                                                             |  |

| 9.3.3 ERDR (EEPROM Read Data Register)                                                                                   |  |

| 9.3.4 MACAR1 (MAC Address Register 1)                                                                                    |  |

| 9.3.5 MACAR2 (MAC Address Register 2)                                                                                    |  |

| 9.3.6 MACAR3 (MAC Address Register 3)                                                                                    |  |

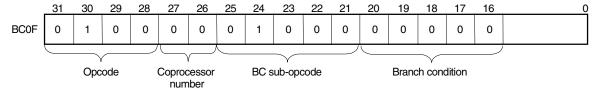

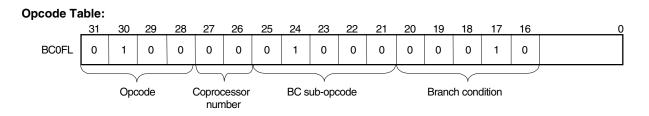

| APPENDIX A MIPS III INSTRUCTION SET DETAILS                                                                              |  |

|                                                                                                                          |  |

| A.1 Instruction Notation Conventions                                                                                     |  |

| A.1 Instruction Notation Conventions<br>A.2 Load and Store Instructions                                                  |  |

|                                                                                                                          |  |

| A.2 Load and Store Instructions                                                                                          |  |

| A.2 Load and Store Instructions<br>A.3 Jump and Branch Instructions                                                      |  |

| A.2 Load and Store Instructions<br>A.3 Jump and Branch Instructions<br>A.4 System Control Coprocessor (CP0) Instructions |  |

## LIST OF FIGURES (1/5)

| Figure No.                                         | Title                    | Page |

|----------------------------------------------------|--------------------------|------|

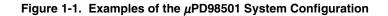

| 1-1. Examples of the $\mu$ PD98501 System Config   | uration                  | 24   |

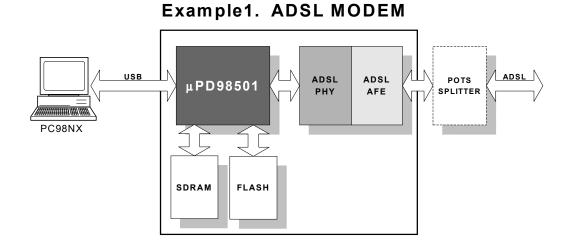

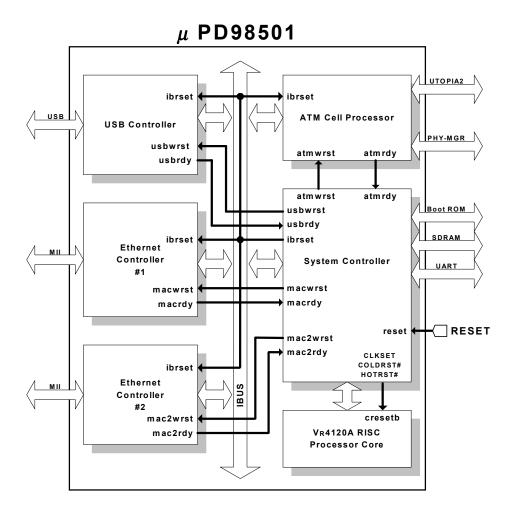

| 1-2. Block Diagram of the $\mu$ PD98501            |                          | 25   |

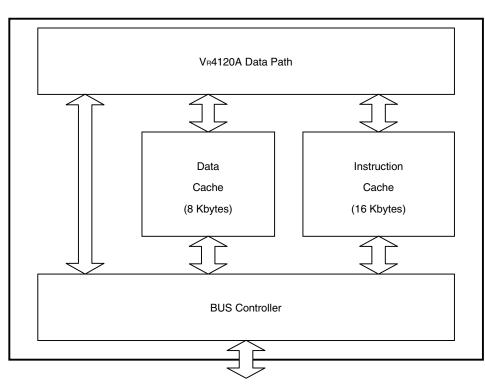

| 1-3. Block Diagram of the VR4120A RISC Proce       | essor                    | 26   |

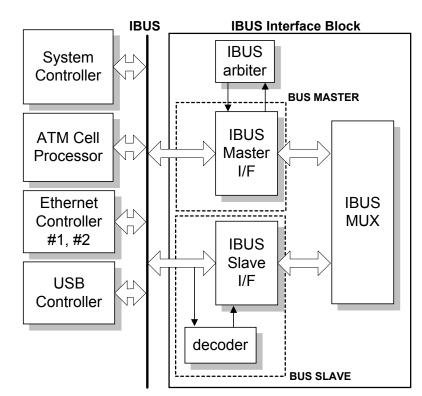

| 1-4. Block Diagram of IBUS                         |                          | 27   |

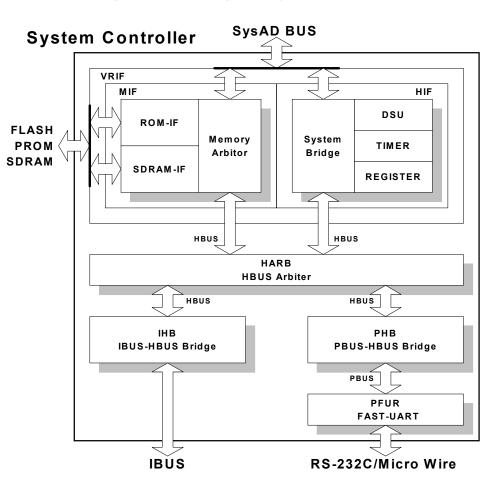

| 1-5. Block Diagram of System Controller            |                          |      |

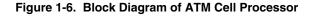

| 1-6. Block Diagram of ATM Cell Processor           |                          | 29   |

| 1-7. Block Diagram of Ethernet Controller          |                          |      |

| 1-8. Block Diagram of USB Controller               |                          |      |

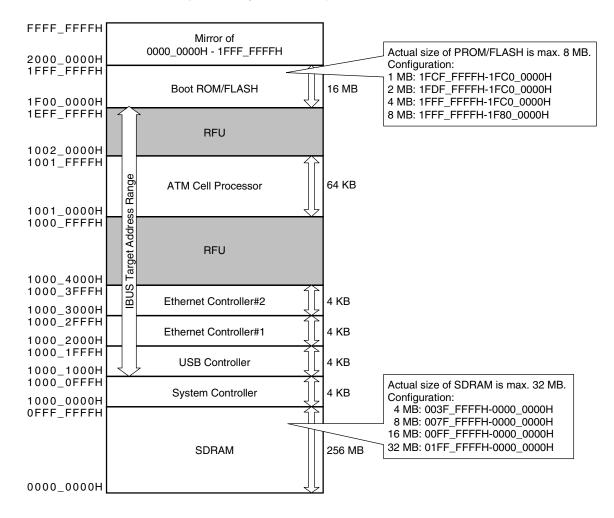

| 1-9. Memory Map                                    |                          | 48   |

| 1-10. Reset Configuration                          |                          | 49   |

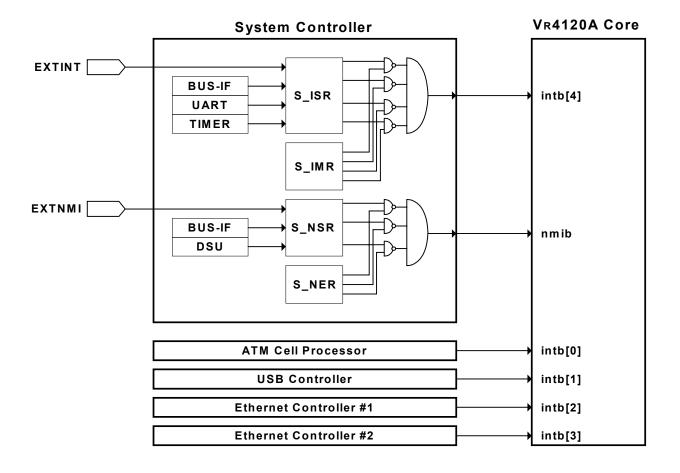

| 1-11. Interrupt Signal Connection                  |                          | 50   |

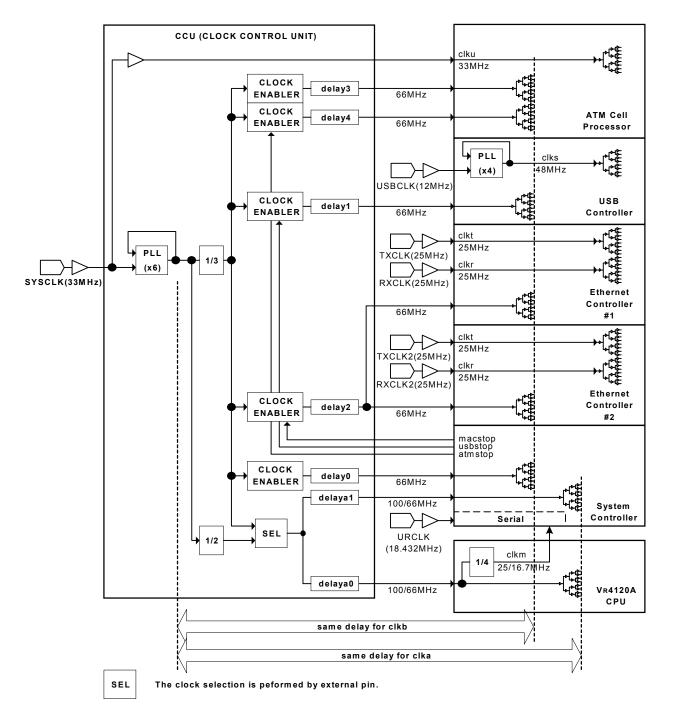

| 1-12. Block Diagram of Clock Control Unit          |                          | 51   |

| 2-1. VR4120A Core Internal Block Diagram           |                          | 52   |

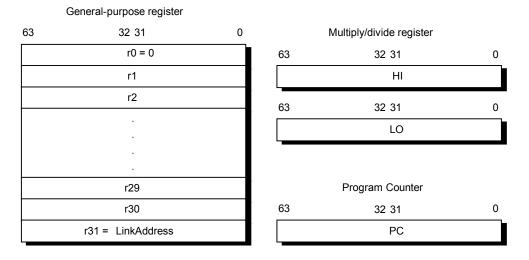

| 2-2. VR4120A Registers                             |                          | 54   |

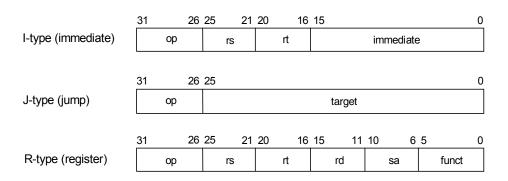

| 2-3. CPU Instruction Formats (32-bit Length Ins    | truction)                | 55   |

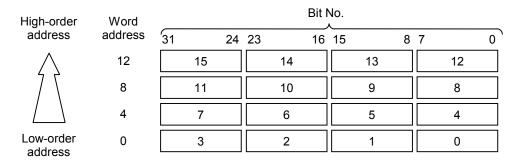

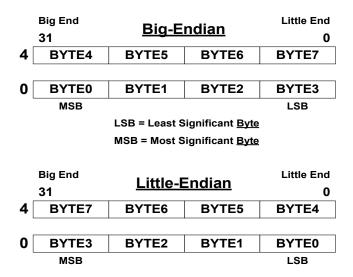

| 2-4. Little-Endian Byte Ordering in Word Data      |                          | 56   |

| 2-5. Little-Endian Byte Ordering in Double Word    | Data                     | 56   |

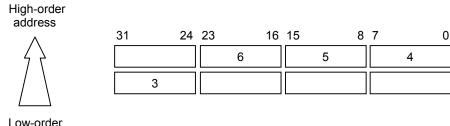

| 2-6. Misaligned Word Accessing (Little-Endian)     |                          | 57   |

| 2-7. CP0 Registers                                 |                          | 58   |

| 2-8. MIPS III ISA CPU Instruction Formats          |                          | 62   |

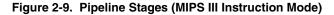

| 2-9. Pipeline Stages (MIPS III Instruction Mode)   | )                        | 80   |

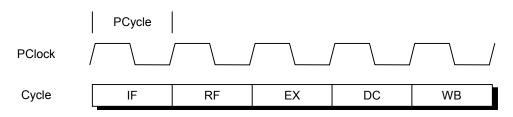

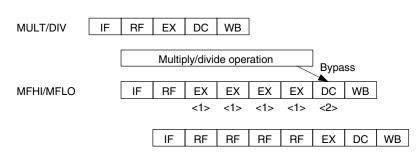

| 2-10. Instruction Execution in the Pipeline        |                          | 81   |

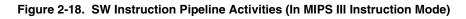

| 2-11. Pipeline Activities (MIPS III)               |                          | 82   |

| 2-12. Branch Delay (In MIPS III Instruction Mod    | e)                       | 83   |

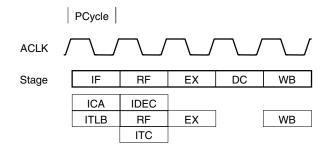

| 2-13. ADD Instruction Pipeline Activities (In MIP  | S III Instruction Mode)  | 84   |

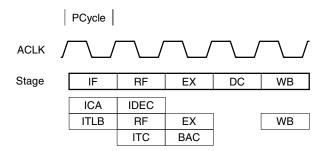

| 2-14. JALR Instruction Pipeline Activities (In MII | PS III Instruction Mode) | 85   |

| 2-15. BEQ Instruction Pipeline Activities (In MIP  | S III Instruction Mode)  | 86   |

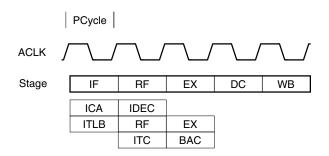

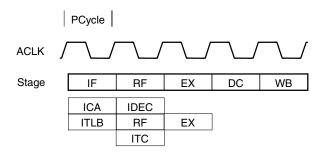

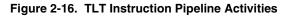

| 2-16. TLT Instruction Pipeline Activities          |                          | 87   |

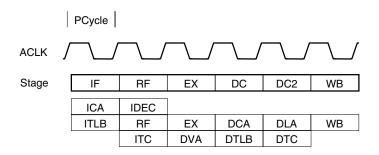

| 2-17. LW Instruction Pipeline Activities (In MIPS  | III Instruction Mode)    |      |

| 2-18. SW Instruction Pipeline Activities (In MIPS  | S III Instruction Mode)  |      |

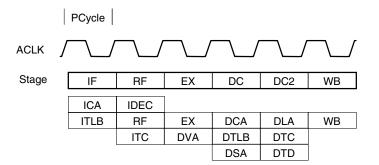

| 2-19. Relationship among Interlocks, Exception     | s, and Faults            | 90   |

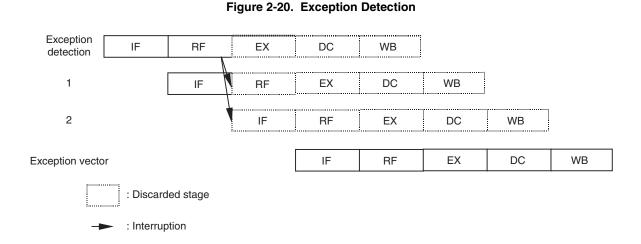

| 2-20. Exception Detection                          |                          | 92   |

| 2-21. Data Cache Miss Stall                        |                          | 93   |

| 2-22. CACHE Instruction Stall                      |                          | 93   |

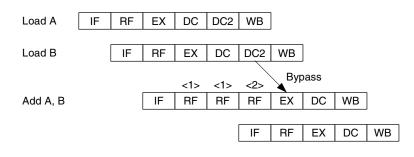

| 2-23. Load Data Interlock                          |                          | 94   |

| 2-24. MD Busy Interlock                            |                          | 95   |

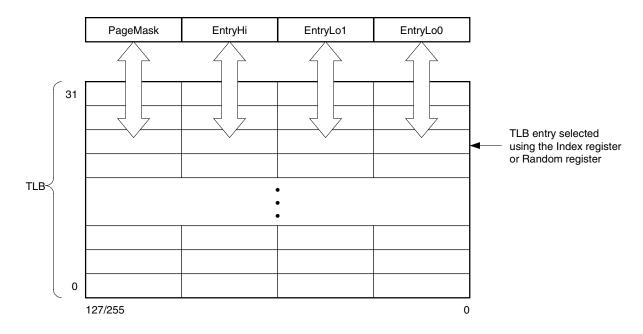

| 2-25. Format of TLB Entry                          |                          |      |

| 2-26. Outline of TLB Manipulation                  |                          |      |

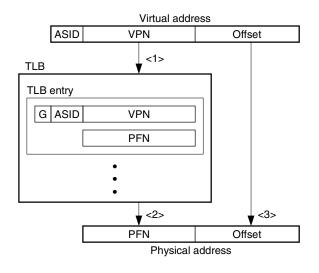

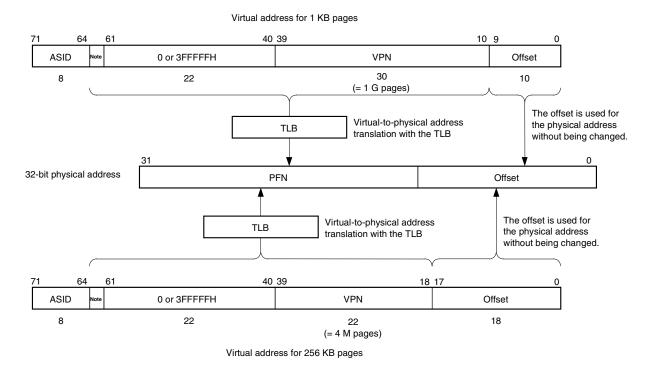

| 2-27. Virtual-to-Physical Address Translation      |                          | 101  |

| 2-28. TLB Address Translation                      |                          | 102  |

| 2-29. 32-bit Mode Virtual Address Translation      |                          | 103  |

## LIST OF FIGURES (2/5)

| Figur | e No.                                   | Title | Page |

|-------|-----------------------------------------|-------|------|

| 2-30. | 64-bit Mode Virtual Address Translation |       |      |

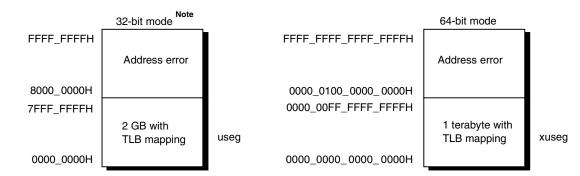

| 2-31. | User Mode Address Space                 |       |      |

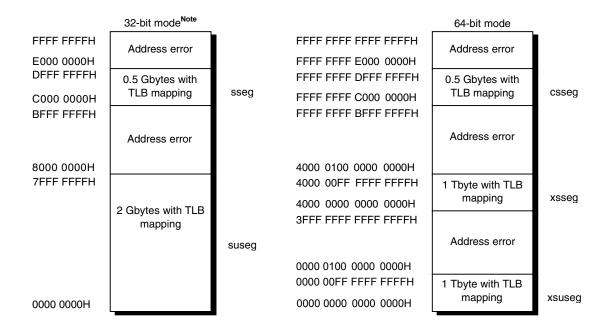

| 2-32. | Supervisor Mode Address Space           |       |      |

| 2-33. | Kernel Mode Address Space               |       |      |

| 2-34. | xkphys Area Address Space               |       |      |

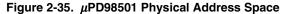

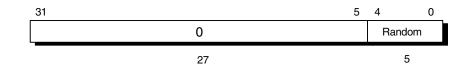

| 2-35. | µPD98501 Physical Address Space         |       |      |

| 2-36. | CP0 Registers and TLB                   |       |      |

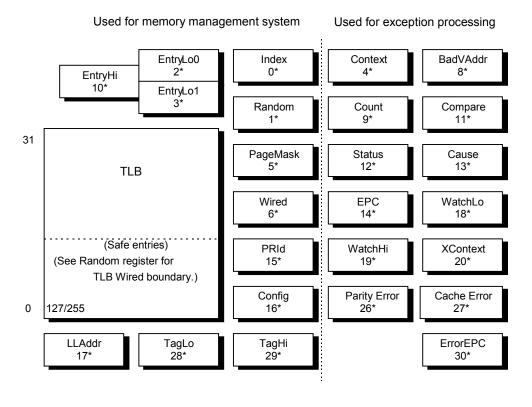

| 2-37. | Index Register                          |       |      |

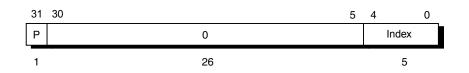

| 2-38. | Random Register                         |       |      |

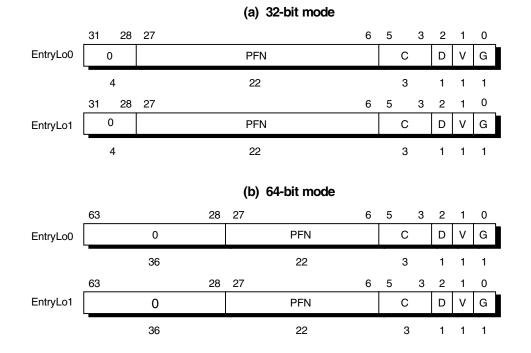

| 2-39. | EntryLo0 and EntryLo1 Registers         |       |      |

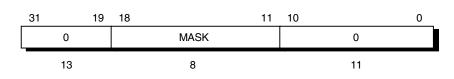

| 2-40. | Page Mask Register                      |       |      |

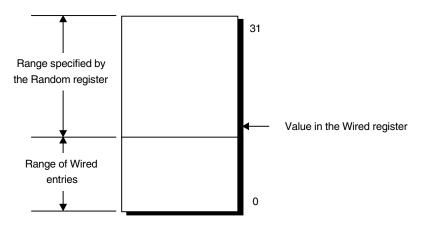

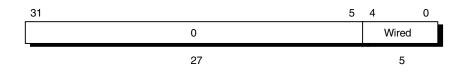

| 2-41. | Positions Indicated by Wired Register   |       |      |

| 2-42. | Wired Register                          |       |      |

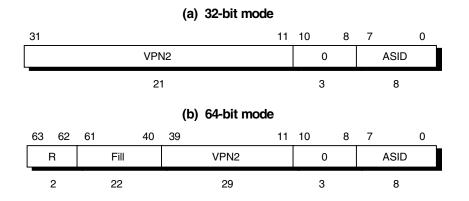

| 2-43. | EntryHi Register                        |       |      |

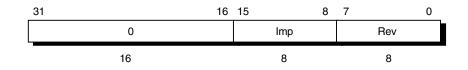

| 2-44. | PRId Register                           |       |      |

| 2-45. | Config Register Format                  |       |      |

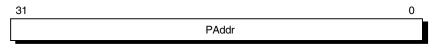

| 2-46. | LLAddr Register                         |       |      |

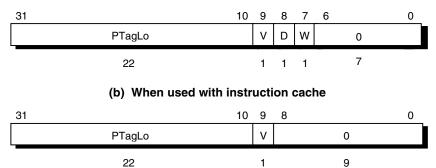

| 2-47. | TagLo Register                          |       |      |

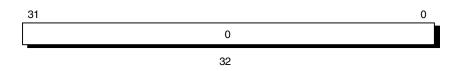

| 2-48. | TagHi Register                          |       |      |

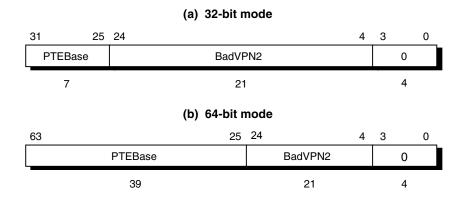

| 2-49. | Context Register Format                 |       |      |

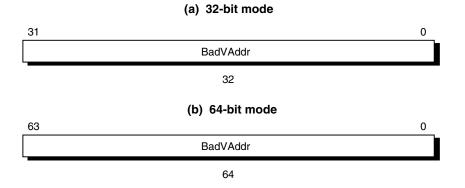

| 2-50. | BadVAddr Register Format                |       |      |

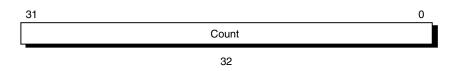

| 2-51. | Count Register Format                   |       |      |

| 2-52. | Compare Register Format                 |       |      |

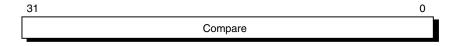

| 2-53. | Status Register Format                  |       |      |

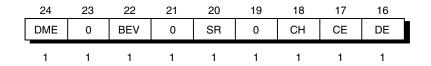

| 2-54. | Status Register Diagnostic Status Field |       |      |

| 2-55. | Cause Register Format                   |       |      |

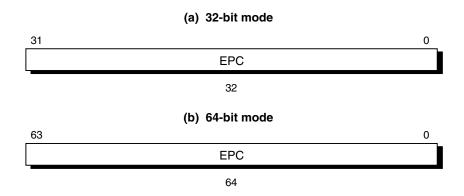

| 2-56. | EPC Register Format                     |       |      |

| 2-57. | WatchLo Register Format                 |       |      |

| 2-58. | WatchHi Register Format                 |       |      |

| 2-59. | XContext Register Format                |       |      |

| 2-60. | Parity Error Register Format            |       |      |

| 2-61. | Cache Error Register Format             |       |      |

| 2-62. | ErrorEPC Register Format                |       |      |

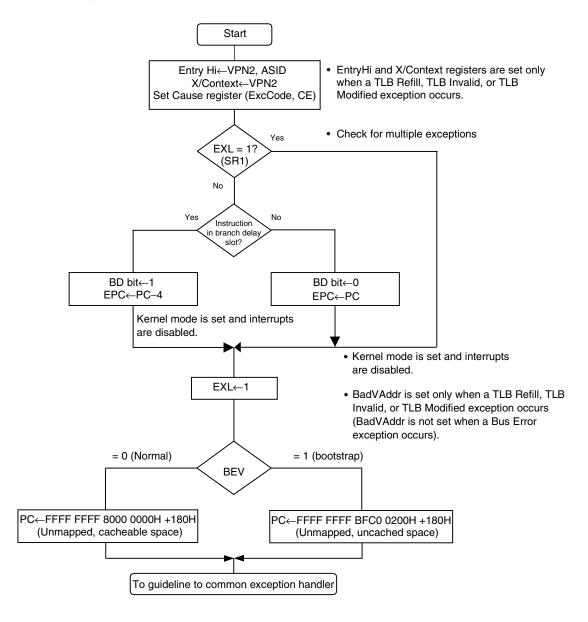

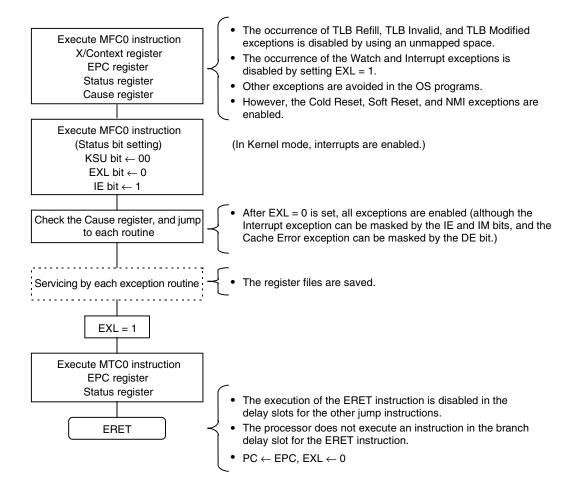

| 2-63. | Common Exception Handling               |       |      |

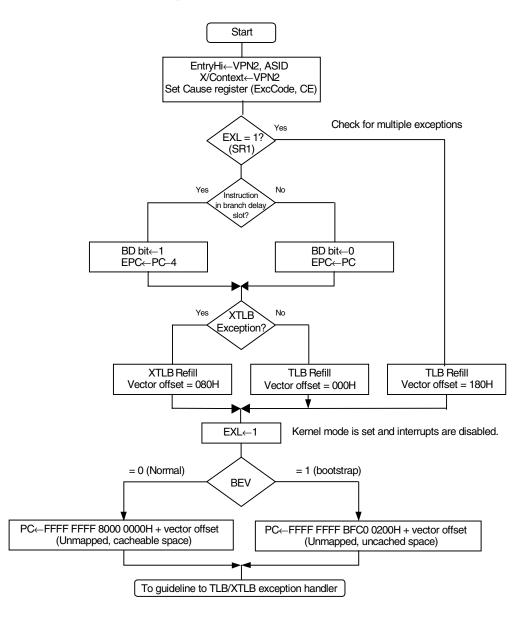

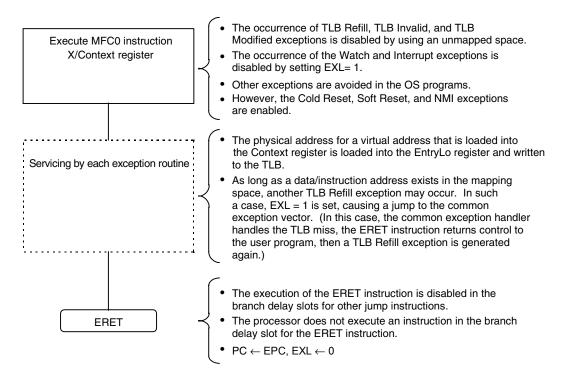

| 2-64. | TLB/XTLB Refill Exception Handling      |       |      |

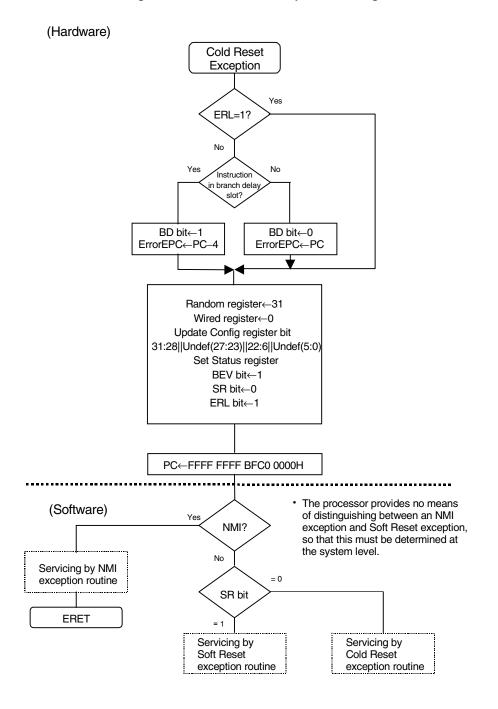

| 2-65. | Cold Reset Exception Handling           |       |      |

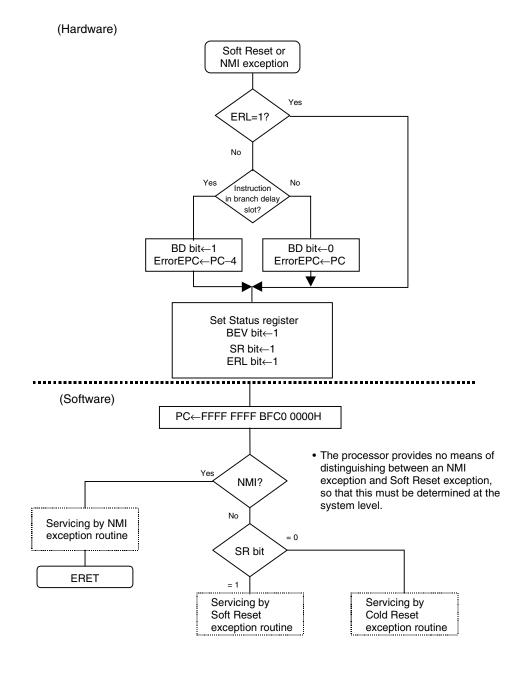

| 2-66. | Soft Reset and NMI Exception Handling   |       |      |

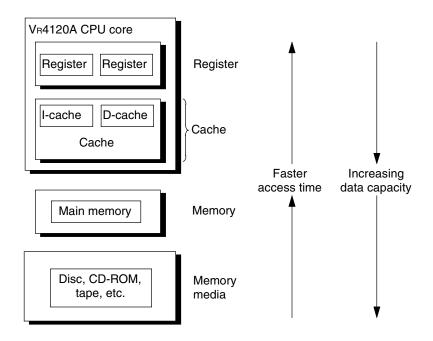

| 2-67. | Logical Hierarchy of Memory             |       |      |

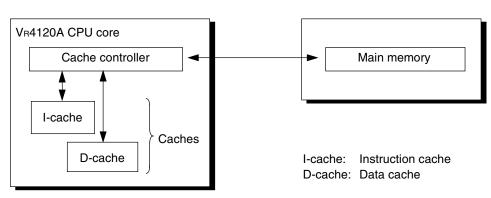

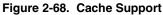

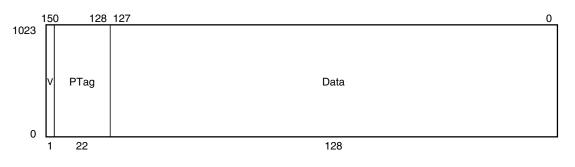

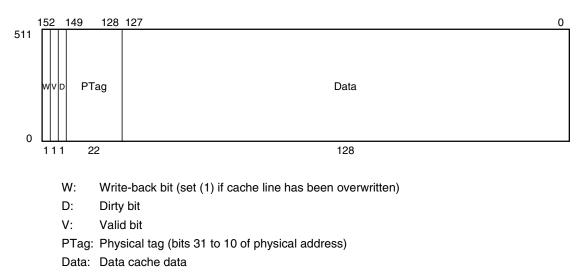

| 2-68. | Cache Support                           |       |      |

| 2-69. | Instruction Cache Line Format           |       |      |

| 2-70. | Data Cache Line Format                  |       |      |

| 2-71. | Cache Data and Tag Organization         |       |      |

## LIST OF FIGURES (3/5)

| Figure I | No. Title                                                | Page |

|----------|----------------------------------------------------------|------|

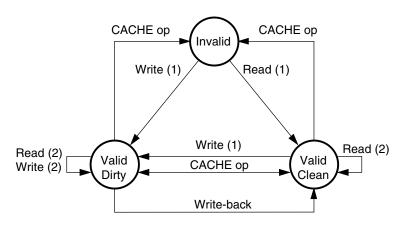

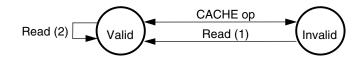

| 2-72. C  | Data Cache State Diagram                                 |      |

| 2-73. Ir | nstruction Cache State Diagram                           |      |

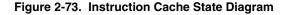

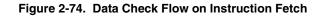

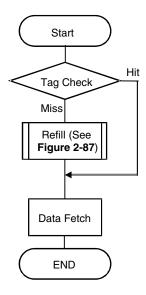

| 2-74. C  | Data Check Flow on Instruction Fetch                     |      |

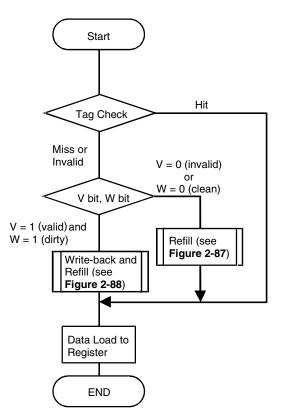

| 2-75. C  | Data Check Flow on Load Operations                       |      |

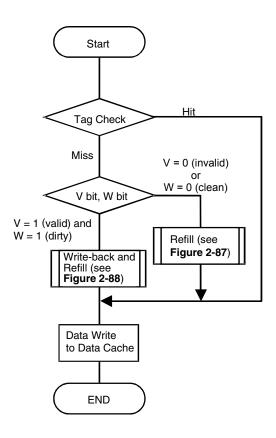

| 2-76. C  | Data Check Flow on Store Operations                      |      |

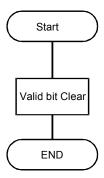

| 2-77. C  | Data Check Flow on Index_Invalidate Operations           |      |

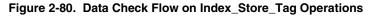

| 2-78. C  | Data Check Flow on Index_Writeback_Invalidate Operations |      |

| 2-79. C  | Data Check Flow on Index_Load_Tag Operations             |      |

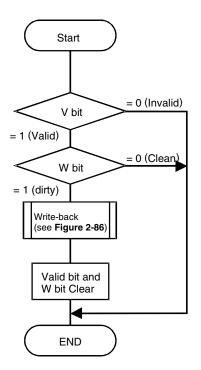

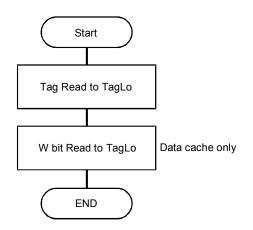

| 2-80. C  | Data Check Flow on Index_Store_Tag Operations            |      |

| 2-81. C  | Data Check Flow on Create_Dirty Operations               |      |

| 2-82. C  | Data Check Flow on Hit_Invalidate Operations             |      |

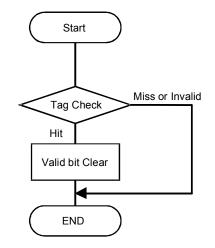

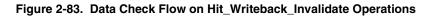

| 2-83. C  | Data Check Flow on Hit_Writeback_Invalidate Operations   |      |

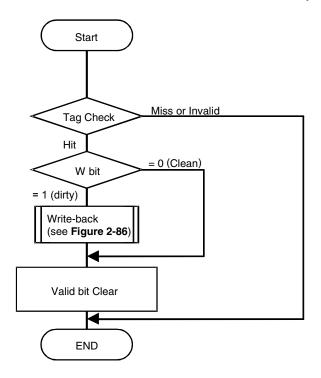

| 2-84. C  | Data Check Flow on Fill Operations                       |      |

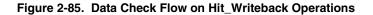

| 2-85. C  | Data Check Flow on Hit_Writeback Operations              |      |

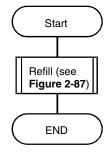

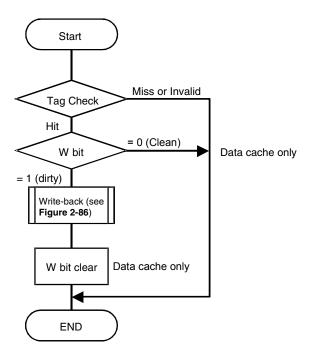

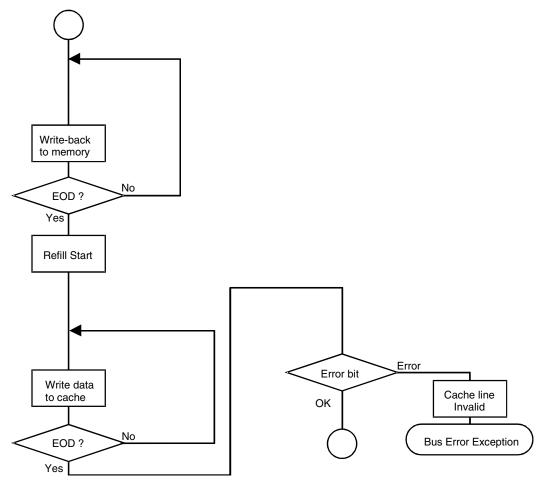

| 2-86. V  | Vriteback Flow                                           |      |

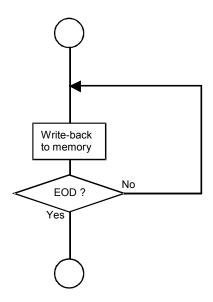

| 2-87. F  | Refill Flow                                              |      |

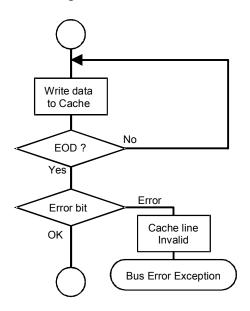

| 2-88. V  | Vriteback & Refill Flow                                  |      |

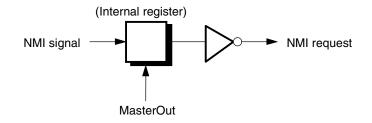

| 2-89. N  | Ion-maskable Interrupt Signal                            |      |

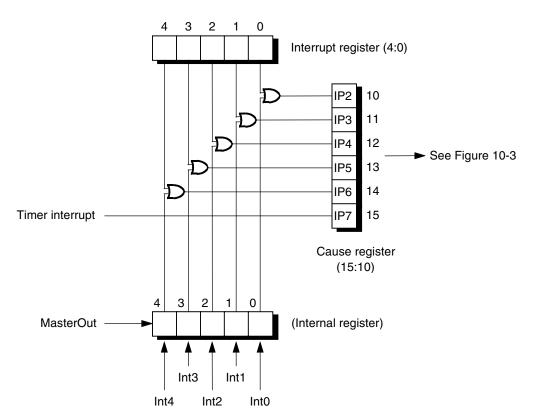

| 2-90. ⊦  | lardware Interrupt Signals                               |      |

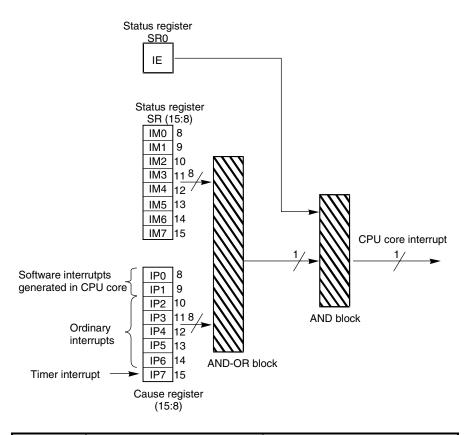

| 2-91. N  | lasking of Interrupt Request Signals                     |      |

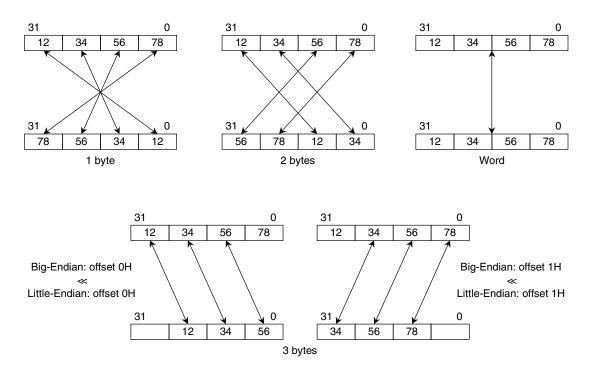

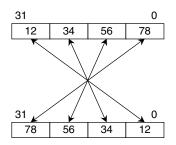

| 3-1. En  | idian Translation for the Data Swap Mode (Master)        |      |

|          | Idian Translation for the Data Swap Mode (Slave)         |      |

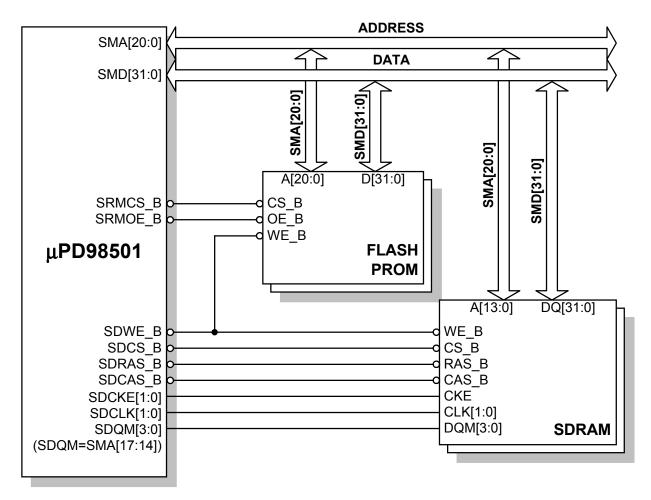

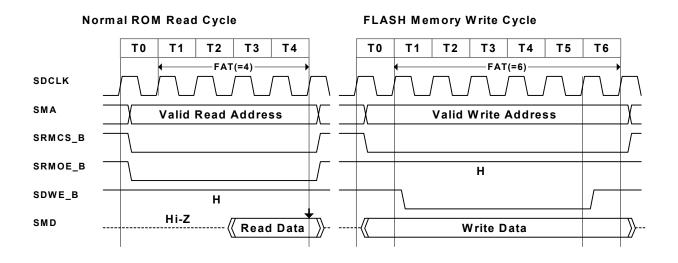

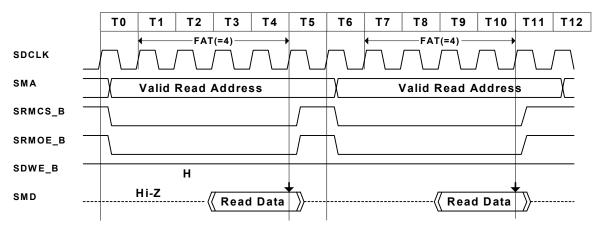

|          | M/ FLASH Memory Read/Write Cycle                         |      |

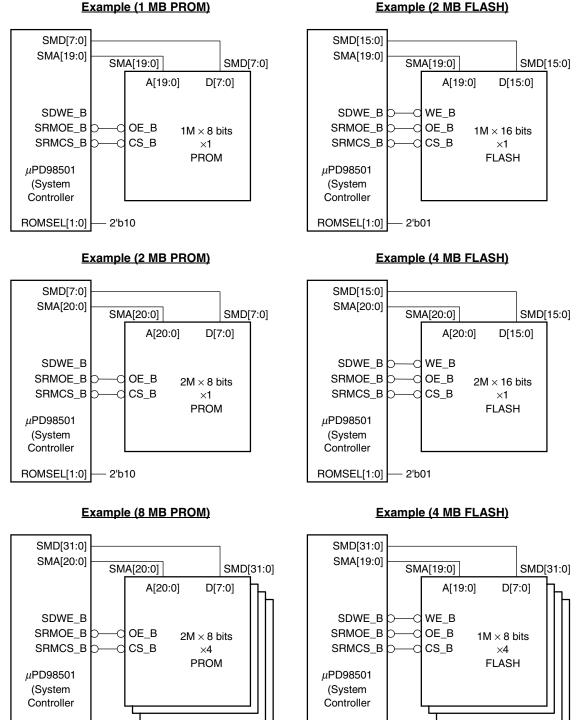

|          | ASH/ROM Configuration                                    |      |

|          | DRAM Configuration                                       |      |

|          | and Byte Order of Endian Modes                           |      |

|          | alfword Data-Array Example                               |      |

|          | ord Data-Array Example                                   |      |

| ∕I-1 Bk  | ock Diagram of ATM Cell Processor                        | 228  |

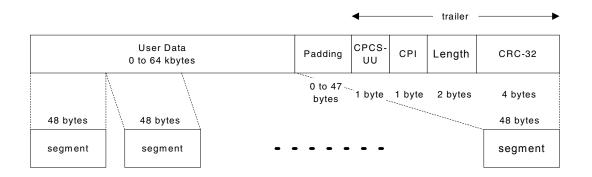

|          | AL-5 Sublayer and ATM Layer                              |      |

|          | AL-5 Sublayer and ATM Layer                              |      |

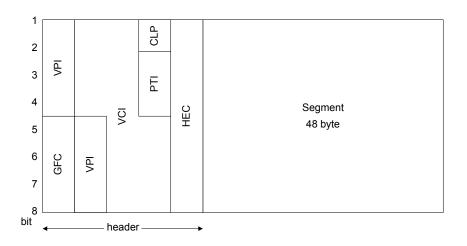

|          | The Cell                                                 |      |

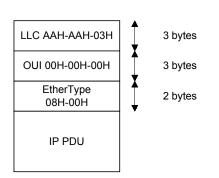

|          | C Encapsulation                                          |      |

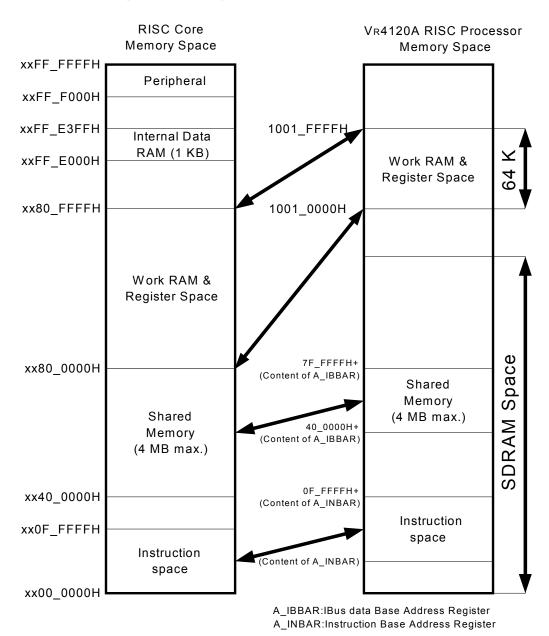

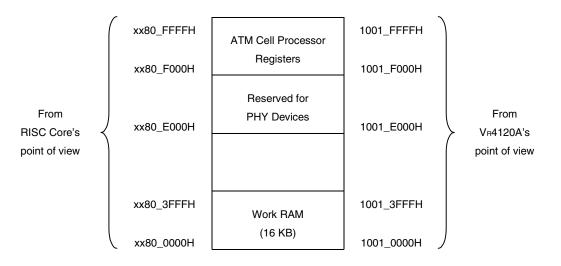

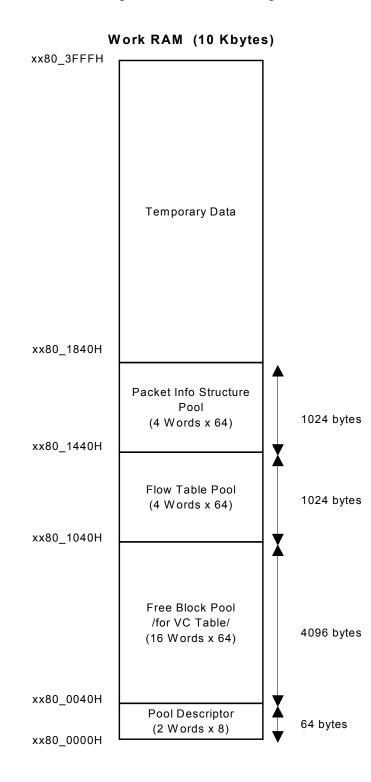

|          | emory Space from V <sub>R</sub> 4120A and RISC Core      |      |

|          | ork RAM and Register Space                               |      |

|          | Packet                                                   |      |

|          | Buffer Elements                                          |      |

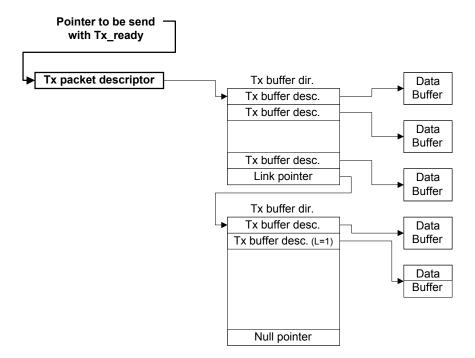

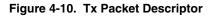

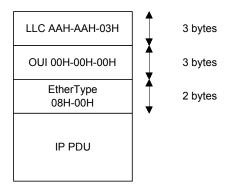

|          | x Packet Descriptor                                      |      |

|          | x Packet Descriptor<br>x Buffer Descriptor/Link Pointer  |      |

|          |                                                          |      |

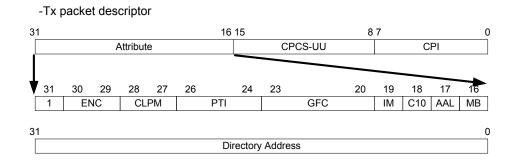

| 4-12. F  |                                                          | 249  |

## LIST OF FIGURES (4/5)

| Figu | re No.                                          | Title                                 | Page |

|------|-------------------------------------------------|---------------------------------------|------|

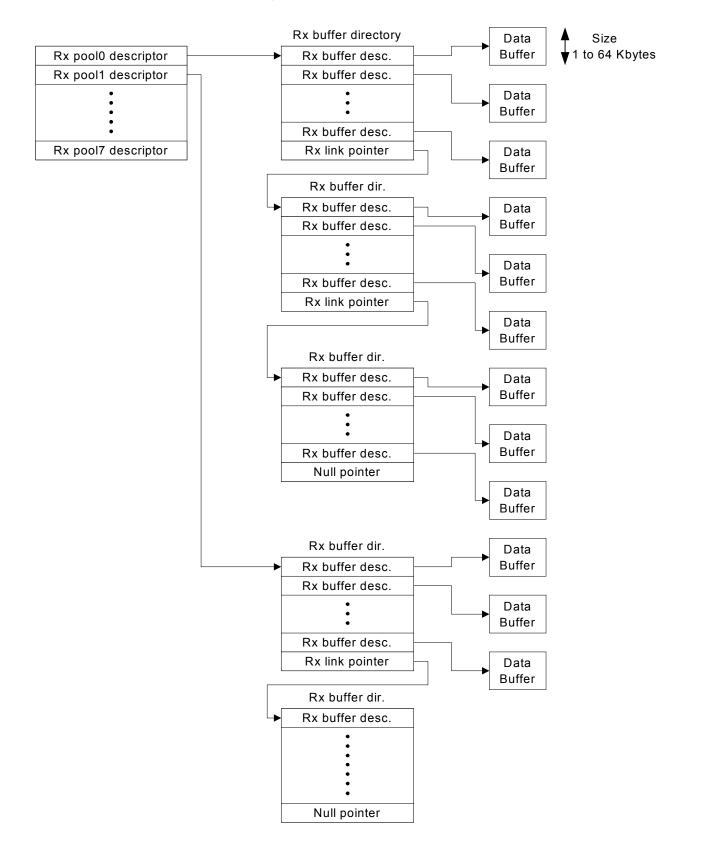

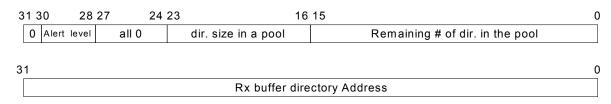

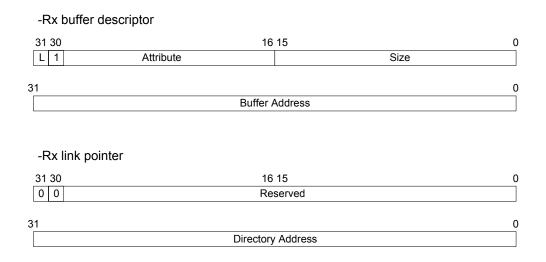

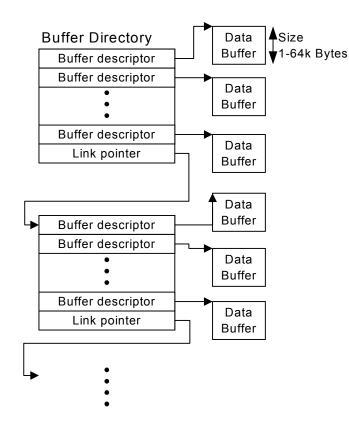

| 4-13 | Rx Pool Descriptor/Rx Buffer Directory/Rx Buffe | r Descriptor/Rx Link Pointer          | 250  |

| 4-14 | Rx Pool Descriptor                              | · · · · · · · · · · · · · · · · · · · | 251  |

| 4-15 | Rx Buffer Descriptor/ Link Pointer              |                                       | 252  |

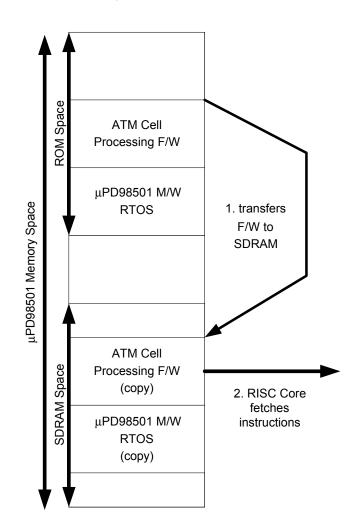

|      | Transfer of F/W                                 |                                       |      |

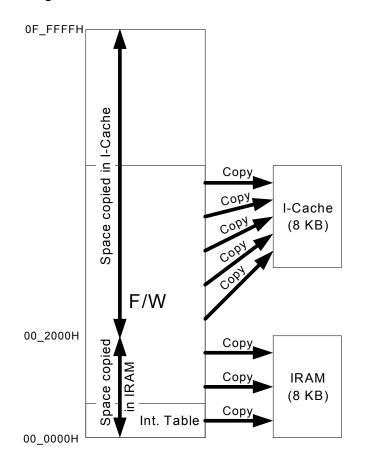

| 4-17 | Instruction RAM and Instruction Cache           |                                       | 254  |

| 4-18 | Set_Link_Rate Command                           |                                       | 256  |

| 4-19 | Open_Channel Command and Indication             |                                       | 256  |

| 4-20 | Close_Channel Command and Indication            |                                       | 257  |

| 4-21 | Tx_Ready Command and Indication                 |                                       | 258  |

| 4-22 | Add_Buffers Command                             |                                       | 259  |

| 4-23 | Indirect_Access Command                         |                                       |      |

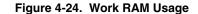

| 4-24 | Work RAM Usage                                  |                                       | 261  |

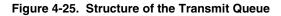

| 4-25 | Structure of the Transmit Queue                 |                                       |      |

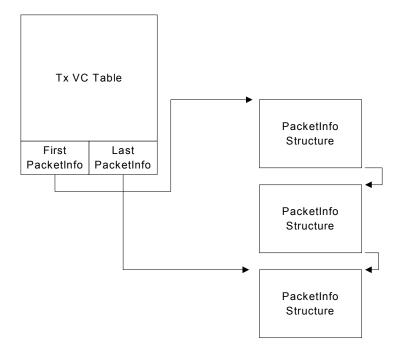

| 4-26 | Packet Info Structure                           |                                       |      |

| 4-27 | Transmit Queue Packet Descriptor                |                                       |      |

| 4-28 | Tx VC Table                                     |                                       |      |

| 4-29 | Raw Cell with CRC-10                            |                                       |      |

| 4-30 | Send Indication Format                          |                                       |      |

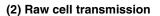

| 4-31 | LLC Encapsulation Format                        |                                       |      |

| 4-32 | Receive VC Table                                |                                       |      |

| 4-33 | Raw Cell Data Format                            |                                       | 271  |

| 4-34 | Receive Indication Format                       |                                       | 272  |

| 4-35 | Mailbox Structure                               |                                       | 274  |

|      |                                                 |                                       |      |

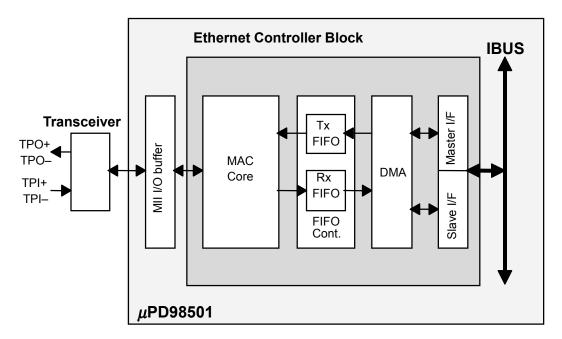

|      | Block Diagram of Ethernet Controller            |                                       |      |

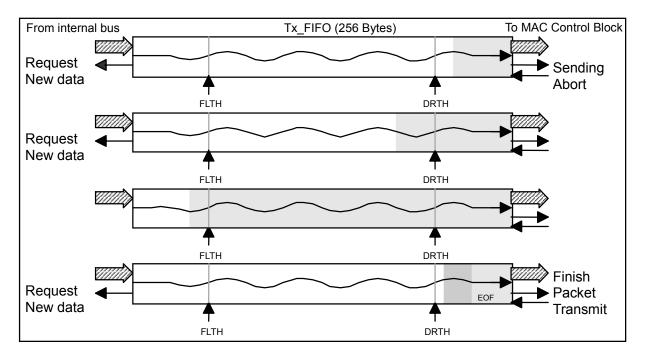

|      | Tx FIFO Control Mechanism                       |                                       |      |

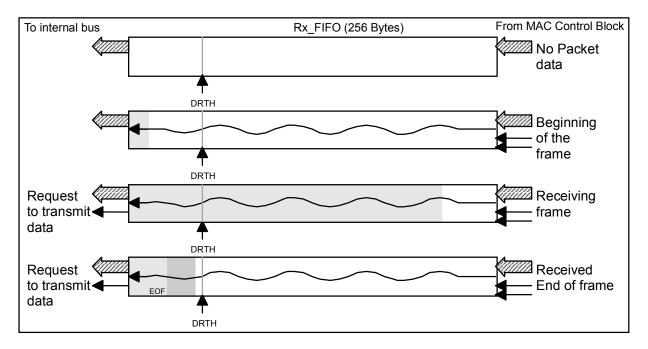

| 5-3. | Rx FIFO Control Mechanism                       |                                       |      |

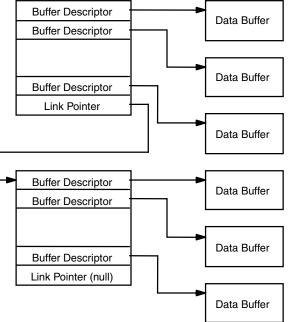

|      | Buffer Structure for Ethernet Block             |                                       |      |

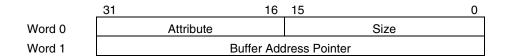

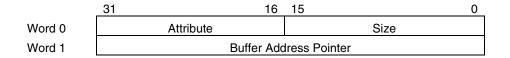

|      | Transmit Descriptor Format                      |                                       |      |

|      | Receive Descriptor Format                       |                                       |      |

|      | Transmit Procedure                              |                                       |      |

| 5-8. | Receive Procedure                               |                                       |      |

| 6-1. | USB Controller Internal Configuration           |                                       | 308  |

|      | USB Attachment Sequence                         |                                       |      |

|      | Mailbox Configuration                           |                                       |      |

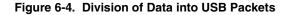

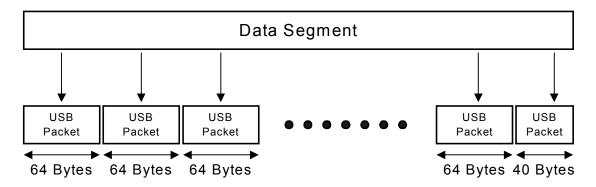

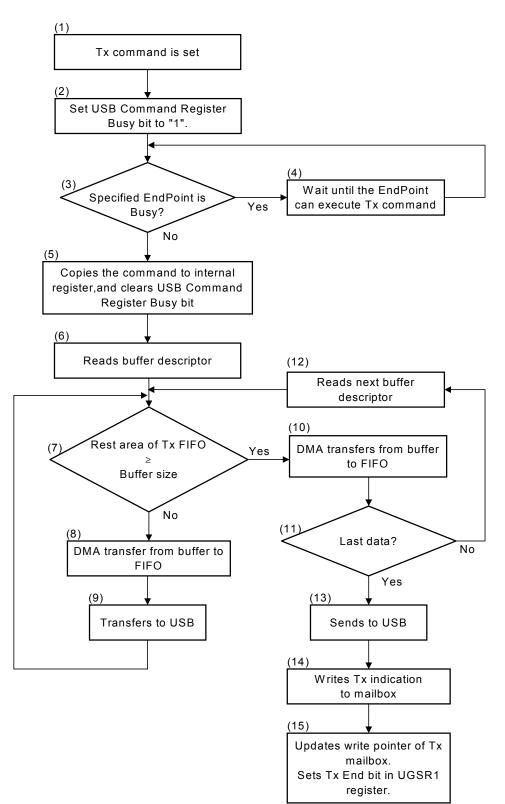

|      | Division of Data into USB Packets               |                                       |      |

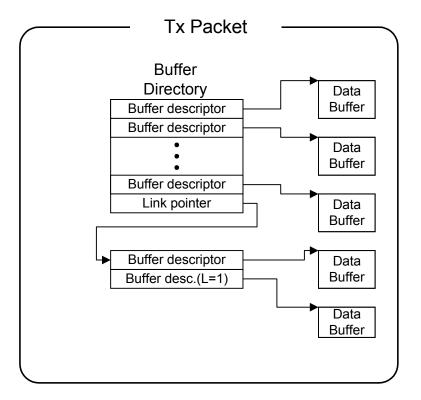

|      | Tx Buffer Configuration                         |                                       |      |

|      | Configuration of Transmit Buffer Directory      |                                       |      |

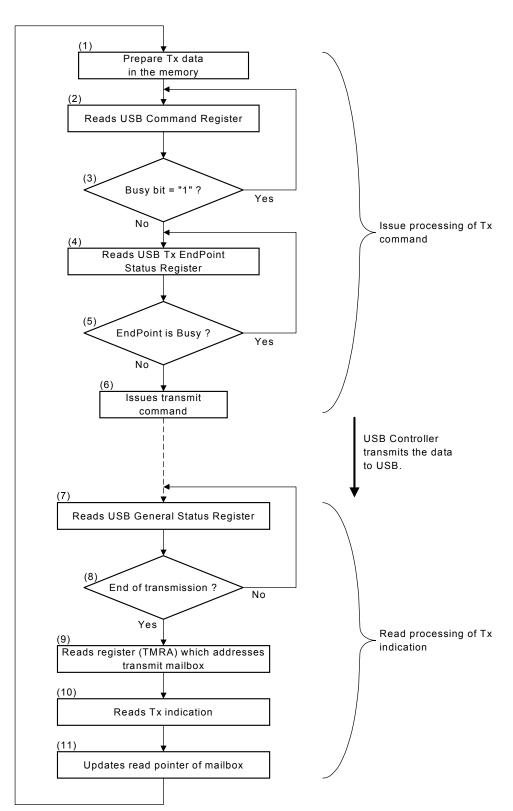

|      | VR4120A Processing at Data Transmitting         |                                       |      |

|      | Transmit Command Issue                          |                                       |      |

|      | Transmit Status Register                        |                                       |      |

|      |                                                 |                                       | 500  |

Page

### LIST OF FIGURES (5/5)

Title

| 6-10. | USB Controller Transmit Operation Flow Chart              | 339 |

|-------|-----------------------------------------------------------|-----|

| 6-11. | Transmit Indication Format                                | 341 |

| 6-12. | Division of Data into USB Packets                         | 342 |

| 6-13. | Receive Buffer Configuration                              | 343 |

| 6-14. | Receive Descriptor Configuration                          | 344 |

| 6-15. | Buffer Directory Addition Command                         | 345 |

| 6-16. | Data Receiving in EndPoint0, EndPoint6                    | 347 |

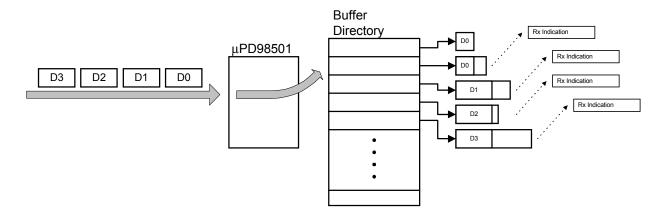

| 6-17. | EndPoint2, EndPoint4 Receive Normal Mode                  | 347 |

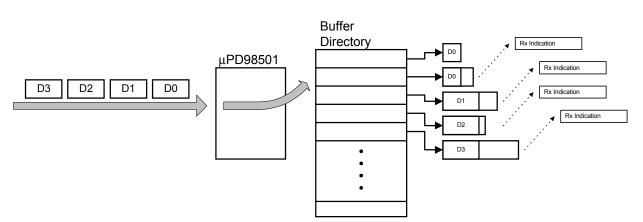

| 6-18. | EndPoint2, EndPoint4 Receive Assemble Mode                | 348 |

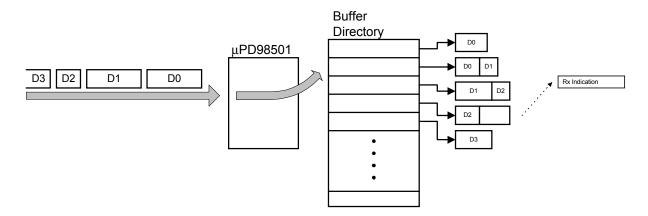

| 6-19. | EndPoint2, EndPoint4 Receive Separate Mode                | 348 |

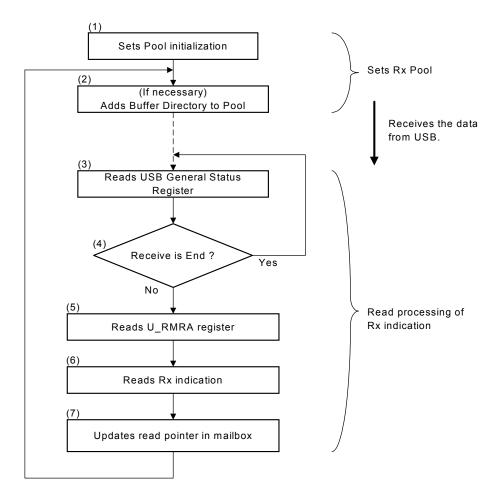

| 6-20. | VR4120A Receive Processing                                | 349 |

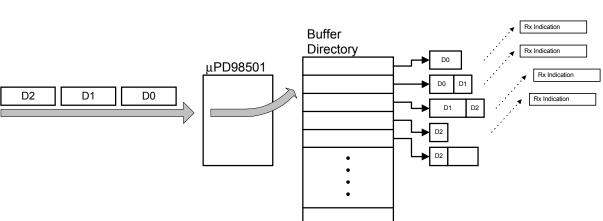

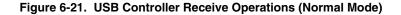

| 6-21. | USB Controller Receive Operations (Normal Mode)           | 350 |

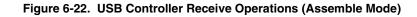

| 6-22. | USB Controller Receive Operations (Assemble Mode)         | 352 |

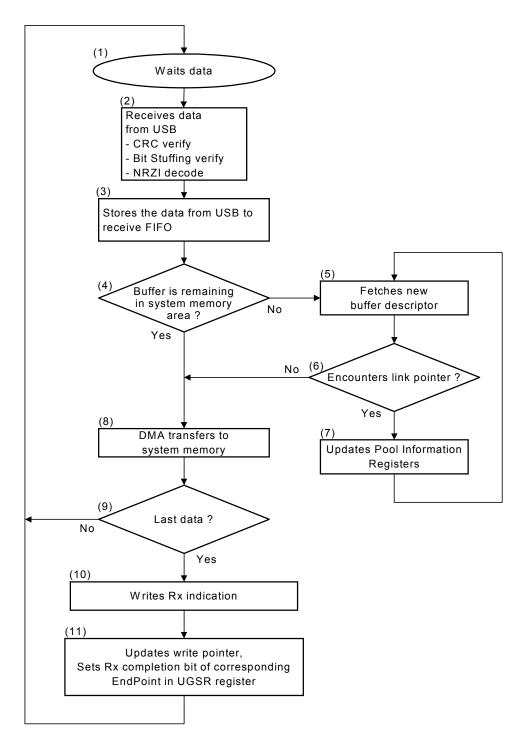

| 6-23. | USB Controller Receive Operation Sequence (Separate Mode) | 354 |

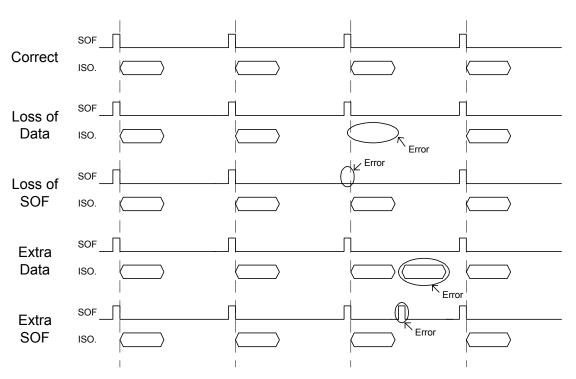

| 6-24. | USB Timing Errors                                         | 356 |

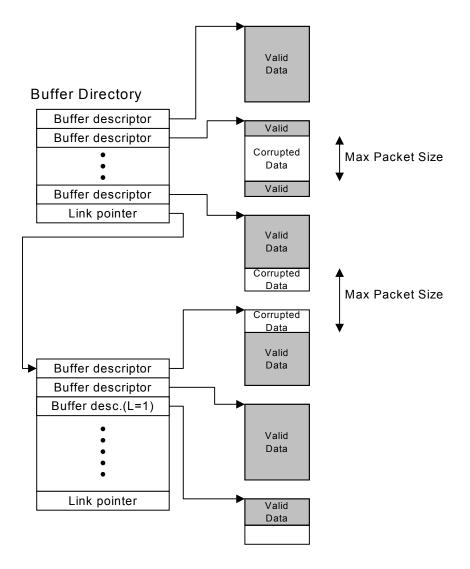

| 6-25. | Example of Buffers Including Corrupted Data               | 359 |

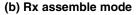

| 6-26. | Receive Indication Format                                 |     |

| 6-27. | Suspend Sequence                                          |     |

| 6-28. | Resume Sequence                                           |     |

Figure No.

## LIST OF TABLES (1/2)

| Tab  | le No. Title                                                              | Page |

|------|---------------------------------------------------------------------------|------|

| 2-1. | System Control Coprocessor (CP0) Register Definitions                     |      |

|      | Number of Delay Slot Cycles Necessary for Load and Store Instructions     |      |

|      | Byte Specification Related to Load and Store Instructions                 |      |

|      | Load/Store Instruction                                                    |      |

|      | Load/Store Instruction (Extended ISA)                                     |      |

| 2-6. | ALU Immediate Instruction                                                 | 67   |

| 2-7. | ALU Immediate Instruction (Extended ISA)                                  |      |

| 2-8. | Three-Operand Type Instruction                                            | 68   |

| 2-9. | Three-Operand Type Instruction (Extended ISA)                             |      |

| 2-10 | ). Shift Instruction                                                      |      |

| 2-11 | . Shift Instruction (Extended ISA)                                        | 70   |

| 2-12 | 2. Multiply/Divide Instructions                                           | 71   |

| 2-13 | <ol> <li>Multiply/Divide Instructions (Extended ISA)</li> </ol>           | 72   |

| 2-14 | Number of Stall Cycles in Multiply and Divide Instructions                | 73   |

| 2-15 | Number of Delay Slot Cycles in Jump and Branch Instructions               | 73   |

| 2-16 | 3. Jump Instruction                                                       | 74   |

| 2-17 | 2. Branch Instructions                                                    | 75   |

| 2-18 | B. Branch Instructions (Extended ISA)                                     | 76   |

| 2-19 | ). Special Instructions                                                   | 77   |

| 2-20 | ). Special Instructions (Extended ISA)                                    | 77   |

| 2-21 | . System Control Coprocessor (CP0) Instructions                           | 78   |

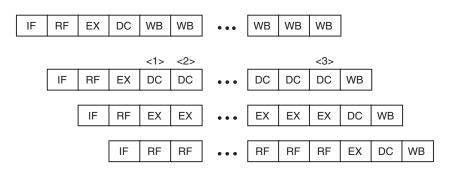

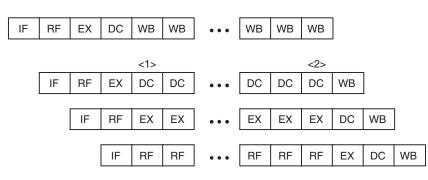

| 2-22 | 2. Operation in Each Stage of Pipeline (MIPS III)                         | 82   |

| 2-23 | 8. Correspondence of Pipeline Stage to Interlock and Exception Conditions | 90   |

| 2-24 | Pipeline Interlock                                                        | 91   |

| 2-25 | i. Description of Pipeline Exception                                      | 91   |

| 2-26 | 6. VR Series Supported Instructions                                       | 96   |

| 2-27 | '. User Mode Segments                                                     |      |

| 2-28 | 3. 32-bit and 64-bit Supervisor Mode Segments                             |      |

| 2-29 | 0. 32-bit Kernel Mode Segments                                            | 112  |

| 2-30 | 0. 64-bit Kernel Mode Segments                                            | 113  |

| 2-31 | . Cacheability and xkphys Address Space                                   | 114  |

| 2-32 | 2. CP0 Memory Management Registers                                        | 118  |

| 2-33 | B. Cache Algorithm                                                        | 121  |

| 2-34 | . Mask Values and Page Sizes                                              | 121  |

| 2-35 | 5. CP0 Exception Processing Registers                                     | 129  |

|      | 6. Cause Register Exception Code Field                                    |      |

| 2-37 | 7. 64-Bit Mode Exception Vector Base Addresses                            | 141  |

| 2-38 | 32-Bit Mode Exception Vector Base Addresses                               | 142  |

| 2-39 | 9. Exception Priority Order                                               | 143  |

| 0 1  | For the extension Table for the Date Ower Mark (Mark)                     |      |

|      | Endian Translation Table for the Data Swap Mode (Master)                  |      |

| 3-2. | Endian Translation Table for the Data Swap Mode (Slave)                   |      |

## LIST OF TABLES (2/2)

| Tabl | e No. Title                                                           | Page |

|------|-----------------------------------------------------------------------|------|

| 3-3. | Endian Configuration Table                                            |      |

| 3-4. | Endian Translation Table in Endian Converter (1)                      |      |

|      | Endian Translation Table in Endian Converter (2)                      |      |

| 3-6. | External Pin Mapping                                                  |      |

| 3-7. | Examples of Memory Performance (4 word-burst access from CPU)         |      |

| 3-8. | Examples of Memory Performance (4 word-burst access from IBUS Master) |      |

| 3-9. | Boot-ROM Size Configuration at Reset                                  |      |

| 3-10 | . Relationship between Memory Map and Address Bus                     |      |

| 3-11 | . Available Write Access Type                                         | 213  |

| 3-12 | 2. Command Sequence                                                   | 214  |

| 3-13 | B. SDRAM Size Configuration at Reset                                  | 216  |

| 3-14 | SDRAM Configurations Supported                                        |      |

| 3-15 | 5. SDRAM Bank Select Signals Mapping                                  | 217  |

| 3-16 | 5. SDRAM Word Order for Instruction-Cache Line-Fill                   | 217  |

| 4-1. | List of Tx Packet Attribute                                           | 247  |

| 4-2. | List of Rx Pool Attributes                                            | 251  |

| 4-3. | Commands                                                              |      |

| 4-4. | Reception Errors That Can Occur During Packet Reception               |      |

| 4-5. | Error Reporting Priorities                                            | 273  |

| 5-1. | Ethernet Controller's Register Categories                             |      |

| 5-2. | MAC Control Register Map                                              | 277  |

| 5-3. | Statistics Counter Register Map                                       | 279  |

| 5-4. | DMA and FIFO Management Registers Map                                 |      |

| 5-5. | Interrupt and Configuration Registers Map                             |      |

| 5-6. | Attribute for Transmit Descriptor                                     |      |

| 5-7. | Attribute for Receive Descriptor                                      |      |

| 7-1. | Correspondence between Baud Rates and Divisors                        |      |

| 9-1. | EEPROM Initial Data                                                   |      |

| 9-2. | EEPROM Command List                                                   |      |