### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# JUSER'S MANUAL

$\mu$ PD30101

VR4000, VR4100, VR4101, VR4200, VR4400, and VR-Series are trademarks of NEC Corporation.

R4000 is a trademark of MIPS Computer Systems, Inc.

MIPS is a trademark of MIPS Technologies, Inc.

iAPX is a trademark of Intel Corp.

DEC VAX is a trademark of Digital Equipment Corp.

UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company, Ltd.

Exporting this product or equipment that includes this product may require a governmental license from the U.S.A. for some countries because this product utilizes technologies limited by the export control regulations of the U.S.A.

### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

#### NOTES FOR CMOS DEVICES -

### **D** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### ② HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

### 3 STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

### **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- · Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- · Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 800-366-9782 Fax: 800-729-9288

### NEC Electronics (Germany) GmbH

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

#### **NEC Electronics (UK) Ltd.**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics Italiana s.r.1.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

### NEC Electronics (Germany) GmbH

Benelux Office Eindhoven, The Netherlands

Tel: 040-2445845 Fax: 040-2444580

### NEC Electronics (France) S.A.

Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

### **NEC Electronics (France) S.A.**

Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

#### **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

### NEC Electronics Singapore Pte. Ltd.

United Square, Singapore 1130

Tel: 253-8311 Fax: 250-3583

### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-719-2377 Fax: 02-719-5951

### **NEC do Brasil S.A.**

Sao Paulo-SP, Brasil Tel: 011-889-1680 Fax: 011-889-1689

### **PREFACE**

Readers This manual targets users who intends to understand the functions of the VR4101

and to design application systems using this microprocessor.

Purpose This manual introduces the architecture and hardware functions of the VR4101 to

users, following the organization described below.

Organization This manual consists of the following contents:

Introduction

- · Pipeline operation

- · Cache organization and memory management system

- · Exception processing

- Initialization interface

- Interrupts

- · Peripheral units

- Instruction set details

How to read this manual It

It is assumed that the reader of this manual has general knowledge in the fields of electric engineering, logic circuits, and microcomputers.

The VR4000<sup>TM</sup> in this manual includes the VR4400<sup>TM</sup>.

To learn about detailed function of a specific instruction,

-> Read Chapter 2 CPU Instruction Set Summary and Chapter 24 CPU Instruction Set Details.

To learn about the overall functions of the VR4101,

-> Read this manual in sequential order.

To learn about electrical specifications,

-> Refer to Data Sheet which is separately available.

Legend Data significance: Higher on left and lower on right

Active low: XXX\* (trailing asterisk after pin and signal names)

Numeric representation: binary ... XXXX or XXXX2

decimal ... XXXX

hexadecimal ... 0xXXXX

Prefixes representing an exponent of 2 (for address space or memory capacity):

K (kilo)  $2^{10} = 1024$ M (mega)  $2^{20} = 1024^2$ G (giga)  $2^{30} = 1024^3$

T (tera)  $2^{40} = 1024^4$ P (peta)  $2^{50} = 1024^5$

P (peta)  $2^{50} = 1024^5$ E (exa)  $2^{60} = 1024^6$

### **Related Documents**

The related documents indicated here may include preliminary version. However, preliminary versions are not marked as such.

• User's manual

VR4101 User's ManualThis manual VR4100<sup>TM</sup> User's Manual U10050E

Data sheet

VR4101

Data Sheet

U11846E

VR4100

Data Sheet

U10428E

Application note

VR4101 Application Note To be issued

### **SUMMARY OF CONTENTS**

| CHAPTER 1  | INTRODUCTION                           | 1    |

|------------|----------------------------------------|------|

| CHAPTER 2  | CPU INSTRUCTION SET SUMMARY            | 23   |

| CHAPTER 3  | VR4101 PIPELINE                        | 35   |

| CHAPTER 4  | MEMORY MANAGEMENT SYSTEM               | 53   |

| CHAPTER 5  | EXCEPTION PROCESSING                   | 85   |

| CHAPTER 6  | PIN FUNCTIONS                          | 123  |

| CHAPTER 7  | INITIALIZATION INTERFACE               | 135  |

| CHAPTER 8  | CACHE ORGANIZATION AND OPERATION       | 147  |

| CHAPTER 9  | CPU CORE INTERRUPTS                    | 165  |

| CHAPTER 10 | BCU (BUS CONTROL UNIT)                 | 169  |

| CHAPTER 11 | DMAAU (DMA ADDRESS UNIT)               | 203  |

| CHAPTER 12 | DCU (DMA CONTROL UNIT)                 | 211  |

| CHAPTER 13 | CMU (CLOCK MASK UNIT)                  | .217 |

| CHAPTER 14 | ICU (INTERRUPT CONTROL UNIT)           | 221  |

| CHAPTER 15 | PMU (POWER MANAGEMENT UNIT)            | 243  |

| CHAPTER 16 | RTC (REALTIME CLOCK UNIT)              | 255  |

| CHAPTER 17 | DSU (DEADMAN'S SW UNIT)                | 267  |

| CHAPTER 18 | GIU (GENERAL PURPOSE I/O UNIT)         | 273  |

| CHAPTER 19 | PIU (TOUCH PANEL INTERFACE UNIT)       | 283  |

| CHAPTER 20 | SIU (SERIAL INTERFACE UNIT)            | 307  |

| CHAPTER 21 | AIU (AUDIO INTERFACE UNIT)             | 327  |

| CHAPTER 22 | KIU (KEYBOARD INTERFACE UNIT)          | 349  |

| CHAPTER 23 | DEBUGSIU (DEBUG SERIAL INTERFACE UNIT) | 373  |

| CHAPTER 24 | CPU INSTRUCTION SET DETAILS            | 385  |

| CHAPTER 25 | Vr4101 COPROCESSOR 0 HAZARDS           | 537  |

| CHAPTER 26 | PLL PASSIVE COMPONENTS                 | 543  |

| APPENDIX   | INDEX                                  | 545  |

### [MEMO]

### **TABLE OF CONTENTS**

| CHAPTE | R 1   | INTRODUCTION                                  | 1  |  |  |

|--------|-------|-----------------------------------------------|----|--|--|

| 1.1    | CHAF  | RACTERISTICS                                  | 1  |  |  |

| 1.2    | ORDE  | ORDERING INFORMATION                          |    |  |  |

| 1.3    | 64-BI | T ARCHITECTURE                                | 2  |  |  |

| 1.4    | VR410 | )1 PROCESSOR                                  | 2  |  |  |

|        | 1.4.1 | Internal Structure                            | 3  |  |  |

|        | 1.4.2 | I/O registers                                 | 4  |  |  |

| 1.5    | VR410 | 00 CPU CORE                                   | 10 |  |  |

|        | 1,5.1 | Internal Structure                            | 10 |  |  |

|        | 1,5.2 | CPU Registers                                 | 11 |  |  |

|        | 1,5.3 | CPU Instruction Set Overview                  | 12 |  |  |

|        | 1.5.4 | Data Formats and Addressing                   | 13 |  |  |

|        | 1.5.5 | Coprocessors (CP0-CP3)                        | 15 |  |  |

|        | 1.5.6 | Floating-Point Unit (FPU)                     | 18 |  |  |

|        | 1.5.7 | Cache                                         | 18 |  |  |

| 1.6    | MEM   | ORY MANAGEMENT SYSTEM (MMU)                   | 18 |  |  |

|        | 1.6.1 | Translation Lookaside Buffer (TLB)            | 18 |  |  |

|        | 1.6.2 | Operating Modes                               | 19 |  |  |

| 1.7    | INST  | RUCTION PIPELINE                              | 19 |  |  |

| 1.8    | CLO   | CK INTERFACE                                  | 19 |  |  |

| СНАРТЕ | ER 2  | CPU INSTRUCTION SET SUMMARY                   | 23 |  |  |

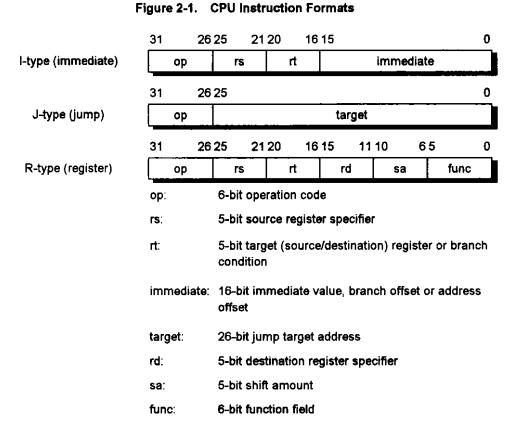

| 2.1    | CPU   | INSTRUCTION FORMATS                           | 23 |  |  |

|        | 2.1.1 | Support of the MIPS ISA                       | 24 |  |  |

| 2.2    | INST  | RUCTION CLASSES                               | 24 |  |  |

|        | 2.2.1 | Load and Store Instructions                   | 24 |  |  |

|        | 2.2.2 | Computational Instructions                    | 26 |  |  |

|        | 2.2.3 | Jump and Branch Instructions                  | 27 |  |  |

|        | 2.2.4 | Special Instructions                          | 27 |  |  |

|        | 2.2.5 | System Control Coprocessor (CP0) Instructions | 28 |  |  |

| 23     | Vp416 | 01 CPU INSTRUCTION SET                        | 28 |  |  |

|             |                                                                                                                                         | VR4101 PIPELINE                                                                                                                                                                                                                                                                                                                                              |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1         |                                                                                                                                         | LINE STAGES                                                                                                                                                                                                                                                                                                                                                  |

|             |                                                                                                                                         | Pipeline Activities                                                                                                                                                                                                                                                                                                                                          |

| 3.2         |                                                                                                                                         | NCH DELAY                                                                                                                                                                                                                                                                                                                                                    |

| 3.3         |                                                                                                                                         | DELAY                                                                                                                                                                                                                                                                                                                                                        |

| 3.4         | PIPE                                                                                                                                    | INE OPERATION                                                                                                                                                                                                                                                                                                                                                |

|             | 3.4.1                                                                                                                                   | Add Instruction (Add rd, rs, rt)                                                                                                                                                                                                                                                                                                                             |

|             | 3.4.2                                                                                                                                   | Jump and Link Register Instruction (JALR rd, rs)                                                                                                                                                                                                                                                                                                             |

|             | 3.4.3                                                                                                                                   | Branch on Equal Instruction (BEQ rs, rt, offset)                                                                                                                                                                                                                                                                                                             |

|             | 3.4.4                                                                                                                                   | Trap if Less Than Instruction (TLT rs, rt)                                                                                                                                                                                                                                                                                                                   |

|             | 3.4.5                                                                                                                                   | Load Word Instruction (LW rt, offset (base))                                                                                                                                                                                                                                                                                                                 |

|             | 3.4.6                                                                                                                                   | Store Word Instruction (SW rt, offset (base))                                                                                                                                                                                                                                                                                                                |

| 3.5         | INTE                                                                                                                                    | RLOCK AND EXCEPTION HANDLING                                                                                                                                                                                                                                                                                                                                 |

|             | 3.5.1                                                                                                                                   | Exception Conditions                                                                                                                                                                                                                                                                                                                                         |

|             | 3.5.2                                                                                                                                   | Stall Conditions.                                                                                                                                                                                                                                                                                                                                            |

|             |                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                              |

|             | 3.5.3                                                                                                                                   | Slip Conditions                                                                                                                                                                                                                                                                                                                                              |

|             |                                                                                                                                         | Slip Conditions                                                                                                                                                                                                                                                                                                                                              |

| 3.6<br>APTE | 3.5.4<br>CODI                                                                                                                           | Bypassing  COMPATIBILITY  MEMORY MANAGEMENT SYSTEM                                                                                                                                                                                                                                                                                                           |

|             | 3.5.4<br>CODI                                                                                                                           | Bypassing  COMPATIBILITY  MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)                                                                                                                                                                                                                                                                          |

| APTE        | 3.5.4<br>CODI<br>R 4<br>TRAN<br>4.1.1                                                                                                   | Bypassing  COMPATIBILITY  MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses                                                                                                                                                                                                                                                         |

| APTE<br>4.1 | 3.5.4<br>CODI<br>ER 4<br>TRAN<br>4.1.1<br>4.1.2                                                                                         | Bypassing  COMPATIBILITY  MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses  Multiple Hit.                                                                                                                                                                                                                                          |

| APTE        | 3.5.4<br>CODI<br>ER 4<br>TRAN<br>4.1.1<br>4.1.2<br>ADDI                                                                                 | Bypassing  E COMPATIBILITY  MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses  Multiple Hit.  RESS SPACES                                                                                                                                                                                                                           |

| APTE<br>4.1 | 3.5.4<br>CODI<br>ER 4<br>TRAN<br>4.1.1<br>4.1.2<br>ADDI                                                                                 | Bypassing  COMPATIBILITY  MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses  Multiple Hit.                                                                                                                                                                                                                                          |

| APTE<br>4.1 | 3.5.4<br>CODI<br>ER 4<br>TRAN<br>4.1.1<br>4.1.2<br>ADDI                                                                                 | Bypassing  E COMPATIBILITY  MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses  Multiple Hit.  RESS SPACES                                                                                                                                                                                                                           |

| APTE<br>4.1 | 3.5.4<br>CODI<br>ER 4<br>TRAN<br>4.1.1<br>4.1.2<br>ADDI<br>4.2.1                                                                        | MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses  Multiple Hit.  RESS SPACES.  Virtual Address Space  Physical Address Space  Virtual-to-Physical Address Translation                                                                                                                                                              |

| APTE<br>4.1 | 3.5.4<br>CODI<br>R 4<br>TRAN<br>4.1.1<br>4.1.2<br>ADDF<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                                              | Bypassing  COMPATIBILITY  MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses  Multiple Hit.  RESS SPACES  Virtual Address Space  Physical Address Space  Virtual-to-Physical Address Translation  32-bit Mode Address Translation                                                                                                    |

| APTE<br>4.1 | 3.5.4<br>CODI<br>R 4<br>TRAN<br>4.1.1<br>4.1.2<br>ADDF<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4                                              | MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses  Multiple Hit.  RESS SPACES.  Virtual Address Space  Physical Address Space  Virtual-to-Physical Address Translation                                                                                                                                                              |

| 4.1<br>4.2  | 3.5.4<br>CODI<br>ER 4<br>TRAN<br>4.1.1<br>4.1.2<br>ADDI<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6                           | Bypassing  COMPATIBILITY  MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses  Multiple Hit.  RESS SPACES  Virtual Address Space.  Physical Address Space.  Virtual-to-Physical Address Translation  32-bit Mode Address Translation  64-bit Mode Address Translation  Operating Modes                                                |

| APTE<br>4.1 | 3.5.4<br>CODI<br>ER 4<br>TRAN<br>4.1.1<br>4.1.2<br>ADDI<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6                           | Bypassing  COMPATIBILITY  MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses  Multiple Hit.  RESS SPACES  Virtual Address Space  Physical Address Space  Virtual-to-Physical Address Translation  32-bit Mode Address Translation  64-bit Mode Address Translation                                                                   |

| 4.1<br>4.2  | 3.5.4<br>CODI<br>ER 4<br>TRAN<br>4.1.1<br>4.1.2<br>ADDI<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>SYST                   | Bypassing  COMPATIBILITY  MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses  Multiple Hit.  RESS SPACES  Virtual Address Space.  Physical Address Space.  Virtual-to-Physical Address Translation  32-bit Mode Address Translation  64-bit Mode Address Translation  Operating Modes                                                |

| 4.1<br>4.2  | 3.5.4<br>CODI<br>R 4<br>TRAN<br>4.1.1<br>4.1.2<br>ADDI<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>SYST<br>4.3.1           | Bypassing  E COMPATIBILITY  MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses  Multiple Hit.  RESS SPACES  Virtual Address Space  Physical Address Space  Virtual-to-Physical Address Translation  32-bit Mode Address Translation  64-bit Mode Address Translation  Operating Modes  EM CONTROL COPROCESSOR                        |

| 4.1<br>4.2  | 3.5.4<br>CODI<br>ER 4<br>TRAN<br>4.1.1<br>4.1.2<br>ADDI<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>SYST<br>4.3.1<br>4.3.2 | Bypassing E COMPATIBILITY  MEMORY MANAGEMENT SYSTEM  ISLATION LOOKASIDE BUFFER (TLB)  Hits and Misses  Multiple Hit.  RESS SPACES.  Virtual Address Space  Physical Address Space  Virtual-to-Physical Address Translation  32-bit Mode Address Translation  64-bit Mode Address Translation  Operating Modes  EM CONTROL COPROCESSOR  Format of a TLB Entry |

| 5.3     | EXCE   | PTION PROCESSING REGISTERS                    | 86  |

|---------|--------|-----------------------------------------------|-----|

|         | 5.3.1  | Context Register (4)                          | 87  |

|         | 5.3.2  | BadVAddr Register (8)                         | 88  |

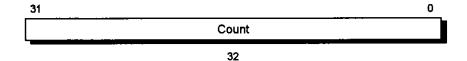

|         | 5.3.3  | Count Register (9)                            | 88  |

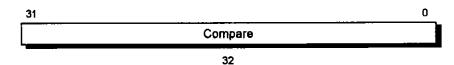

|         | 5.3.4  | Compare Register (11)                         | 89  |

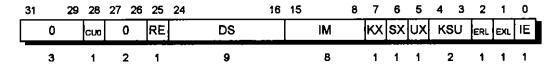

|         | 5.3.5  | Status Register (12)                          | 89  |

|         | 5.3.6  | Cause Register (13)                           | 92  |

|         | 5.3.7  | Exception Program Counter (EPC) Register (14) | 94  |

|         | 5.3.8  | WatchLo (18) and WatchHi (19) Registers       | 95  |

|         | 5.3.9  | XContext Register (20)                        | 96  |

|         | 5.3.10 | Parity Error Register (26)                    | 97  |

|         | 5.3.11 | Cache Error Register (27)                     | 97  |

|         | 5.3.12 | ErrorEPC Register (30)                        | 98  |

| 5.4     | DETA   | ILS OF EXCEPTIONS                             | 99  |

|         | 5.4.1  | Exception Types                               | 99  |

|         | 5.4.2  | Exception Vector Locations                    | 99  |

|         | 5.4.3  | Priority of Exceptions                        | 101 |

|         | 5.4.4  | Cold Reset Exception                          | 102 |

|         | 5.4.5  | Soft Reset Exception                          | 103 |

|         | 5.4.6  | NMI Exception                                 | 104 |

|         | 5.4.7  | Address Error Exception                       | 105 |

|         | 5.4.8  | TLB Exceptions                                | 106 |

|         | 5.4.9  | Cache Error Exception                         | 109 |

|         | 5.4.10 | Bus Error Exception                           | 110 |

|         | 5.4.11 | System Call Exception                         | 111 |

|         | 5.4.12 | Breakpoint Exception                          | 111 |

|         | 5.4.13 | Coprocessor Unusable Exception                | 112 |

|         | 5.4.14 | Reserved Instruction Exception                | 113 |

|         | 5.4.15 | Trap Exception                                | 113 |

|         | 5.4.16 | Integer Overflow Exception                    | 114 |

|         | 5.4.17 | Watch Exception                               | 114 |

|         | 5.4.18 | · · · · · · · · · · · · · · · · · · ·         | 115 |

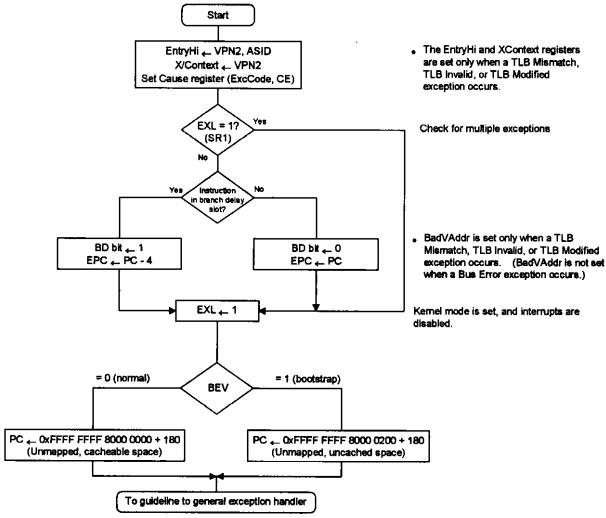

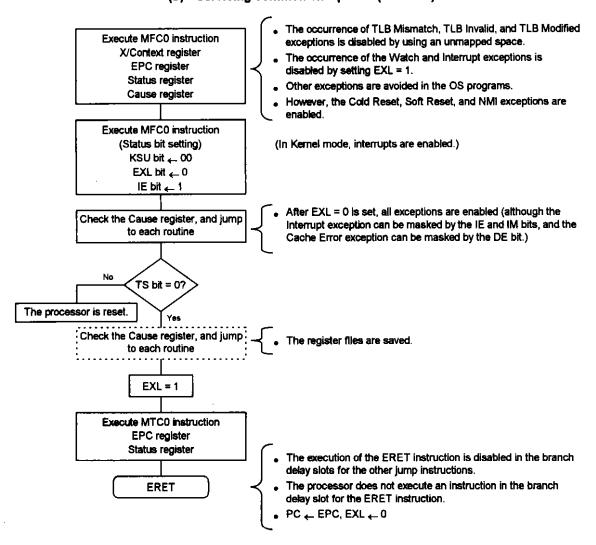

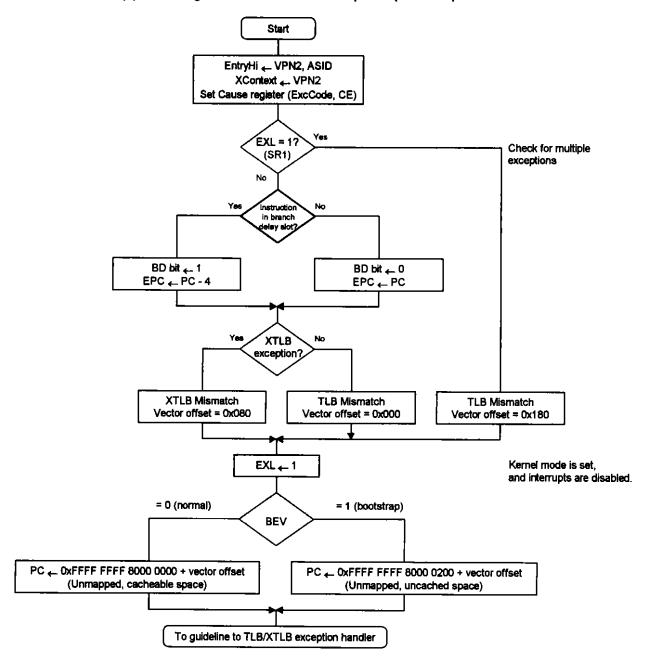

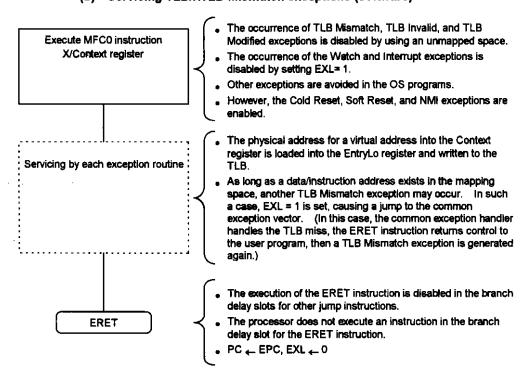

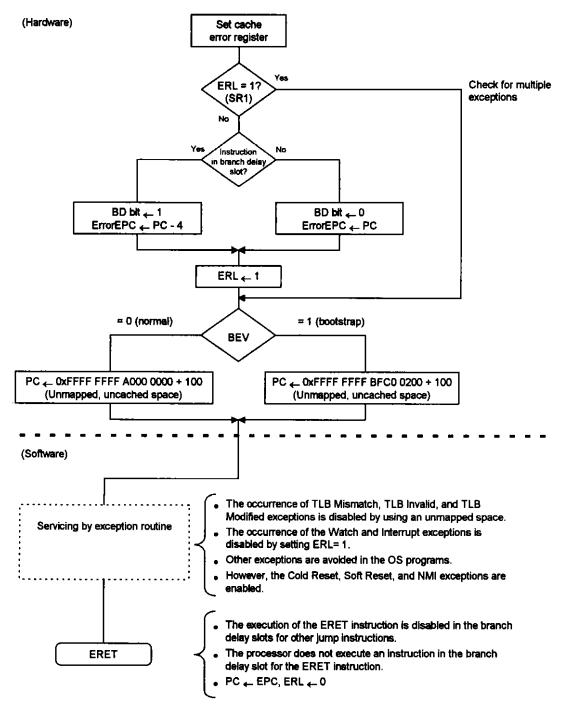

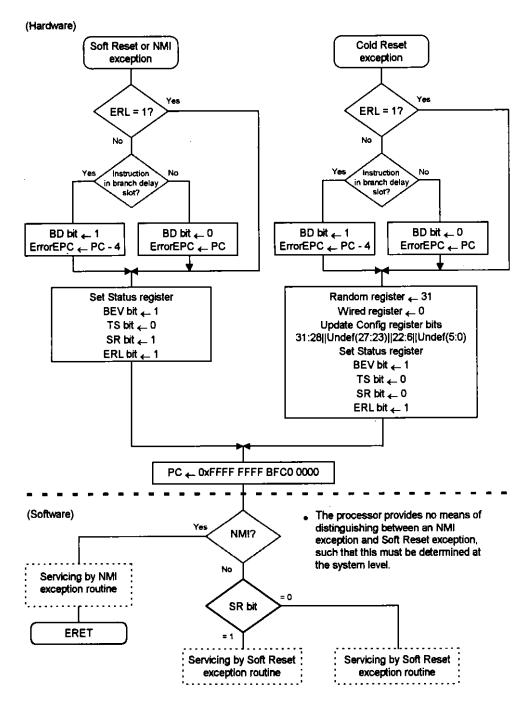

| 5.5     | EXCE   | PTION HANDLING AND SERVICING FLOWCHARTS       | 115 |

|         |        |                                               |     |

| 0114577 | -D.C.  | DIN FUNCTIONS                                 | 466 |

| CHAPTE  |        | PIN FUNCTIONS                                 |     |

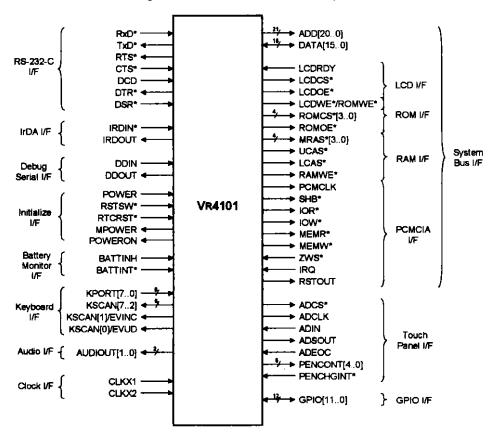

| 6.1     | VR410  | 1 SIGNALS                                     |     |

|         | 6.1.1  | -,                                            | 124 |

|         |        | Clock Interface Signals                       | 125 |

|         | 613    | Rattery Monitor Interface Signals             | 126 |

|      | 6.1.  | 4 Initialization Interface Signals                | 126 |

|------|-------|---------------------------------------------------|-----|

|      | 6,1.  | 5 RS-232-C Interface Signals                      | 127 |

|      | 6.1.  | 6 IrDA Interface Signals                          | 127 |

|      | 6.1.  | 7 Debug Serial Interface Signals                  | 128 |

|      | 6.1.  | 8 Keyboard Interface Signals                      | 128 |

|      | 6.1.  | 9 Audio Interface Signal                          | 129 |

|      | 6.1.  | 10 Touch Panel Interface Signals                  | 129 |

|      | 6.1.  | 11 General-purpose I/O Signals                    | 130 |

| 6.   | 2 STA | TUS OF PINS UPON A SPECIFIC STATE                 | 131 |

| 6.   | 3 PIN | CONFIGURATION                                     | 133 |

|      |       |                                                   |     |

| CHAP | ΓER 7 | INITIALIZATION INTERFACE                          | 135 |

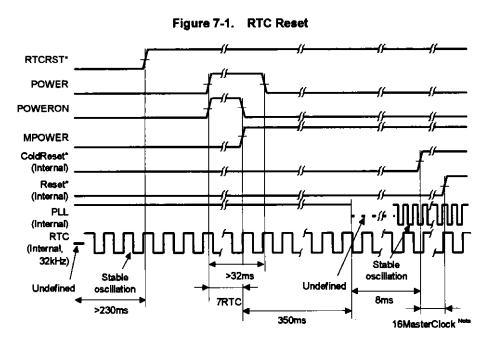

| 7.   | 1 RES | SET FUNCTION                                      | 135 |

|      | 7.1.  | 1 RTC Reset                                       | 135 |

|      | 7.1.  | 2 RSTSW                                           | 136 |

|      | 7.1.  | 3 Deadman'sSW                                     | 137 |

|      | 7.1.  | 4 Software Shutdown                               | 138 |

|      | 7.1.  | 5 HALTimer Shutdown                               | 139 |

| 7.   | 2 PO\ | WER-ON SEQUENCE                                   | 140 |

| 7.   | 3 RES | SET OF THE CPU CORE                               | 142 |

|      | 7.3.  | 1 Cold Reset                                      | 142 |

|      | 7.3.  | 2 Soft Reset                                      | 142 |

| 7.   | 4 VR4 | 101 PROCESSOR MODES                               | 144 |

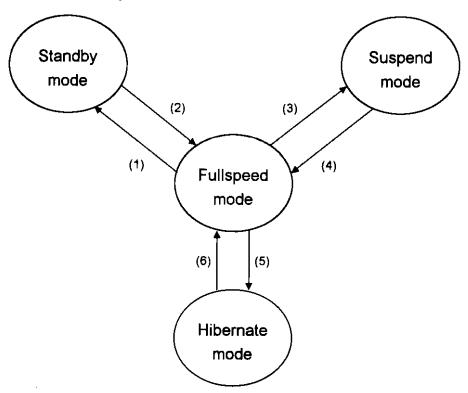

|      | 7.4.  | 1 Power Modes                                     | 144 |

|      | 7.4.  | 2 Privilege Modes                                 | 145 |

|      | 7.4.  | 3 Reverse Endianess                               | 145 |

|      | 7.4.  | 4 Bootstrap Exception Vector (BEV)                | 145 |

|      | 7.4   | 5 Cache Error Check                               | 146 |

|      | 7.4.  | 6 Disable Parity Errors                           | 146 |

|      | 7.4.  | 7 Interrupt Enable (IE)                           | 146 |

|      |       |                                                   |     |

| CHAP | ΓER 8 | CACHE ORGANIZATION AND OPERATION                  | 147 |

| 8.   | 1 MEI | MORY ORGANIZATION                                 | 147 |

| 8.   | 2 CAC | CHE ORGANIZATION                                  | 148 |

|      | 8.2.  | 1 Organization of the Instruction Cache (I-Cache) | 149 |

|      | 8.2.  | 2 Organization of the Data Cache (D-Cache)        | 149 |

|      | 8.2.  | 3 Accessing the Caches                            | 150 |

| 8.   | 3 CAC | CHE OPERATIONS                                    | 151 |

|        | 8.3.1  | Cache Write Policy                           | 151 |

|--------|--------|----------------------------------------------|-----|

| 8.4    | CACH   | HE STATES                                    | 152 |

| 8.5    | CACH   | HE STATE TRANSITION DIAGRAMS                 | 153 |

|        | 8.5.1  | Data Cache State Transition                  | 153 |

|        | 8.5.2  | Instruction Cache State Transition.          | 153 |

| 8.6    |        | HE DATA INTEGRITY                            |     |

| 8.7    | MANI   | IPULATION OF THE CACHES BY AN EXTERNAL AGENT | 164 |

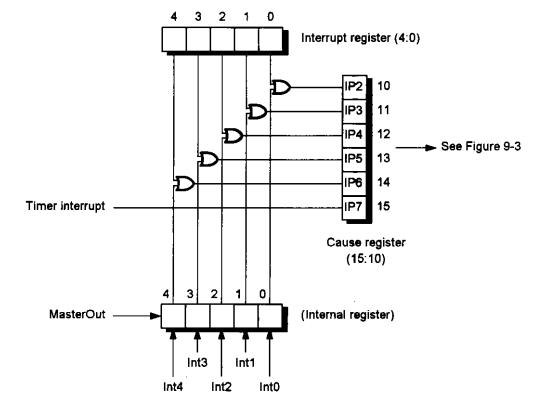

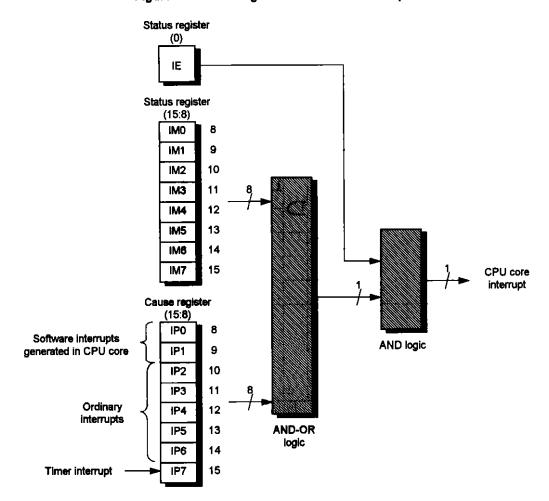

| CHAPTE | R 9    | CPU CORE INTERRUPTS                          | 165 |

| 9.1    | NON    | MASKABLE INTERRUPT (NMI)                     | 165 |

| 9.2    |        | NARY INTERRUPTS                              |     |

| 9.3    | SOFT   | TWARE INTERRUPTS GENERATED IN CPU CORE       | 166 |

| 9.4    | TIME   | R INTERRUPT                                  | 166 |

| 9.5    | ASSE   | ERTING INTERRUPTS                            | 167 |

|        | 9.5.1  | Detecting Hardware Interrupts                | 167 |

|        | 9.5.2  | Masking Interrupt Signals                    | 168 |

|        |        |                                              |     |

| CHAPTE | ER 10  | BCU (BUS CONTROL UNIT)                       | 169 |

| 10.1   | GEN    | NERAL                                        | 169 |

| 10.2   | REG    | BISTER SET                                   | 169 |

|        | 10.2.1 | BCUCNTREG                                    | 170 |

|        | 10.2.2 | 2 BCUBRREG                                   | 171 |

|        | 10.2.3 | B BCUBRCNTREG                                | 172 |

|        | 10.2.4 | 4 BCUBCLREG                                  | 173 |

|        | 10.2.5 | 5 BCUBCLCNTREG                               | 174 |

|        | 10.2.6 | BCUSPEEDREG                                  | 175 |

|        | 10.2.7 | 7 BCUERRSTREG                                | 177 |

|        | 10.2.8 | BCURFCNTREG                                  | 178 |

|        | 10.2.9 | PREVIDREG                                    | 179 |

| 10.3   | MEN    | MORY ACCESS BY BCU                           | 180 |

|        | 10.3.1 | Address Map                                  | 180 |

|        | 10.3.2 | 2 Address Space for ROM                      | 180 |

|        | 10.3.3 | Address Space for Expansion Bus              | 181 |

|        | 10.3.4 | Address Space for Registers                  | 182 |

|        | 10.3.5 | 5 Address Space for LCD                      | 182 |

|        |        | S Address Space for DRAM                     |     |

| 10.4   | CON    | NNECTION OF ADDRESS TERMINALS                |     |

| 10 /   | : NOT  | FES FOR LISING RCLI                          | 185 |

|              | 10.5.1  | CPU Core Bus Modes            | 185 |

|--------------|---------|-------------------------------|-----|

|              | 10.5.2  | Access Data Size              | 185 |

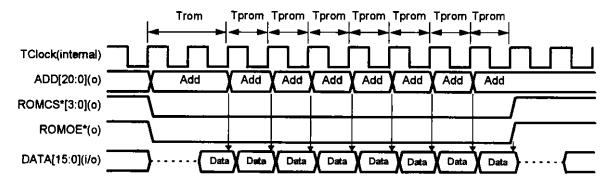

|              | 10.5.3  | ROM Interface                 | 186 |

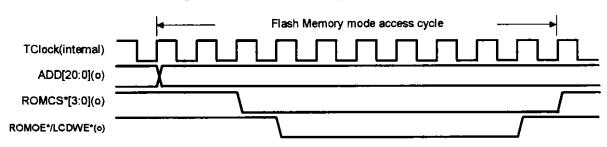

|              | 10.5.4  | Flash Memory Interface        | 187 |

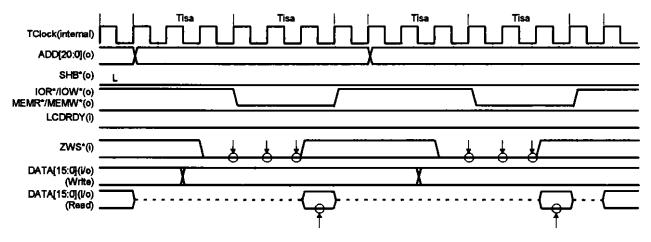

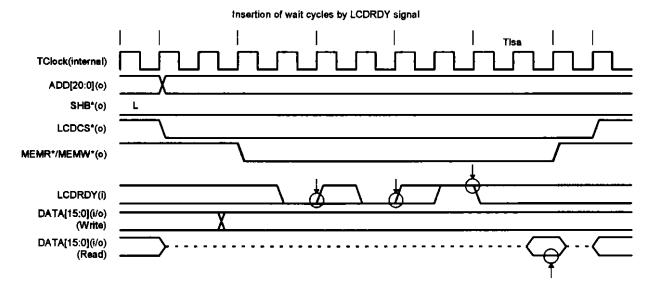

|              | 10.5.5  | Expansion Bus Interface       | 188 |

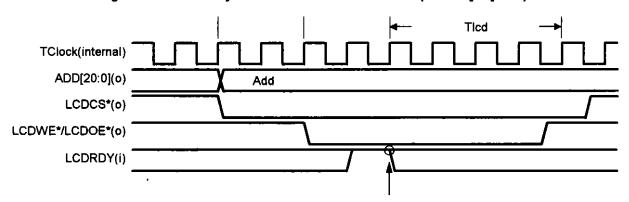

|              | 10.5.6  | LCD Controller Interface      | 189 |

|              | 10.5.7  | Notice of an Illegal Access   | 190 |

| 10.          | 6 BUS   | OPERATION                     | 190 |

|              | 10.6.1  | ROM Access                    | 190 |

|              | 10.6.2  | Expansion Bus Interface       | 194 |

|              | 10.6.3  | LCD Interface.                | 198 |

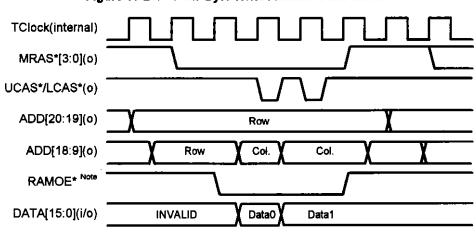

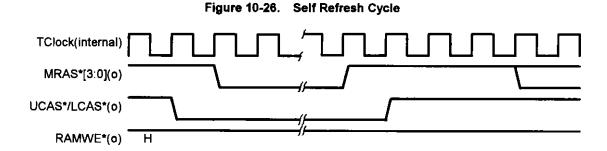

|              | 10.6.4  | DRAM Access (EDO type)        | 199 |

|              | 10,6.5  | Refresh                       | 202 |

|              |         |                               |     |

| OUADT        | ED 44   | DIALALI (DIALA ADDDDOG LINUT) |     |

| CHAPTI       |         | DMAAU (DMA ADDRESS UNIT)      |     |

| 11.1         |         | ERAL                          |     |

| 11.:         | - · · · | STER SET                      |     |

|              | 11.2.1  | PADDMAADRLREG, PADDMAADRHREG  |     |

|              |         | SRXDMAADRLREG, SRXDMAADRHREG  |     |

|              |         | STXDMAADRLREG, STXDMAADRHREG  |     |

|              |         | AUDDMAADRLREG, AUDDMAADRHREG  |     |

|              | 11.2.5  | KEYDMAADRLREG, KEYDMAADRHREG  | 209 |

|              |         |                               |     |

|              |         | DCU (DMA CONTROL UNIT)        |     |

| 12.          |         | ERAL                          | 211 |

| 12.          | 2 REGI  | STER SET                      | 211 |

|              | 12.2.1  | DMARSTREG                     | 212 |

|              | 12.2.2  | DMAIDLEREG                    | 213 |

|              | 12.2.3  | DMASENREG                     | 214 |

|              | 12.2.4  | DMAMSKREG                     | 215 |

|              | 12.2.5  | DMAREQREG                     | 216 |

| СНАРТ        | FR 13   | CMU (CLOCK MASK UNIT)         | 217 |

| 13.1<br>13.1 |         | ERAL                          |     |

| 13.          |         | STER SET                      |     |

| 13.4         |         | CMUCLKMSKREG                  |     |

|              | 1J.Z. I | CINIOCENINION/NEG             | 219 |

| CHAI | PTEF         | ₹ 14    | ICU (INTERRUPT CONTROL UNIT)    | 221 |

|------|--------------|---------|---------------------------------|-----|

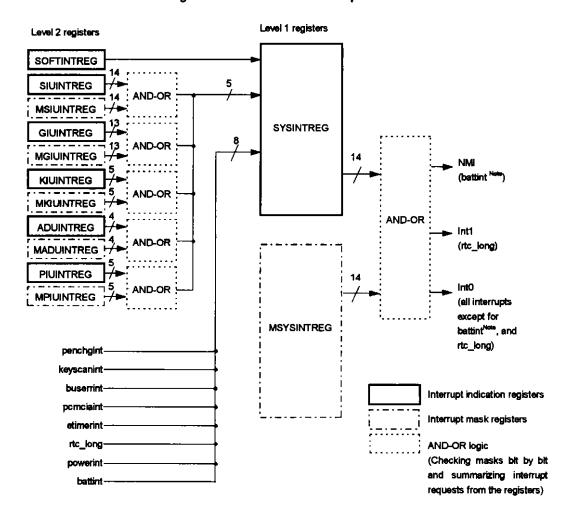

|      | 14.1         | GEN     | ERAL                            | 221 |

|      | 14.2         | REGI    | STER SET                        | 223 |

|      |              | 14.2.1  | Level-1 System Register         | 224 |

|      |              | 14.2.2  | Level-2 PIU Register            | 226 |

|      |              | 14.2.3  | Level-2 AIU Register            | 227 |

|      |              | 14.2.4  | Level-2 KIU Register            | 228 |

|      |              | 14.2.5  | Level-2 GIU Register            | 229 |

|      |              | 14.2.6  | Level-2 SIU Register            | 230 |

|      |              | 14.2.7  | Level-1 Mask System Register    | 232 |

|      |              | 14.2.8  | Level-2 Mask PIU Register       | 234 |

|      |              | 14.2.9  | Level-2 Mask AIU Register       | 235 |

|      |              | 14.2.10 | Level-2 Mask KIU Register       | 236 |

|      |              | 14.2.11 | Level-2 Mask GIU Register       | 237 |

|      |              | 14.2.12 | 2 Level-2 Mask SIU Register     | 238 |

|      |              | 14.2.13 | NMI Register                    | 240 |

|      |              | 14.2.14 | Software Interrupt Register     | 241 |

|      | 14.3         | NOTE    | ES FOR REGISTER SETTING         | 242 |

| CHAI | PTEF<br>15.1 |         | PMU (POWER MANAGEMENT UNIT)     |     |

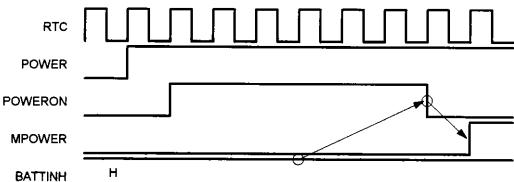

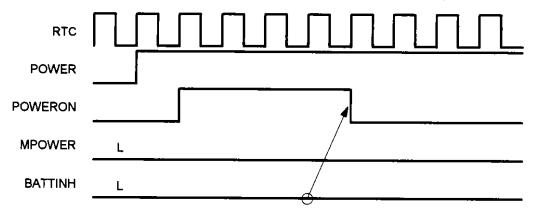

|      |              | 15.1.1  | Reset Control                   | 243 |

|      |              | 15.1,2  | Shutdown Control                | 244 |

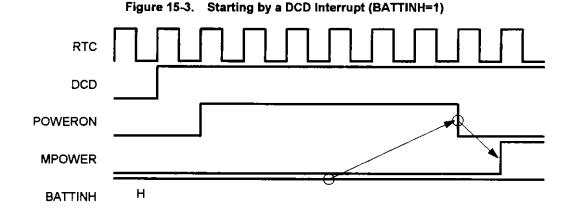

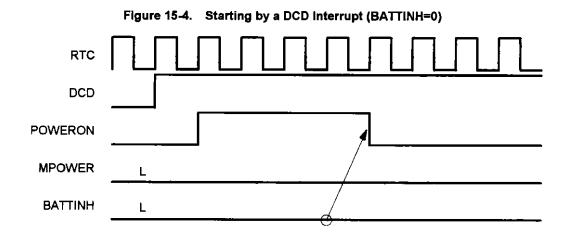

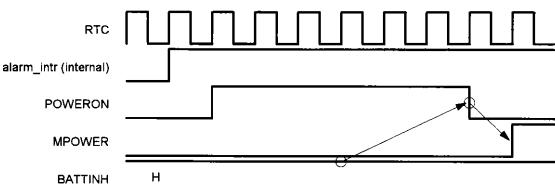

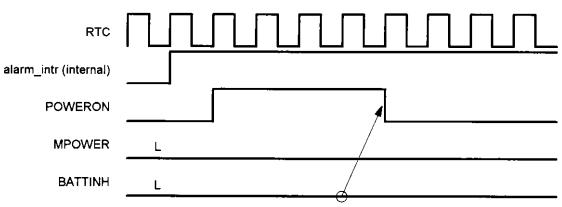

|      |              | 15.1.3  | Power-on Control                | 245 |

|      |              | 15.1.4  | Power Mode                      | 248 |

|      | 15.2         | REGI    | STER SET                        | 251 |

|      |              | 15.2.1  | PMUINTREG                       | 252 |

|      |              | 15.2.2  | PMUCNTREG                       | 254 |

|      |              |         |                                 |     |

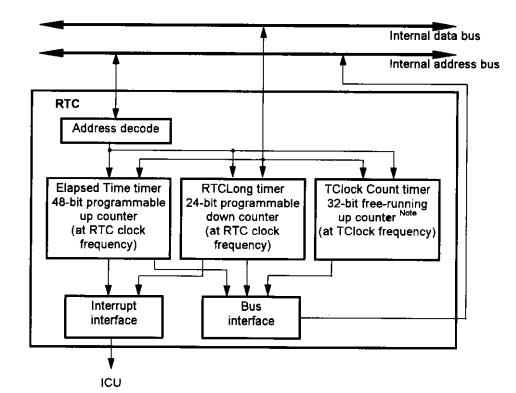

| CHA  | )<br>)<br>   | 2 16    | RTC (REALTIME CLOCK UNIT)       | 255 |

|      | 16.1         |         | •                               | 255 |

|      | 16.2         |         | STER SET                        |     |

|      |              |         | ETIMELREG, ETIMEMREG, ETIMEHREG |     |

|      |              |         | ECMPHREG, ECMPLREG, ECMPMREG    |     |

|      |              | 16.2.3  | RTCLLREG, RTCLHREG              | 260 |

|      |              |         | RTCLCNTLREG, RTCLCNTHREG.       | 262 |

|      |              |         | TCLKCNTLREG, TCLKCNTHREG        | 264 |

|      |              |         | PTCINTECO                       | 204 |

| CHAP | TEF  | ₹ 17   | DSU (DEADMAN'S SW UNIT)                 | 267   |

|------|------|--------|-----------------------------------------|-------|

|      | 17.1 |        | RAL                                     |       |

| 1    | 17.2 | REGI   | STER SET                                | 267   |

|      |      | 17.2.1 | DSU Control Register                    | 268   |

|      |      | 17.2.2 | DSU Dead Time Setting Register          | 269   |

|      |      | 17.2.3 | DSU Clear Register                      | 270   |

|      |      | 17.2.4 | DSU Elapsed Time Register               | 271   |

| 1    | 17.3 | REGI   | STER SETTING FLOW                       | . 272 |

| CHAP | TEF  | R 18   | GIU (GENERAL PURPOSE I/O UNIT)          | 273   |

|      | 18.1 |        | ERAL                                    |       |

| 1    | 18.2 | REGI   | STER SET                                | . 274 |

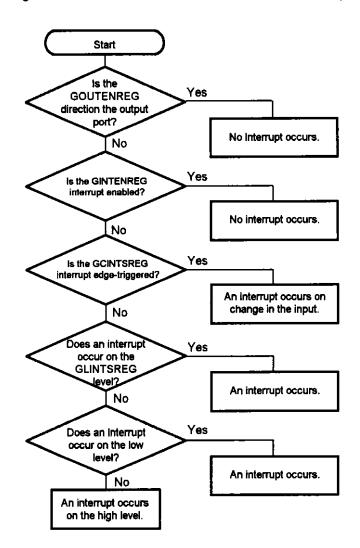

|      |      | 18.2.1 | GPIO Output Enable Register             | 274   |

|      |      | 18.2.2 | GPIO Port Data Register                 | 275   |

|      |      | 18.2.3 | GPIO Interrupt Status Register          | 276   |

|      |      | 18.2.4 | GPIO Interrupt Enable Register          | 277   |

|      |      | 18.2.5 | GPIO Change Point Interrupt Register    | 278   |

|      |      | 18.2.6 | Interrupt Level Identifying Register    | 279   |

| 1    | 18.3 | REGI   | STER SETTING FLOW                       | 280   |

| 1    | 18.4 | INTE   | RRUPT FROM GPIO PINS                    | 281   |

| 1    | 18.5 | FUNC   | CTIONS TO ACHIEVE LOW POWER CONSUMPTION | 282   |

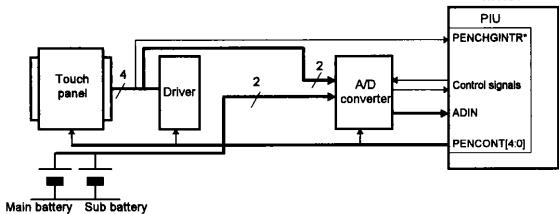

| CHAP | TEF  | R 19   | PIU (TOUCH PANEL INTERFACE UNIT)        | 283   |

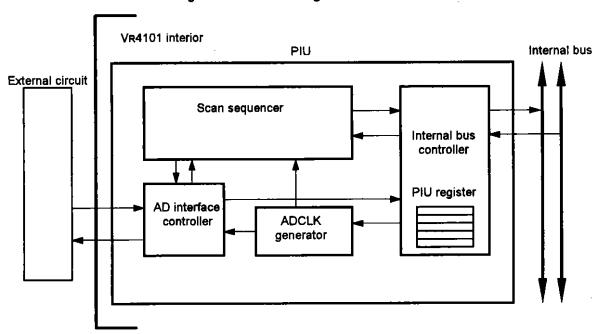

| 1    | 19.1 | GENE   | ERAL                                    | 283   |

|      |      | 19.1.1 | Block Diagram                           | 284   |

|      |      | 19.1.2 | Scan Sequencer State Transition         | 286   |

| 1    | 19.2 | REGI   | STER SET                                | 288   |

|      |      | 19.2.1 | PIUDATAREG                              | 288   |

|      |      | 19.2.2 | PIUCNTREG                               | 289   |

|      |      | 19.2.3 | PIUINTREG                               | 291   |

|      |      | 19.2.4 | PIUSIVLREG                              | 292   |

|      |      | 19.2.5 | PIUSTBLREG                              | 293   |

|      |      | 19.2.6 | PIUCMDREG                               | 294   |

|      |      | 19.2.7 | PIUCIVLREG                              | 295   |

| 1    | 19.3 | REGI   | STER SETTING FLOW                       | 296   |

| 1    | 19.4 | OUTE   | PUT TO PENCONT PINS                     | 298   |

|      |                | 19.4.1  | Order of Coordinate Data                   | 299 |

|------|----------------|---------|--------------------------------------------|-----|

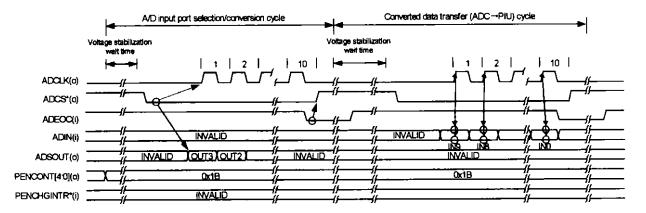

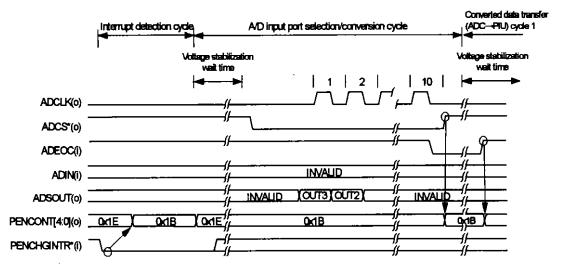

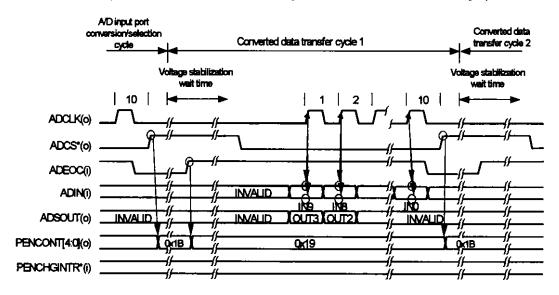

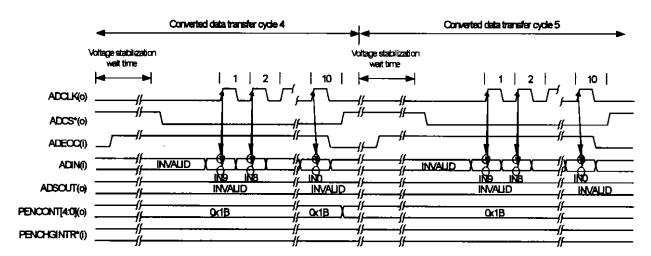

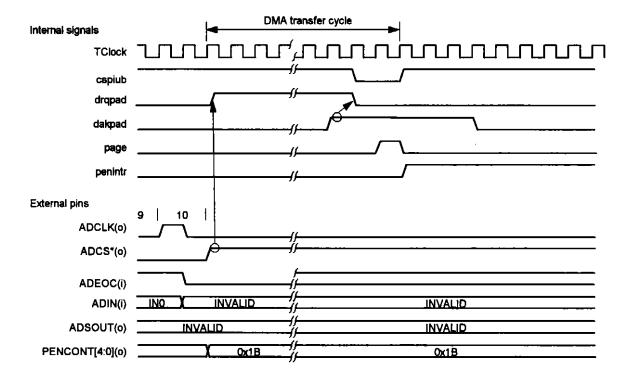

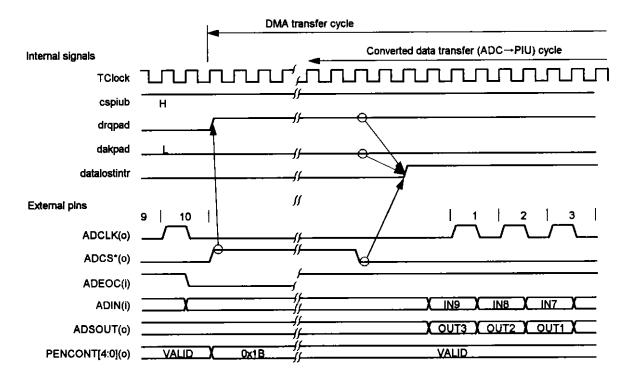

|      | 19.5           | PIU O   | PERATION TIMINGS                           | 300 |

|      |                | 19.5.1  | Explanation of signals in the timing chart | 300 |

|      |                | 19.5.2  | Battery Voltage Detection                  | 301 |

|      |                | 19.5.3  | Coordinate Detection                       | 301 |

|      |                | 19.5.4  | Page Boundary Interrupt                    | 303 |

|      |                | 19.5.5  | Data Lost                                  | 304 |

|      |                | 19.5.6  | Other cautions                             | 305 |

| CHAI | DTE            | R 20    | SIU (SERIAL INTERFACE UNIT)                | 307 |

|      | r i ⊑r<br>20.1 |         | RAL                                        |     |

|      | 20.1           |         |                                            |     |

|      | 20.2           |         | TRANSMIT/RECEIVE DATA FORMAT               |     |

|      |                | 20.2.1  | SIURXDATREG                                |     |

|      |                |         | SIUTXDATREG                                |     |

|      |                |         | SIUCNTREG                                  |     |

|      |                | 20.2.4  |                                            |     |

|      |                |         | SIUINTREG                                  |     |

|      |                | 20.2.6  | ·                                          |     |

|      |                | 20.2.7  | SIUBAUDSELREG                              | 322 |

|      | 20.3           | REGI    | STER SETTING FLOW                          | 323 |

|      | 20.4           | OPER    | NATION OF THE SIU                          | 325 |

|      |                |         |                                            |     |

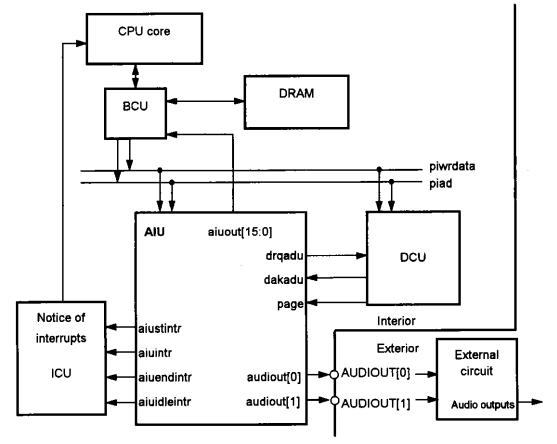

| CHAI | PTE            | R 21    | AIU (AUDIO INTERFACE UNIT)                 | 327 |

|      | 21.1           |         | RAL                                        |     |

|      | 21.2           |         | STER SET                                   |     |

|      |                |         | AIUDATREG                                  |     |

|      |                |         | AIURESETREG                                | 330 |

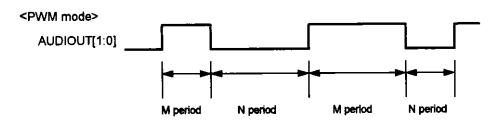

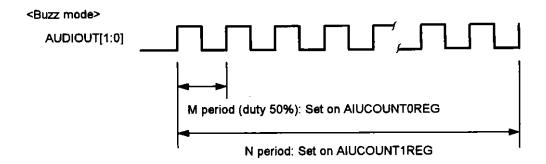

|      |                |         | AIUMODEREG                                 | 331 |

|      |                |         | AIUSEQENREG                                | 332 |

|      |                |         | AIUMUTEREG                                 | 333 |

|      |                | 21.2.6  | AIUSTATREG                                 | 334 |

|      |                | 21.2.7  | AIUSTPPAGEREG                              | 335 |

|      |                |         | AIUVALIDREG                                | 336 |

|      |                |         | AIUINTREG                                  | 337 |

|      |                | 21.2.10 | AIUCOUNT0REG                               | 339 |

|      |                | 21.2.11 | AIUCOUNT1REG                               | 340 |

|      |                | 21.2.12 | AIUREPNUMREG                               | 342 |

|     |           | 21.2.13 | AIUBUSENREG                                                                                         | 343 |

|-----|-----------|---------|-----------------------------------------------------------------------------------------------------|-----|

|     | 21.3      | REGIS   | STER SETTING FLOW                                                                                   | 344 |

|     |           | 21.3.1  | DMA transfer in the PWM mode                                                                        | 344 |

|     |           | 21.3.2  | In the Buzz Mode <or case="" dma="" in="" is="" mode="" not="" pwm="" the="" used="" where=""></or> | 346 |

| СНА | PTFI      | R 22    | KIU (KEYBOARD INTERFACE UNIT)                                                                       | 340 |

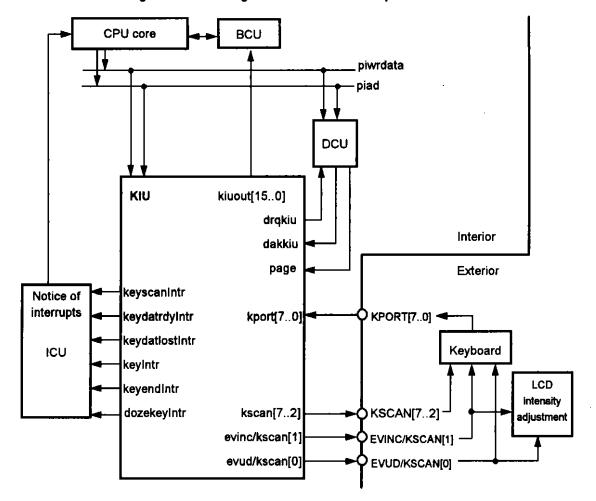

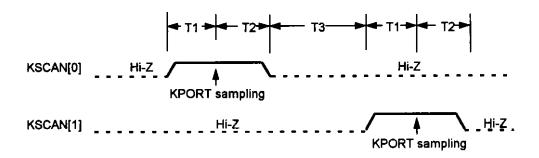

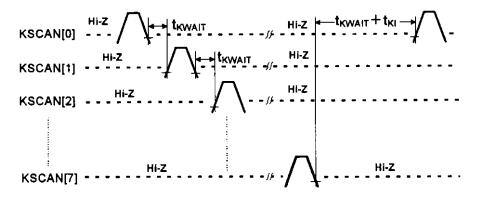

|     | 22.1      |         | RAL                                                                                                 |     |

|     | <b></b> . |         | Outlined Operation of the KIU                                                                       |     |

|     | 22.2      |         | EGISTER SET                                                                                         |     |

|     |           | 22.2.1  | KIUDATREG                                                                                           |     |

|     |           |         | KIUASCANREG                                                                                         |     |

|     |           |         | KIUASTOPREG                                                                                         |     |

|     |           |         | KIUSCANREG                                                                                          |     |

|     |           |         | KIUSTOPREG                                                                                          |     |

|     |           |         | KIUSAPREG                                                                                           |     |

|     |           | 22.2.7  | KIUSCANSREG                                                                                         |     |

|     |           | 22.2.8  | KIUWKSREG                                                                                           |     |

|     |           | 22.4.9  | KIUWKIREG                                                                                           | 360 |

|     |           | 22.2.10 | KIUSRNREG                                                                                           | 362 |

|     |           | 22.2.11 | KIUINTREG                                                                                           | 363 |

|     |           | 22.2.12 | KIURSTREG                                                                                           | 365 |

|     |           | 22.2.13 | KIUENREG                                                                                            | 366 |

|     |           | 22.2.14 | DOZEKEYINTREG                                                                                       | 367 |

|     |           | 22.2.15 | EVVOLREG                                                                                            | 368 |

|     | 22.3      | REGIS   | STER SETTING FLOW                                                                                   | 369 |

|     |           | 22.3.1  | Setting Flow on the KIU (To the End of DMA Transfer)                                                | 369 |

|     |           | 22.3.2  | Setting Flow for Shifting to Suspend Mode (or Standby Mode with TClock Masked)                      | 372 |

| CHA | PTEI      | R 23    | DEBUGSIU (DEBUG SERIAL INTERFACE UNIT)                                                              | 373 |

|     | 23.1      |         | RAL                                                                                                 |     |

|     | 23.2      |         | STER SET                                                                                            |     |

|     |           |         | ASIM00REG                                                                                           |     |

|     |           |         | ASIM01REG                                                                                           |     |

|     |           |         | RXBORREG                                                                                            |     |

|     |           |         | RXB0LREG.                                                                                           | 377 |

|     |           |         | TXSORREG                                                                                            |     |

|     |           |         | TXS0LREG                                                                                            |     |

|     |           |         | ASISADEC                                                                                            | 200 |

|         | 23.2.8 INTRURES                       |     |

|---------|---------------------------------------|-----|

|         | 23.2.9 BPRM0REG                       | 382 |

|         | 23.2.10 DSIURESETREG                  | 383 |

| CHAPTEI | R 24 CPU INSTRUCTION SET DETAILS      | 385 |

| 24.1    | INSTRUCTION CLASSES                   |     |

| 24.2    |                                       |     |

|         | INSTRUCTION NOTATION CONVENTIONS      |     |

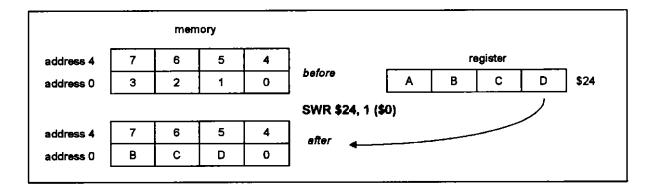

| 2-7.0   | 24.3.1 Instruction Notation Examples. |     |

| 24.4    | ·                                     |     |

| 24.5    |                                       |     |

| 24.6    |                                       |     |

|         | CPU INSTRUCTION OPCODE BIT ENCODING   |     |

| CHAPTEI | R 25 VR4101 COPROCESSOR 0 HAZARDS     | 537 |

| CHAPTEI | R 26 PLL PASSIVE COMPONENTS           | 543 |

| ADDENIN | IY INDEY                              | 545 |

### [MEMO]

# LIST OF FIGURES (1/8)

| Fig. No.     | Title                                                                      | Page |

|--------------|----------------------------------------------------------------------------|------|

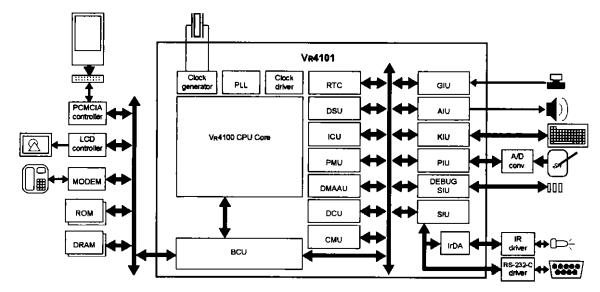

| 1-1.         | VR4101 Internal Block Diagram and Example of Connection to External Blocks | 2    |

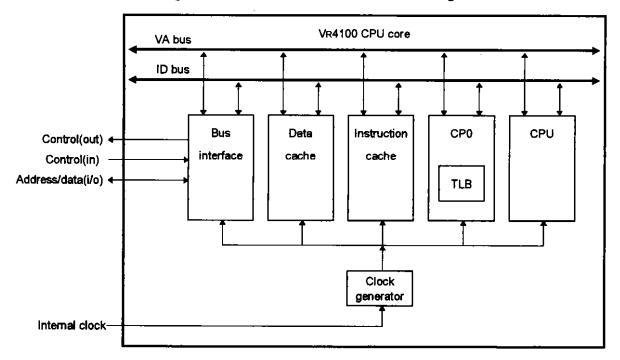

| 1-2.         | VR4100 CPU Core Internal Block Diagram                                     | 10   |

| 1-3.         | VR4101 CPU Registers                                                       | 12   |

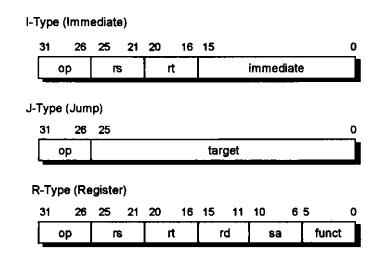

| 1-4.         | CPU Instruction Formats                                                    | 12   |

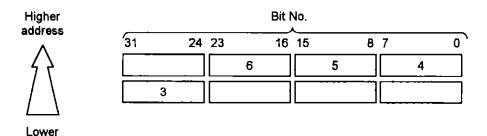

| 1-5.         | Little-Endian Byte Ordering                                                | 14   |

| 1-6.         | Little-Endian Data in a Doubleword                                         | 14   |

| 1-7.         | Misaligned Word Accessing (Little-Endian)                                  | 15   |

| 1-8.         | CP0 Registers                                                              | 16   |

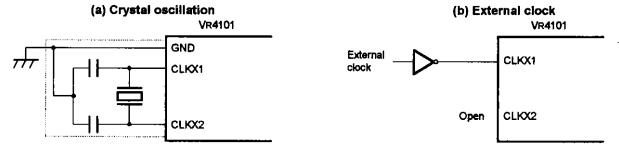

| 1-9.         | External Circuit of Clock Oscillator                                       | 20   |

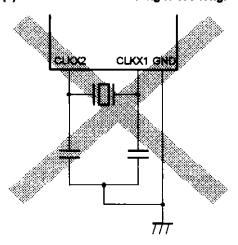

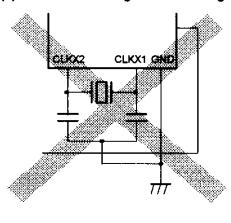

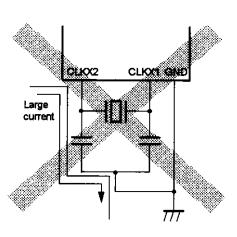

| 1-10.        | Examples of Oscillator with Bad Connection                                 | 21   |

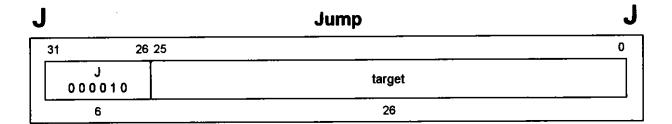

| 2-1.         | CPU Instruction Formats                                                    | 23   |

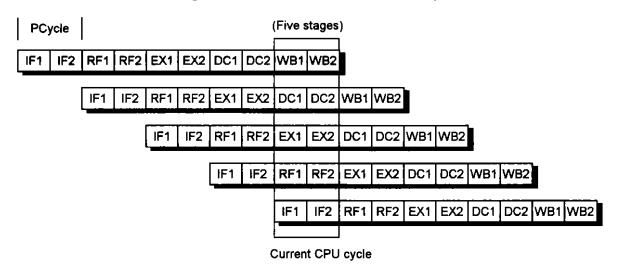

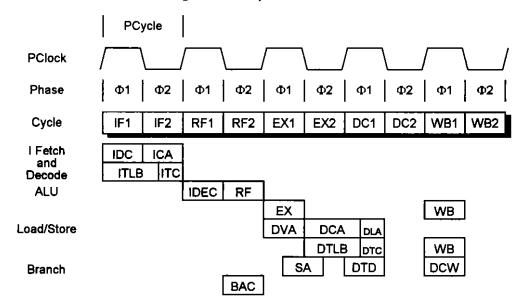

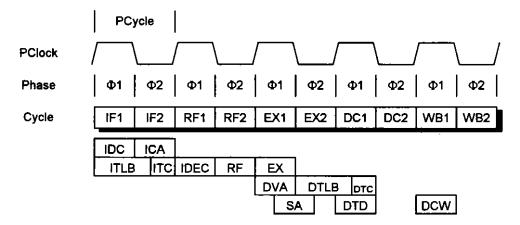

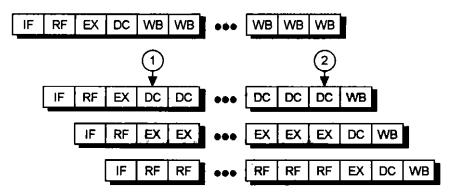

| 3-1.         | Pipeline Stages                                                            | 35   |

| 3-2.         | Instruction Execution in the Pipeline                                      | 36   |

| 3-3.         | Pipeline Activities                                                        | 36   |

| 3-4.         | Branch Delay                                                               | 38   |

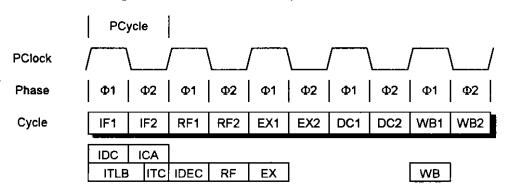

| 3-5.         | Add Instruction Pipeline Activities                                        | 39   |

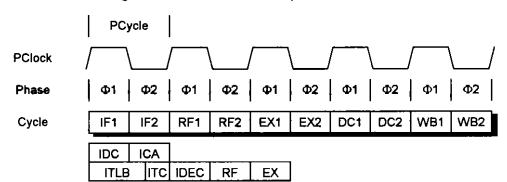

| 3-6.         | JALR Instruction Pipeline Activities                                       | 40   |

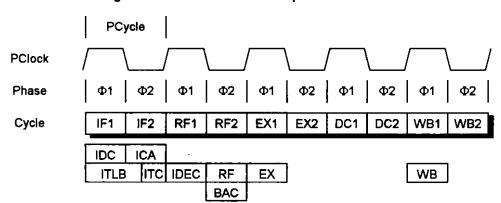

| 3-7.         | BEQ Instruction Pipeline Activities                                        | 41   |

| 3-8.         | TLT Instruction Pipeline Activities                                        | 42   |

| 3-9.         | LW Instruction Pipeline Activities                                         | 43   |

| 3-10.        | SW Instruction Pipeline Activities                                         | 44   |

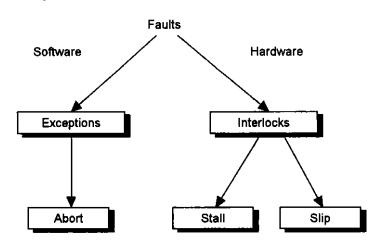

| 3-11.        | Interlocks, Exceptions, and Faults                                         | 45   |

| 3-12.        | Correspondence of Pipeline Stage to Interlock and Exception Condition      | 46   |

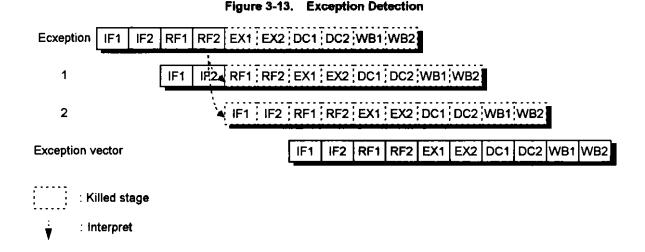

| 3-13.        | Exception Detection                                                        | 48   |

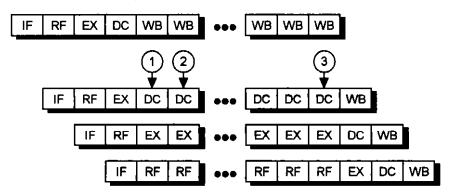

| 3-14.        | Data Cache Miss Stall.                                                     | 49   |

| 3-15.        | CACHE Instruction Stall                                                    | 49   |

| 3-16.        | Load Data Interlock                                                        | 50   |

| 3-17.        | MD Busy Interlock                                                          | 50   |

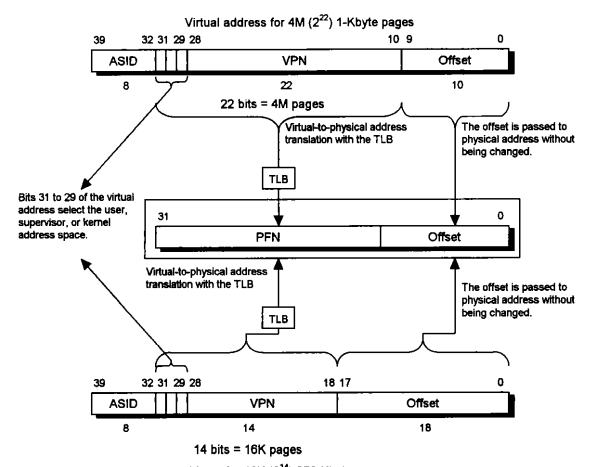

| <b>4-1</b> . | Virtual-to-Physical Address Translation                                    | 54   |

| 4-2.         | VR4101 Physical Address Space                                              | 55   |

| 4-3.         | 32-bit Mode Virtual Address Translation                                    | 57   |

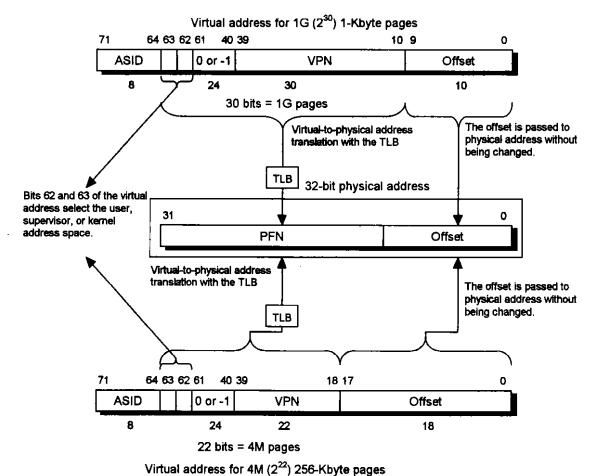

| 4-4.         | 64-bit Mode Virtual Address Translation                                    | 58   |

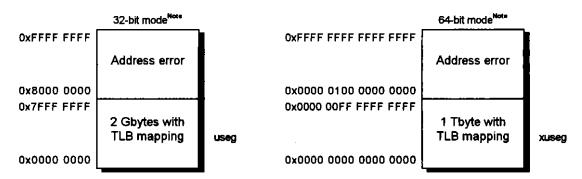

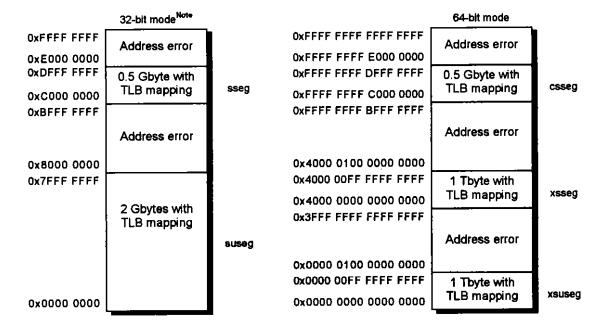

| 4-5.         | User Mode Address Space                                                    | 59   |

# LIST OF FIGURES (2/8)

| Fig. No.      | Title                                              | Page |

|---------------|----------------------------------------------------|------|

| 4-6.          | Supervisor Mode Address Space                      | 61   |

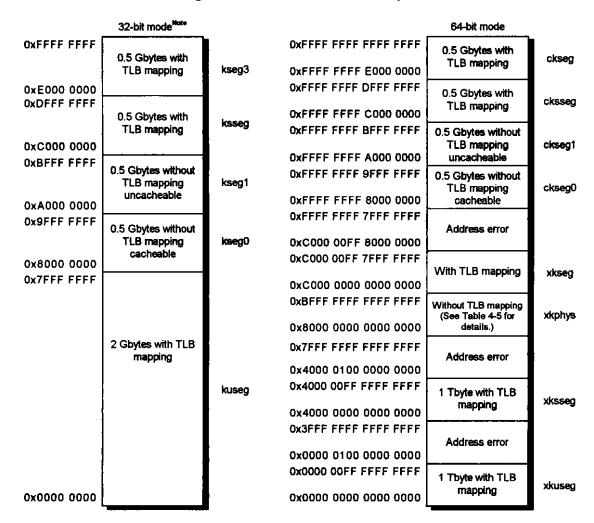

| 4-7.          | Kernel Mode Address Space                          | 64   |

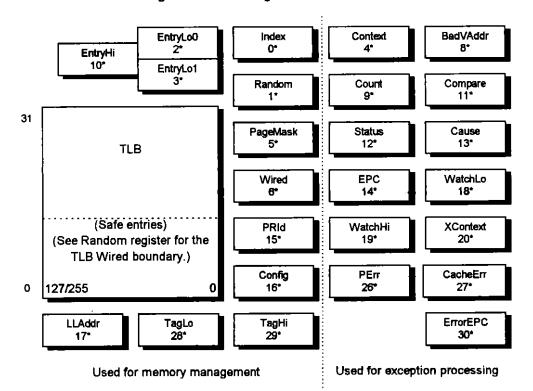

| <b>4-8</b> .  | CP0 Registers and the TLB                          | 69   |

| 4-9.          | Format of a TLB Entry                              | 70   |

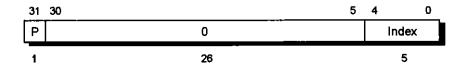

| <b>4-10</b> . | Index Register                                     | 71   |

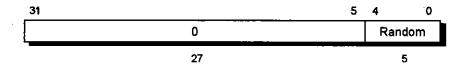

| 4-11.         | Random Register                                    | 72   |

| 4-12.         | EntryLo0 and EntryLo1 Registers                    | 73   |

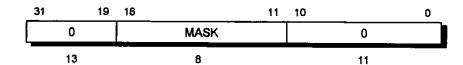

| 4-13.         | Page Mask Register                                 | 74   |

| 4-14.         | Positions Indicated by the Wired Register          | 75   |

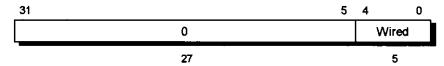

| 4-15.         | Wired Register                                     | 75   |

| <b>4</b> -16. | EntryHi Register                                   | 76   |

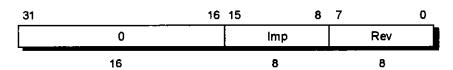

| 4-17.         | PRId Register                                      | 77   |

| 4-18.         | Config Register Format                             | 78   |

| 4-19.         | LLAddr Register                                    | 79   |

| 4-20.         | TagLo Register                                     | 80   |

| 4-21.         | TagHi Register                                     | 80   |

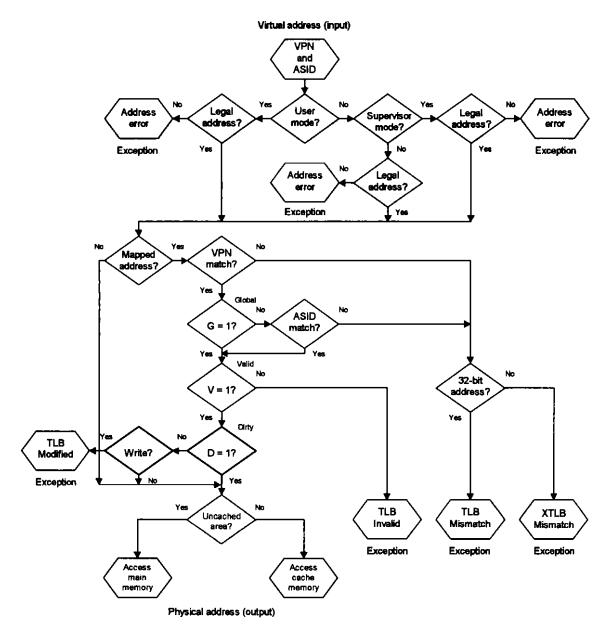

| 4-22.         | TLB Address Translation                            | 82   |

| 5-1.          | Context Register Format                            | 87   |

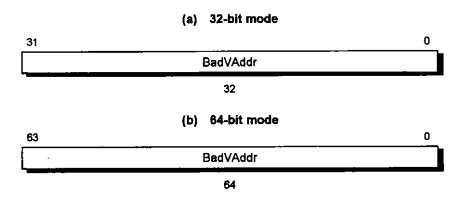

| 5-2.          | BadVAddr Register Format                           | 88   |

| 5-3.          | Count Register Format                              | 88   |

| <b>5-4</b> .  | Compare Register Format                            | 89   |

| 5-5.          | Status Register Format                             | 89   |

| <b>5-6</b> .  | Status Register Diagnostic Status Field            | 90   |

| <b>5-</b> 7.  | Cause Register Format                              | 92   |

| 5-8.          | EPC Register Format                                | 94   |

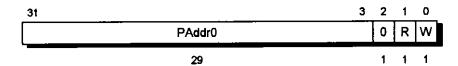

| 5-9.          | WatchLo Register Format                            | 95   |

| 5-10.         | WatchHi Register Format                            | 95   |

| 5-11.         | XContext Register Format                           | 96   |

| 5-12.         | PErr Register Format                               | 97   |

| 5-13.         | CacheErr Register Format                           | 97   |

| 5-14.         | The ErrorEPC Register Format                       | 98   |

| 5-15.         | Common Exception Handling                          | 116  |

| 5-16.         | TLB/XTLB Mismatch Exception Handling               | 118  |

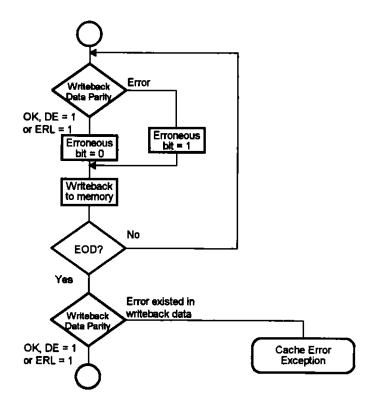

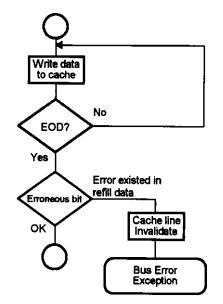

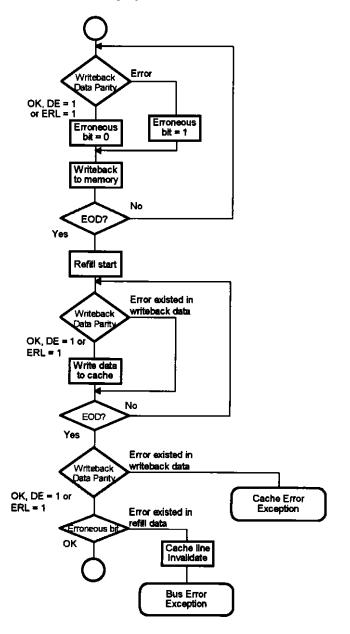

| 5-17.         | Cache Error Exception Handling                     | 120  |

| 5-18.         | Cold Reset, Soft Reset, and NMI Exception Handling | 121  |

## LIST OF FIGURES (3/8)

| Fig. No.      | Title                                                   | Page |

|---------------|---------------------------------------------------------|------|

| 6-1.          | VR4101 Processor Signals                                | 123  |

| 6-2.          | Pinout of the 160-pin LQFP                              | 133  |

| 7-1.          | RTC Reset                                               | 135  |

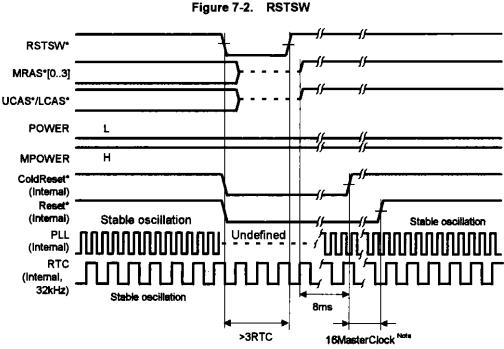

| 7-2.          | RSTSW                                                   | 136  |

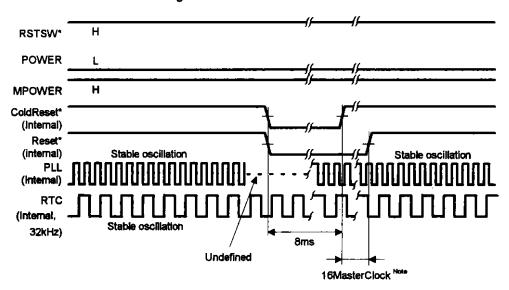

| 7-3.          | Deadman's SW                                            | 137  |

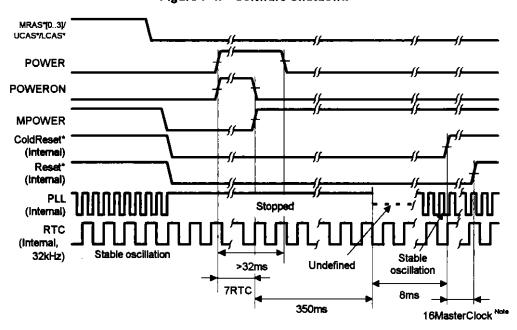

| 7-4.          | Software Shutdown                                       | 138  |

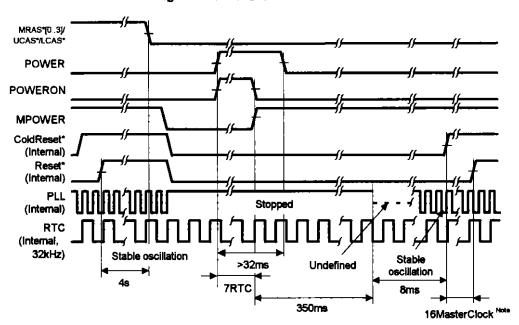

| 7-5.          | HALTimer Shutdown                                       | 139  |

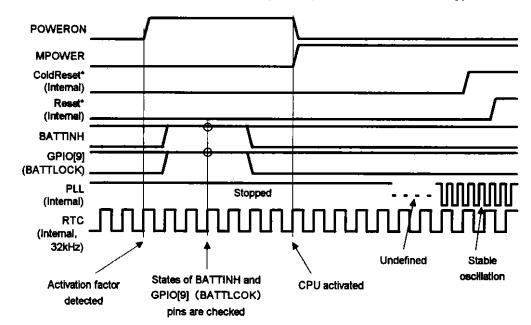

| 7 <b>-</b> 6. | VR4101 Activation Sequence (When Activated Normally)    | 140  |

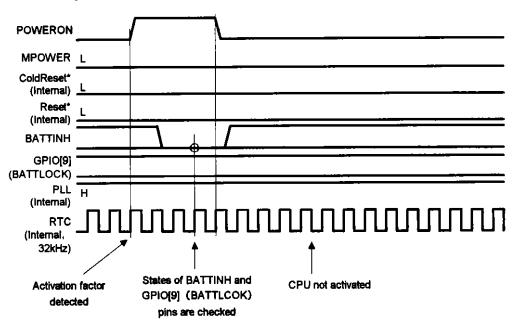

| 7-7.          | VR4101 Activation Sequence (When Activation Fails)      | 141  |

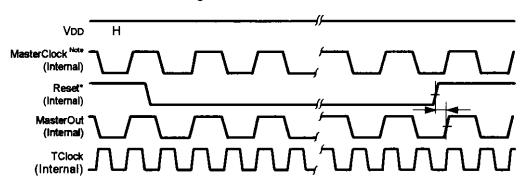

| <b>7-8</b> .  | Cold Reset                                              | 143  |

| 7-9.          | Soft Reset                                              | 143  |

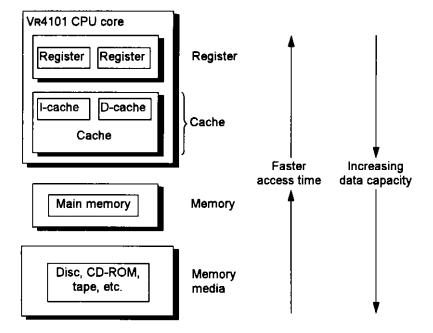

| 8-1.          | Logical Hierarchy of Memory                             | 147  |

| 8-2.          | Cache Support                                           | 148  |

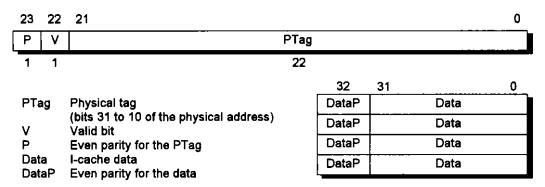

| 8-3.          | I-Cache Line Format                                     | 149  |

| 8-4.          | Data Cache Line Format                                  | 150  |

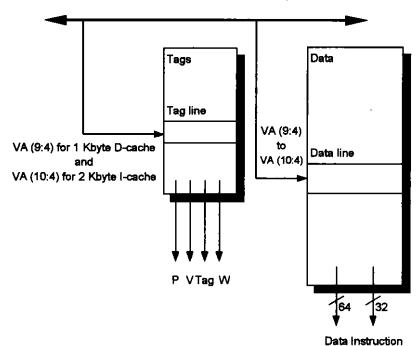

| <b>8-</b> 5.  | Cache Data and Tag Organization                         | 150  |

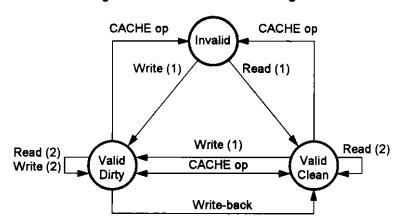

| <b>8-</b> 6.  | Data Cache State Diagram                                | 153  |

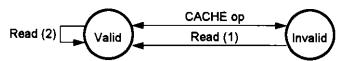

| 8-7.          | Instruction Cache State Diagram                         | 153  |

| 8-8.          | Data flow on Instruction Fetch                          | 154  |

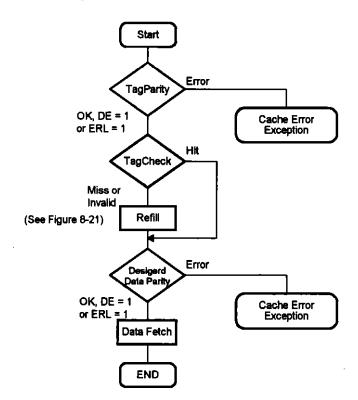

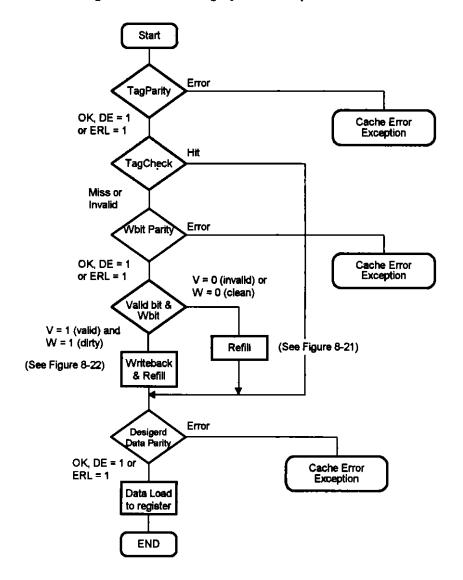

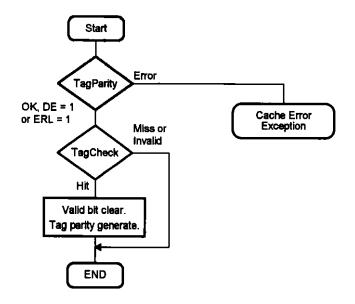

| 8-9           | Data Integrity on Load Operations                       | 155  |

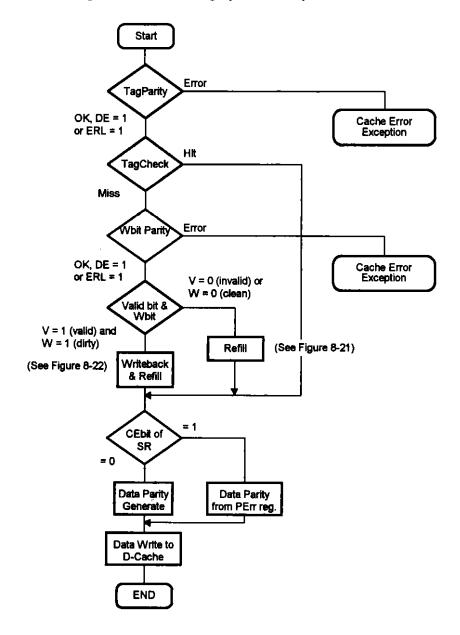

| <b>8-1</b> 0. | Data Integrity on Store Operations                      | 156  |

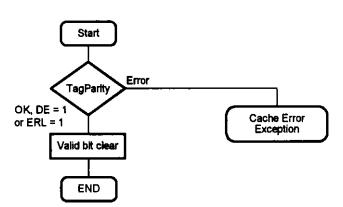

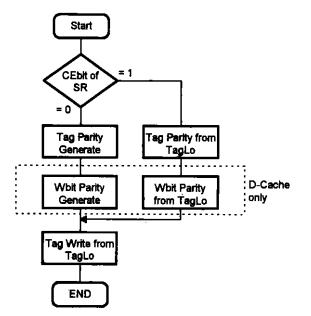

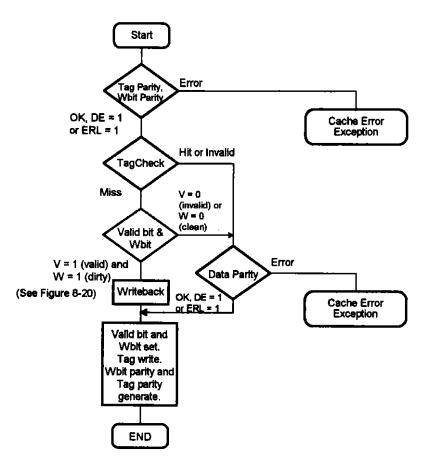

| <b>8-11</b> . | Data Integrity on Index_Invalidate Operations           | 157  |

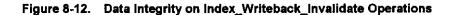

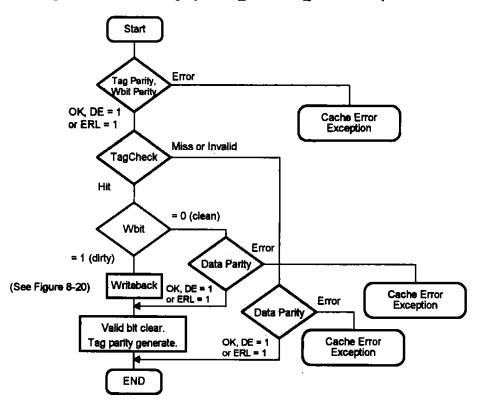

| <b>8-12</b> . | Data Integrity on Index_Writeback_Invalidate Operations | 157  |

| 8-13.         | Data Integrity on Index_Load_Tag Operations             | 158  |

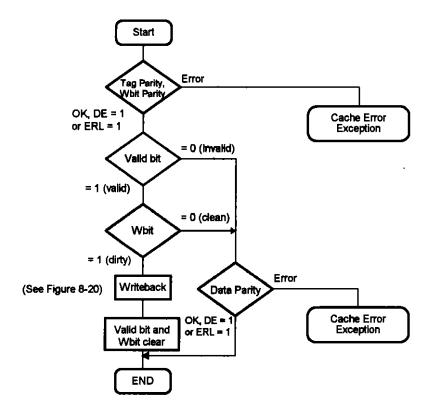

| 8-14.         | Data Integrity on Index_Store_Tag Operations            | 158  |

| 8-15.         | Data Integrity on Create_Dirty Operations               | 159  |

| 8-16.         | Data Integrity on Hit_Invalidate Operations             | 159  |

| 8-17.         | Data Integrity on Hit_Writeback_Invalidate Operations   | 160  |

| <b>8-</b> 18. | Data Integrity on Fill Operations                       | 160  |

| 8-19.         | Data Integrity on Hit_Writeback Operations              | 161  |

| 8-20.         | Data Integrity on Writeback Flow                        | 162  |

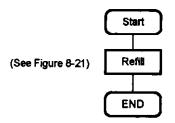

| 8-21.         | Data Integrity on Refill Flow                           | 162  |

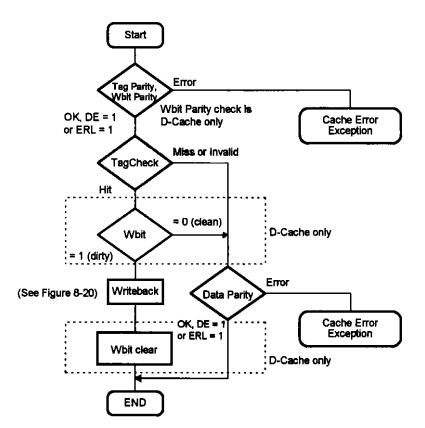

| 8-22.         | Data Integrity on Writeback & Refill Flow               | 163  |

# LIST OF FIGURES (4/8)

| Fig. No.           | Title                                                                               | Page |

|--------------------|-------------------------------------------------------------------------------------|------|

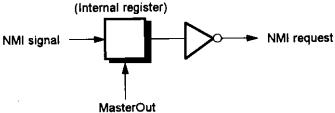

| 9-1.               | Nonmaskable Interrupt Signal                                                        | 165  |

| <b>9-2</b> .       | Hardware Interrupt Signals                                                          | 167  |

| <b>9-3</b> .       | Masking of the CPU Core Interrupts                                                  | 168  |

| 10-1.              | BCUCNTREG (0x0B00 0000)                                                             | 170  |

| 10-2.              | BCUBRREG (0x0B00 0002)                                                              | 171  |

| 10-3.              | BCUBRCNTREG (0x0B00 0004)                                                           | 172  |

| 10 <del>-4</del> . | BCUBCLREG (0x0B00 0006)                                                             | 173  |

| 10-5.              | BCUBCLCNTREG (0x0B00 0008)                                                          | 174  |

| 10-6.              | BCUSPEEDREG (0x0B00 000A)                                                           | 175  |

| 10-7.              | BCUERRSTREG (0x0B00 000C)                                                           | 177  |

| 10-8.              | BCURFCNTREG (0x0B00 000E)                                                           | 178  |

| 10-9.              | PREVIDREG (0x0B00 0010)                                                             | 179  |

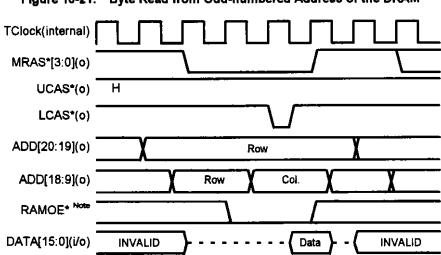

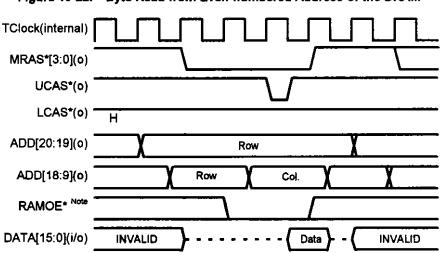

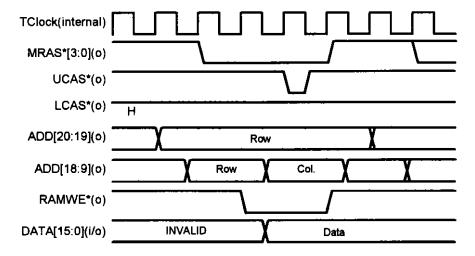

| 10-10.             | ROM 4-Byte Read (WROMA[2:0] = 110)                                                  | 191  |

| <b>10-11</b> .     | Page-ROM 4-Byte Read (WROMA[2:0] = 110, WPROM[1:0] = 01)                            | 192  |

| 10-12.             | Flash Memory 2-byte Access                                                          | 193  |

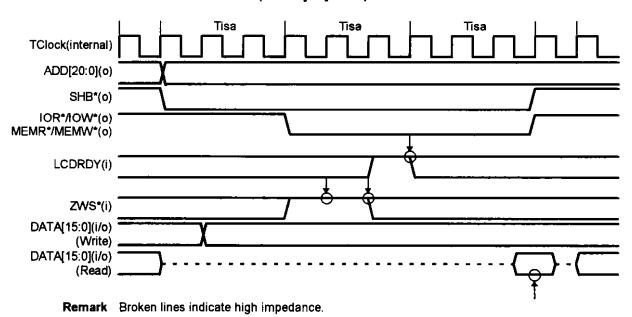

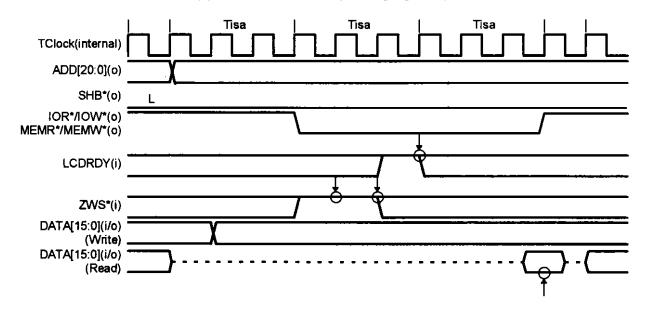

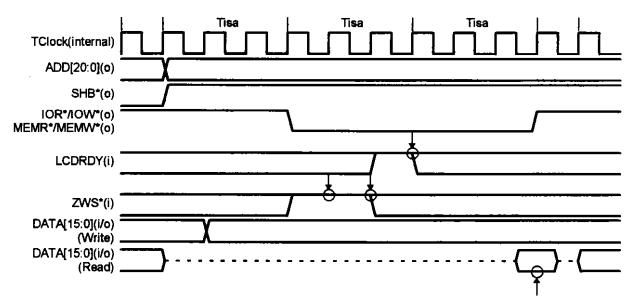

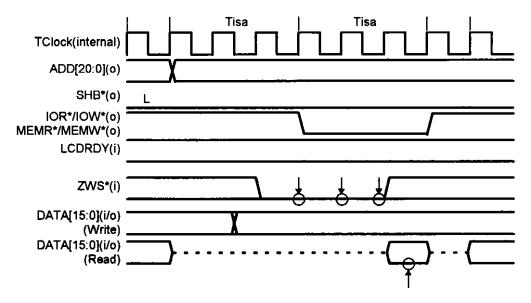

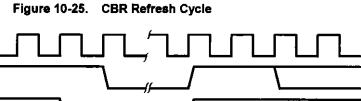

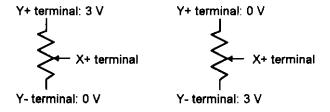

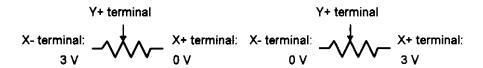

| 10-13.             | Two-Byte Access in the Case Where the LCDRDY High Level Is Sampled                  | 195  |