# Algorithmics P-4032 User's Manual

© 2000 Algorithmics Ltd

Revision: 2.5 Dated: 1999/08/17

P-4032 is a single board computer for prototyping and evaluating 32-bit MIPS R4x00 CPUs like NEC's Vr4300, IDT's R4640 or QED's RM5230 CPU for your application. It's fast, efficient, and economical, with excellent software support, and the design can be licensed in whole or in part.

We all know that you only read the manual if all else fails. But can we at least recommend that you read §1.1, "Key facts for the impatient" and §2, "Getting Started". This manual is ©1996,97,98 Algorithmics Ltd, but anyone may reprint this document in whole or in part, so long as this copyright message is preserved.

Algorithmics Ltd 3 Drayton Park London N5 1NU ENGLAND. Phone: +44 71 700 3301 Fax: +44 71 700 3400 Email: ask-algor@algor.co.uk WWW: http://www.algor.co.uk/ FTP: ftp://ftp.algor.co.uk/pub/

## Contents

| Contents                                                  | 3  |

|-----------------------------------------------------------|----|

| 1. Introduction to the P-4032                             | 7  |

| 1.1. Key facts for the impatient                          | 7  |

| 1.2. P-4032 evolution                                     | 7  |

| 1.3. Features                                             | 7  |

| 1.4. Block Diagram                                        | 9  |

| Figure 1.1 P–4032 block diagram                           | 9  |

| Notes on the block diagram                                |    |

| 1.5. A note on EMC                                        | 10 |

| 2. Getting started                                        | 11 |

| 2.1. What's in the box?                                   | 11 |

| 2.2. Initial wiring up                                    | 11 |

| 2.3. Boxing a P-4032                                      | 11 |

| 2.4. Normal sign-on sequence and what it means            |    |

| Table 2.1: P–4032 ROM sign-on sequence                    |    |

| Startup troubleshooting and switch flipping               |    |

| 2.5. Flash memory and ROM socket                          |    |

| 2.6. PMON                                                 |    |

| The environment store                                     |    |

| Table 2.2: P-4032 - typical PMON environment variables    |    |

| Instant PMON                                              | 15 |

| 3. Memory map                                             | 16 |

| 3.1. R4x00 addressing - program and physical addresses    | 16 |

| Figure 3.1 MIPS program address map                       | 16 |

| Figure 3.2 MIPS program address map (entire 64-bit space) | 17 |

| 3.2. Physical memory map                                  |    |

| Table 3.1: P–4032 physical address map                    | 19 |

| 4. Processor and options                                  | 20 |

| 4.1. Clock rate/Clock rate multiplier                     |    |

| 4.2. CPU daughterboard                                    |    |

| 4.3. Endianness                                           | 20 |

| 5. Local memory                                           | 22 |

| 5.1. DRAM configuration                                   |    |

| Modules and mixes supported                               | 22 |

| Jumper configuration for DRAM type/speed                  | 23 |

| Figure 5.1 Software option jumper J22 (DRAM bits)         | 23 |

| Table 5.1: Configuring SIMM module types                  | 23 |

| DRAM Configuration register                               |    |

| Table 5.2: DRAM configuration register fields             |    |

| How to size the DRAM                                      |    |

| Table 5.3: How CPU addresses reach the DRAM SIMMs         |    |

| Outcomes of out-of-range memory accesses                  |    |

| 5.2. 8-bit ROM                                            | 25 |

| Notes about writing to P-4032's flash PROM              | 26      |

|---------------------------------------------------------|---------|

| 5.3. Serial EEPROM                                      | 27      |

| Table 5.4: EEPROM signals and GPIO pins                 |         |

|                                                         |         |

| 6. PCI interface                                        |         |

| 6.1. PCI accesses                                       |         |

| 6.2. PCI wiring                                         |         |

| Table 6.1: IDSEL for PCI devices/slots                  |         |

| Table 6.2: PCI arbitration signals for devices          |         |

| 6.3. PCI interface registers                            |         |

| 6.4. PCI startup                                        |         |

| •                                                       |         |

| 6.5. PCI performance notes                              | 29      |

| 7. Ethernet interface (DEC 21041)                       | 30      |

| 8. SCSI interface (Symbios 53C810)                      | 31      |

|                                                         |         |

| 9. Onboard I/O                                          |         |

| 9.1. Board configuration register                       | 32      |

| Table 9.1: Board configuration register fields          | 32      |

| 9.2. Option register                                    |         |

| Figure 9.1 Option header/register (J22)                 | 33      |

| 9.3. Design revision register                           |         |

| 9.4. Combination RS232/centronics/diskette interface    | 34      |

| 9.5. Dual UARTS                                         |         |

| 9.6. Centronics                                         |         |

| Table 9.2: Centronics connections in "peripheral" mode  |         |

| 9.7. Diskette interface                                 |         |

| 9.8. Real Time Clock (RTC)                              |         |

| 9.9. General-purpose parallel I/O (PIO)                 |         |

| Table 9.3: Parallel I/O bits and onboard functions      |         |

| 9.10. LED or LCD display                                |         |

| LED display                                             |         |

|                                                         |         |

| Figure 9.2 Alphanumeric Display Extended Character Set  |         |

| LCD display                                             | -       |

| 9.11. PC keyboard controller                            |         |

| 10. The Interrupt system                                | 38      |

|                                                         |         |

| Figure 10.1 Interrupt system block diagram              |         |

| Table 10.1: Interrupt register addresses                |         |

| Table 10.2: Interrupt sources                           |         |

| Table 10.3: Interrupt assignments for PCI devices/slots |         |

| Figure 10.2 Interrupt register bit fields               |         |

| Notes on the interrupt registers                        | 41      |

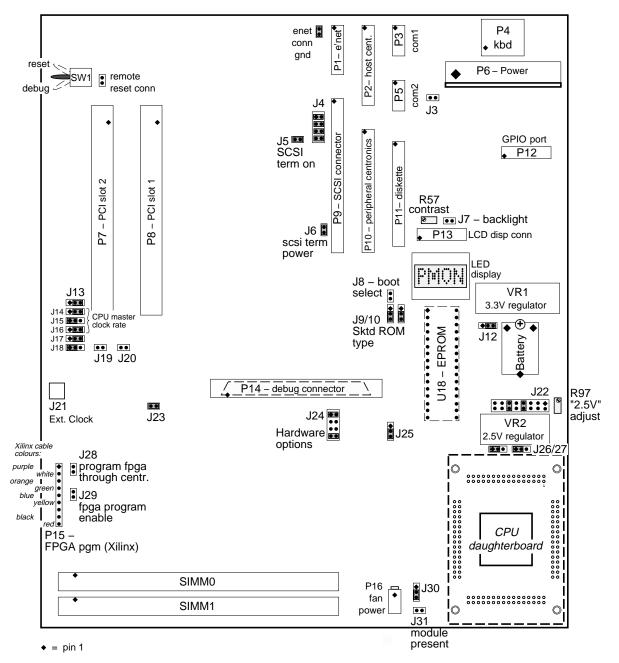

| 11. P-4032 layout and user-selectable options           | 10      |

| Figure 11.1 Board layout and jumper defaults            |         |

| 11.1. Notes on Figure 11.1.                             |         |

| 11.2. CPU options - newer boards                        |         |

| 11.3. CPU options - older boards                        |         |

|                                                         | ·····+J |

| 11.4. Jumper options                                                         | 43 |

|------------------------------------------------------------------------------|----|

| Figure 11.2 Hardware option jumper (J24) positions                           | 43 |

| CPU adaptation options                                                       |    |

| PCI clock source                                                             | 45 |

| CPU system interface clock frequency                                         |    |

| Table 11.1: CPU clock rate setup                                             |    |

| ·····                                                                        |    |

| 12. CPU endianness                                                           | 46 |

| 13. Connectors and cables                                                    | 48 |

| 13.1. Cables supplied                                                        | 48 |

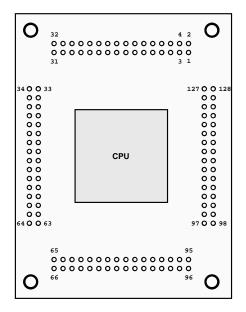

| 13.2. CPU daughterboard connector                                            | 49 |

| Figure 13.1 CPU daughterboard layout                                         | 49 |

| Table 13.1: Pinout of CPU daughterboard (MIPS names)                         |    |

| 13.3. SIMM memory slots (SIMM0/SIMM1)                                        |    |

| 13.4. PCI edge connectors (P8/P7)                                            |    |

| 13.5. Ethernet (P1)                                                          |    |

| Table 13.2: Ethernet connector (P1) pinout                                   |    |

| 13.6. SCSI (P9)                                                              |    |

| Table 13.3: SCSI connector (P9) pinout                                       |    |

| 13.7. RS232 (P3/P5)                                                          |    |

| Table 13.4: Serial connector (P3/P5) pinout                                  |    |

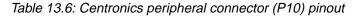

| 13.8. Centronics (P2/P10)                                                    |    |

| Table 13.5: Centronics host connector (P2) pinout                            |    |

| Table 13.6: Centronics peripheral connector (P10) pinout                     |    |

| 13.9. Diskette (P11)                                                         |    |

| 13.10. User-defined parallel I/O (P12)                                       |    |

| Table 13.7: General purpose I/O connector (P12) pinout                       |    |

| 13.11. PC-compatible keyboard (P4)                                           |    |

| 13.12. LCD display connector (P13)                                           |    |

| Table 13.8: LCD display header (P13) pinout                                  |    |

| 13.13. Power supply connector (P6)                                           |    |

| Table 13.9: Power connector pinout                                           |    |

| 13.14. 12V fan power (P16)                                                   |    |

| 13.15. Logic programming connector (P15)                                     |    |

| Figure 13.2 Xilinx-compatible connector (P15) for reprogramming P–4032 logic |    |

|                                                                              |    |

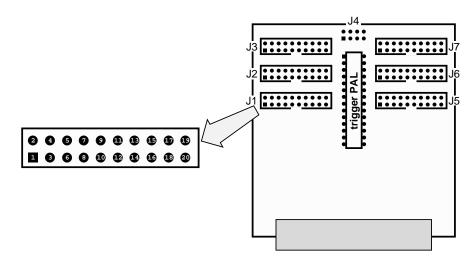

| 14. Logic analyser (debug) board                                             |    |

| Figure 14.1 DBG–4 - P–4032's debug board                                     |    |

| Table 14.1: Signals from DBG–4                                               |    |

| Figure 14.2 Connecting an HP or compatible analyser to DBG-4                 |    |

| Figure 14.3 Pin-by-pin analyser connection to DBG–4                          |    |

| 14.1. DBG-4 option header (J4)                                               |    |

| Figure 14.4 The J4 option header - pins                                      |    |

| Reprogramming the ANTRIG PAL                                                 |    |

| 14.2. Pinout of debug connector (P14)                                        |    |

| Table 14.2: Debug connector signal description                               |    |

| Table 14.3: Debug connector (P14) pinout                                     | 61 |

| Appendix A: References and further reading                                   | 60 |

|                                                                              |    |

| CPU variants                 | information62 |

|------------------------------|---------------|

|                              |               |

|                              | nanuals62     |

| Other software               |               |

| Data sheets62                |               |

| Standards                    |               |

| Appendix B: Software support | are support64 |

| SDE-MIPS for P-4032          | P-4032        |

| Real-time OS on P-403264     | on P–403264   |

| Other OS on P-403264         | 9–4032        |

## 1. Introduction to the P-4032

## **1.1.** Key facts for the impatient

If you know quite a lot about MIPS already, and are familiar with programming at a low level, you'll still need the following parts of this manual:

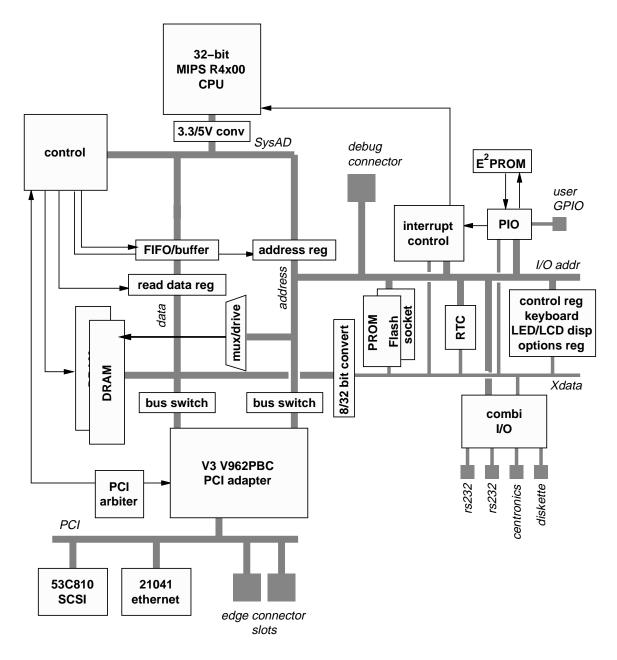

- *Block Diagram*: you'll probably find it helpful to glance at Figure 1.1 on page 9.

- *Memory map*: refer to Table 3.1 to find out what registers are where.

- Physical arrangement, connectors and jumpers: described in §11 on page 42 below.

- *Board-specific programming*: no matter how familiar you are with the devices we've used, to program the board from scratch you'll need to know about the board configuration register, described in §9.1 on page 32.

## 1.2. P-4032 evolution

Early P–4032's were fitted with either an NEC Vr4300-133 or IDT R4640 CPU as a build-time option. More recent boards (built since January 1997, serial number 1000-) provide for the QED RM5230 CPU onboard and have a daughterboard interface for other choices.

This manual specifically describes the third revision of the daughterboard-ready P–4032. The hardware of this board has been fairly extensively redesigned, because the programmable logic device we used in early boards had become obsolete (thank you, Altera). However, apart from the loss of a couple of connectors which were really customer-specific, these changes should not affect use or programming of the board.

## 1.3. Features

• *Processor*: any of QED's RM5230/31, NEC Vr4300/4310 or IDT's R4640 CPU running at a system interface speed of 50, 60 or 66MHz. When we want to refer to any CPU we'll call it R4x00.

These CPUs can be configured to run at a multiple of the system interface speed - usually twice. The CPU has 64 bit registers and a complete 64-bit instruction set, but uses a 32-bit external bus interface to save cost and power.

Early P–4032 boards have positions for either a Vr4300 or R4640 CPU; recent variants bear the name "P–4032Q" and accept either an RM5230/31 soldered down or a CPU daughterboard. Daughterboards are available for the NEC Vr4300, IDT R4640, and RM5230/31 (for customers who want to be able to change their CPU).

The CPUs are fairly compatible, but there are software-visible differences:

- Vr4300 100% compatible with earlier R4x00 CPUs; 16K I-cache and 8K D-cache, both direct mapped. Floating point and integer pipelines combined, which slows floating point operations somewhat but saves power and space.

- R4640 Less compatible (lacks double-precision floating point, no hardware memory management); 8K I- and D-caches, 2-way set associative with locking options. It features an integer multiply-accumulate instruction, useful for some DSP-like algorithms.

RM5230/31

upward compatible with everything including the R5000 and a full MIPSIV instruction set. 16K I- + 16K D-cache (double size on '31), 2-way set associative. Includes R4640-compatible multiply-accumulate.

Vr4100 low-power CPU likely to be used mostly as an ASIC core. No floating point hardware, small caches, much slower. The hardware interface is rather different, and it will be

difficult for customers to reconfigure P–4032 between Vr4100 and other CPUs. In fact, there may be no Vr4100 support available in later boards; check with Algorithmics.

• Local Memory: supports one or two industry-standard 72-pin SIMMs. Any standard EDO or page-mode 32-bit module can be used - including 32-bit flash ROM modules if you want to prototype a ROM-based application.

The size and type of memory is user-configurable. The maximum theoretically achievable memory size is 256Mbytes, and is 128Mbytes with modules available in early 1996.

- *Boot ROM*: supports both socketed conventional EPROM and flash PROM for economical, field-upgradeable bootstrap.

- *PCI expansion bus*: is PCI2.1 compatible<sup>1</sup>, 33MHz, 32-bits wide. There are two PC-standard 5V edge connector sockets.

- *Ethernet*: implemented with the DEC 21041 controller, attached onboard via the PCI bus.

- *High-performance SCSI interface*: using an onboard Symbios 53C810 controller, is available for local disk or tape devices, or customer-specific SCSI peripherals.

- *PC-compatible I/O*: a combination I/O controller provides dual serial ports (16550 compatible), bidirectional Centronics and a diskette interface. The Centronics port can play the role of a "peripheral" to your PC host, or a host to your printer or other peripheral.

So the board can talk to you when all else fails, there's a 4-character alphanumeric LED display used by the boot ROM and other code which likes it. To bridge the software/hardware gulf there's a general purpose parallel I/O (PIO) connector, which allows you to wiggle or watch any of 8 lines under software control.

And we provide a PC-compatible keyboard controller, real-time clock, and an optional LCD "front panel" display.

- *EEPROM*: a simple serial device provides 4Kbits of non-volatile "environment" storage.

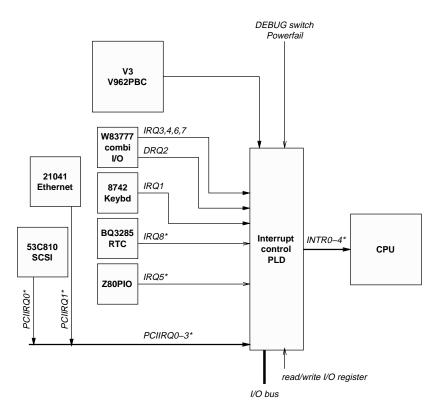

- Interrupt controller: a custom design which can be software-configured to suit a wide range of customer or OS requirements.

- *Field-reconfigurable logic*: most of the board's logic is implemented in re-programmable FPGA devices. We can supply logic upgrades over internet.

- Software support: delivered with the PMON boot monitor [PMON], for which full source code (including all drivers) is available free on request. The standard bootstrap also includes a ROM-based power on self test ("AlgPOST"). Algorithmics SDE-MIPS toolkit [SDE-MIPS] provides a library for P-4032.

Algorithmics can supply BSP ("board support packages") for real-time OS' such as VxWorks from Wind River Systems and pSOS from ISI. Versions of freely-redistributable operating systems (notably OpenBSD and Linux) are available too.

Free software for P-4032 can be found on our internet ftp server at ftp.algor.co.uk.

• *Reset/debug switch*: that little switch (SW1). It can be pushed left (away from the center of the board) for a full reset, and right to produce a "debug" interrupt. The debug interrupt is wired into a regular interrupt, not the *NMI* (non-maskable interrupt), and does interesting things to the boot-up sequence.

8

<sup>&</sup>lt;sup>1</sup> PCI is a fast-moving target; see the online errata for deviations. They don't affect everyday uses.

### 1.4. Block Diagram

Figure 1.1 P-4032 block diagram

#### Notes on the block diagram

• *Buses*: the CPU local bus ("SysAD") is a 32-bit wide, 5V-signalled, multiplexed bus running synchronously at the CPU's interface clock rate - up to 67MHz.

CPU data passes through a write FIFO, allowing CPU cache writeback bursts to run at full speed.

The intermediate bus has a dual personality. During CPU/memory transactions, it runs at CPU interface speed; but during transfers to or from PCI it runs at one-half CPU speed, and with timings compatible to the local bus of an Intel i960 CPU.

- V3 V962PBC: is a local-bus/PCI converter, originally designed for i960 applications.

- *Bus switch*: decouples the PCI converter chip when the intermediate bus is carrying CPU/memory or CPU/local I/O traffic.

- DRAM: two sockets for 32-bit SIMM modules.

- *IO bus and Xdata*: provides an 8-bit bus for onboard PC-type peripherals. The "8/32-bit converter" can steer IO bus data to any byte lane of the read data register; when the CPU reads from the 8-bit ROM space the hardware performs four byte-wide reads and assembles them into a 32-bit word.

## 1.5. A note on EMC

The electronics industry in both Europe and the USA is now concerned with stray emissions (and sensitivity to) electromagnetic radiation. P-4032 is not currently certified under European regulations, because it is not itself a system but only a component<sup>2</sup>. By design, P-4032 is relatively insensitive to incoming radiation; it may be affected by power glitches, but it is the power supply's job to filter those.

Many of you will be using P-4032 open on a bench set up. Use of a 100MHz+ system without any overall metal shielding is likely to produce radiated emissions above the levels permissible for office (let alone domestic) equipment. The European regulations specifically provide for laboratory set-ups, on the basis that it is your responsibility to ensure that no nuisance is caused to a third party. The best shielding is distance; don't set up your board a few feet away from someone else trying to watch TV!

P-4032 is designed to be compatible with widely available "PC" boxes, power supplies and cables, and its radiation will be sharply reduced if those are of good quality. Algorithmics may at some point issue a boxed system product or specification, which would need to be certified and "CE"-marked. Write to us if you need that. Meanwhile, the board is a component for use in laboratory environments, and the user is responsible for managing radiated emissions.

<sup>&</sup>lt;sup>2</sup> There is some debate in Europe about whether all assembled PCBs should be covered by the "CE" registration scheme, but it's still an open question.

## 2. Getting started

Most of you should read this section.

## 2.1. What's in the box?

Everybody should find:

- P-4032 user's manual: but you got that, because you're reading it.

- *PMON user's manual*: describing the boot monitor and startup sequence. A useful reference for when things go wrong, but many of you won't really have much to do with it.

- *P–4032*: configured with the CPU, and the amount and type of memory, you ordered.

- *Transition Cables*: there should be a bunch of standard transition cables, which you can either use to bring out connections for a board in a PC box, or just to mate with standard bought-in cables.

You may also find (if you ordered them):

- *Extra cables*: some are optional, see §13.1.

- *Debug board*: makes it much easier to watch addresses/data in your program. Invaluable for driver and ROM-code debug; see §14 below.

- *LCD display*: an optional 16×2 alphanumeric display supplied loose with a short transition cable. It's up to you to find a mounting point, or just leave it lying around. More information in §13.12.

## 2.2. Initial wiring up

P-4032 is quite happy operating on a bench top. There are no dangerous voltages, and nothing will get too hot. You'll need to connect at least power, and possibly some other stuff.

- *Power*: PC power supplies are cheap, electrically safe, and plug right in. The connector is in two parts, but put the black (ground) wires together and you'll be safe.

- Serial port(s): if the connection from your computer terminates in a female D-type (9-pin for PCs, or 25-pin for old RS232 standard), then there's a good chance that you can wire them up with the supplied cables. If not, or you've lost the cables, refer to Table 13.4 below for the connections on board.

The PROM monitor signs on at 9600 baud, sends 8-bit characters with no parity, and (in its default configuration) accepts pretty much anything back again.

- *Ethernet*: you need an external transceiver. The supplied cable plugs in.

- *Centronics for download*: if you have a normal PC centronics cable then you'll need the centronics peripheral transition cable, which is an optional extra.

## 2.3. Boxing a P-4032

P-4032 is designed to fit into PC metalwork - older rather than "ATX" PCs - and matches a small PC motherboard in its size, fixing hole positions and standard connectors (PCI, keyboard, power supply). PC metalwork varies, so you may need some patience.

The serial and centronics transition cables supplied with the board terminate on PC back-panel fingers. The SCSI cable supplied is suitable for use in-box. You'll need to make your own arrangements for other I/O.

Most PCs have a reset button lead, which will mate with the 2-pin header J2, allowing the board to be reset from the front panel.

## 2.4. Normal sign-on sequence and what it means

From power up your P–4032 will show signs of life by writing enigmatic codes to its LED display (just in case you expected English, it starts by saying "U\*U\*"). At the same time it's sending rather more meaningful messages to both serial ports. Here's a typical example:

| P–4032 says                                                               | What it means                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Info: Version: P4032 (EB) 1.17: (chris) Thu ∖<br>Feb 13 13:35:05 GMT 1997 | PROM sign-on. "(EB)" for big-endian, "(EL)" for<br>little-endian. Note that the PROM contains both<br>the power-on selftest code (AlgPOST) and the<br>ROM monitor (PMON). This is AlgPOST<br>starting up.                                                                      |

| Info: Activity: ICU operation<br>Info: Activity: cache tests              | And the "\" shows where I've folded a single line<br>which is too long for this table.<br>"Info:" denotes a test starting. If you get nothing<br>but "Info" and "Notice" lines from the power-on<br>tests, then they didn't find anything really wrong.<br>Started cache tests |

| Info: Dcache size 8 Kbytes (16/line)                                      |                                                                                                                                                                                                                                                                                |

| Info: Icache size 16 Kbytes (32/line)                                     |                                                                                                                                                                                                                                                                                |

| Info: Activity: dcache refill test                                        |                                                                                                                                                                                                                                                                                |

| Info: Activity: dcache writeback test                                     |                                                                                                                                                                                                                                                                                |

| Info: Activity: RTC operation                                             |                                                                                                                                                                                                                                                                                |

| Info: Date: Fri 25/4/1997 10:38:00 UTC                                    |                                                                                                                                                                                                                                                                                |

| Info: Memory Size 8Mb, Simm0 4Mb SIMM1 4Mb \                              | "DCR" is the hex value of the DRAM                                                                                                                                                                                                                                             |

| DCR 0xdd                                                                  | configuration register, described in §5.1 below.                                                                                                                                                                                                                               |

| Info: Activity: quick memory address test                                 | More thorough tests are available, see PMON manual for how to make them happen.                                                                                                                                                                                                |

| Info: Activity: flash memory operation                                    |                                                                                                                                                                                                                                                                                |

| Info: Flash: Fujitsu 29F080                                               |                                                                                                                                                                                                                                                                                |

| Info: Activity: ns16550 operation                                         | That's the dual serial port controller                                                                                                                                                                                                                                         |

| Info: Activity: keyboard operation                                        |                                                                                                                                                                                                                                                                                |

| Notice: No keyboard attached                                              |                                                                                                                                                                                                                                                                                |

| Info: Activity: PCI operation                                             |                                                                                                                                                                                                                                                                                |

| Info: V962 silicon revision 2                                             | The PCI bridge chip. Revision 2 indicates a<br>"B.1" part, which is not so good. See our web<br>site for bugs inherent in the B.1 chip, and let's<br>hope your board announces a revision of 3 or<br>higher.                                                                   |

| Notice: Integrated Tests Completed                                        |                                                                                                                                                                                                                                                                                |

| Notice: Executing PROM package 6                                          | Control is now being handed over from the<br>power-on tests to PMON.                                                                                                                                                                                                           |

| PCI slot 5: Digital Equipment DECchip 21041 \                             |                                                                                                                                                                                                                                                                                |

| ("Tulip Pass 3") (class: network, $\setminus$                             |                                                                                                                                                                                                                                                                                |

| subclass: ethernet)                                                       | PMON is probing for active PCI devices                                                                                                                                                                                                                                         |

| PCI slot 8: NCR 53c810 (class: mass $\setminus$                           |                                                                                                                                                                                                                                                                                |

| storage, subclass: SCSI)                                                  |                                                                                                                                                                                                                                                                                |

| de0: P4032 DC21041 [10Mb/s] pass 1.1 Ethernet                             | Ethernet driver initialisation.                                                                                                                                                                                                                                                |

| address 00:40:bc:03:00:44                                                 |                                                                                                                                                                                                                                                                                |

| P–4032 says                                           | What it means                                  |  |

|-------------------------------------------------------|------------------------------------------------|--|

| PMON version 3.1.155 [P4032,EB,FP,NET]                | PROM monitor version and date                  |  |

| Algorithmics Ltd. Jan 24 1997 11:46:17                | PROMINION VEISION and date                     |  |

| This software is not subject to copyright $\setminus$ |                                                |  |

| and may be freely copied.                             |                                                |  |

| CPU type R4300. Rev 2.0. 133.3 MHz.                   | From CPU ID register and measurement.          |  |

| Memory size 8 MB.                                     | PMON should agree with AlgPOST                 |  |

| Icache size 16 KB, 32/line.                           | These figures are right for the Vr4300, others |  |

| Dcache size 8 KB, 16/line.                            | differ                                         |  |

|                                                       |                                                |  |

| PMON>                                                 | You've got a prompt                            |  |

Table 2.1: P-4032 ROM sign-on sequence

#### Startup troubleshooting and switch flipping

As the board powers up, the LED shows a code for each set of tests. The display blinks out briefly as each individual test is started.

Lower-case codes are good, but upper case codes from AlgPOST are bad (at least, after it's initial "U\*U\*" stuff). Upper-case test names from AlgPOST mean a warning or worse; always stay around for long enough for you to read them; and are accompanied by a console message unless the console is not working or configured off.

Confusingly, PMON puts upper-case messages on the display and those aren't errors; but they tend to zoom past really fast until you get a gently flashing "PMON" - and that indicates that the system is up to the PMON prompt.

If the board seems to be expiring really early, you may want to turn up the thoroughness and verbosity of the power-on tests. Usually, this is controlled by environment variables; but if you can't reach the PMON prompt you can't change those. So you can do it by wiggling the debug/reset switch; reset the board in the usual way, but instead of releasing the switch move the switch all the way over to its other ("debug") position, and hold it there for a couple of seconds. AlgPOST will now test everything (including some rather tedious memory tests) and tell you pretty much everything about it.

## 2.5. Flash memory and ROM socket

P–4032 normally boots from an onboard 1M×8 flash memory, pre-loaded by Algorithmics with power-on tests and the PMON ROM monitor program. You can create and write your own bootstrap; software running out of DRAM can update the flash memory in place.

If your board won't boot and you believe that the flash memory may be corrupted, there is a socket (U18) which accepts an alternative bootstrap source. The device is usually a  $512K \times 8$  150ns EPROM, in a 32-pin dual in-line package, but you can use a suitable flash part (AMD 29F040 or equivalent), by changing the jumpers J9 and J10 from their default (2–3) position to (1–2).

The board will use the ROM socket for its bootstrap if you insert jumper J8.

A copy of PMON in S-record format, ready to run in your board, can be downloaded from Algorithmics' web site www.algor.co.uk. You can also download a program to run under PMON, which will write a clean bootstrap image to your flash memory.

Flash memory updates are performed through two separate address windows onto the onboard and socketed devices.

### 2.6. PMON

PMON is the bootstrap monitor program supplied in ROM, described much more fully in the "PMON User's Manual" which all board customers should have received. Many users will make use of only a fraction of PMON's facilities:

#### The environment store

The board environment is implemented in an EEROM device separate from the main memory map, and is intended to be shared by any software which wants to store small amounts of per-board configuration information. In PMON you use the "set" command to inspect or create environment entries. To edit existing entries, the "eset" command gives you line editing.

Table 2.2 shows a typical dump of variables from P-4032; we'll explain what they mean.

```

PMON> set

ethaddr = 00:40:bc:03:00:44

itquick = t

netaddr = 192.168.1.67

hostname = comm67.comm.algor.co.uk

nameserver = 192.168.1.65

gateway = 192.168.1.65

tftphost = oval

v = gate:/vol/tornado/target/config/p4032/vxWorks

dlecho = off [off on lfeed]

dlproto = EtxAck [none XonXoff EtxAck]

hostport = tty1

heaptop = 80020000

moresz = 10

prompt = "PMON> "

brkcmd = "l @epc 1"

datasz = -b [-b - h - w - d]

[no sec pri save]

bootp = no

inalpha = hex

inbase = 16

regstyle = sw

[hex symbol]

[auto 8 10 16]

[hw sw]

[32 64]

regstyle = sw

regsize = 32

rptcmd = trace

[off on trace]

trabort = ^K

[cr lf crlf]

ulcr = cr

uleof = %

validpc = "_ftext etext"

```

Table 2.2: P-4032 - typical PMON environment variables

What do all these mean?

- *ethaddr*: Without this, no network. The first part of the address ("00:40:bc:03") is the same for all boards; the last four digits of the hex ethernet number are the board's serial number (but in hex); this board is serial 0068, which is "0044" in hex.

- *itquick*: Suppresses long-running power-on memory tests. See PMON manual for how to ask for more power-on tests.

netaddr, hostname, nameserver: You need either a "netaddr" or both a (suitably registered)

"hostname" and "nameserver" to be set up. Either gives the board an identity for communication.

If you need more information about setting up the network, read the PMON manual.

- *gateway*: default gateway. Network data for any host which is not on the local network (does not respond to ARP request) will be sent here. Useful if you keep your prototype boards on a separate network.

- *tftphost*: default network host to use when using *tftp*. You can always give an explicit host name.

- *v*: a typical programmer-set shortcut, allowing you to just say:

PMON> boot \$v; g

to load and run the program.

- *dlecho, dlproto*: control download over serial or parallel link. P-4032 can echo characters (if the link is bidirectional) or use a character-based flow control protocol.

- *hostport*: select which device is to be used for download. The device can either be shared with the PMON console, or separate. Possible download device names are:

- tty0 is the first serial port, "com1", also used for the PMON console.

tty1 is the second serial port, "com2".

- tty2 is the centronics port, using peripheral mode.

- heaptop: how much DRAM memory PMON uses, starting from zero represented as a MIPS "kseg0" address in hex. This is the lowest address at which you can load your program. You can set "heaptop" somewhat lower; but not to zero (PMON has to have some writable memory to operate in) and PMON may be unable to do some things for you without enough free memory.

- *moresz, prompt*: PMON user interface controls.

- *brkcmd etc*: these variables configure the operation of PMON as a debug monitor, and you'll have to look in the PMON manual for them

#### **Instant PMON**

There's so much more in the PMON user manual, but worth mentioning:

- Command editing: use emacs/unix style keys to move around and edit characters.

- Booting from ethernet: uses the "boot" command from PMON, and loads ELF object files.

- Booting from serial or parallel ports: use the "load" command of PMON, and can accept a variety of download formats such as S-records.

## 3. Memory map

## 3.1. R4x00 addressing - program and physical addresses

In MIPS CPUs the addresses generated by your program<sup>3</sup> are never the same as the physical addresses which come out of the CPU and affect the rest of the system.

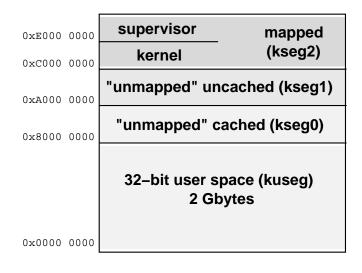

This is different from most familiar CISC architectures, and this often causes confusion. CISC CPUs often have a mode bit which enables memory translation - and without that mode bit set the physical address is exactly the same as the program address. MIPS has no such mode bit. Instead, the CPU' program address space is split into regions, as shown in Figure 3.1:

Figure 3.1 MIPS program address map

The regions *kuseg* and *kseg2* are designated for translation; addresses in these regions will be presented to the hardware's memory translation unit (the *TLB*), and what happens then is beyond the scope of this section. If you want to know more, read an architecture book such as [MIPS R4000] or [Using MIPS].

Embedded software more often runs in *kseg0* and *kseg1*, each of which offers a window onto the low 512Mbyte of physical memory (cached and uncached respectively). *kseg1* is essential to run startup code (before the caches are initialised), and is also needed for access to hardware I/O registers. Once the system is running most system code and data will be accessed through *kseg0*.

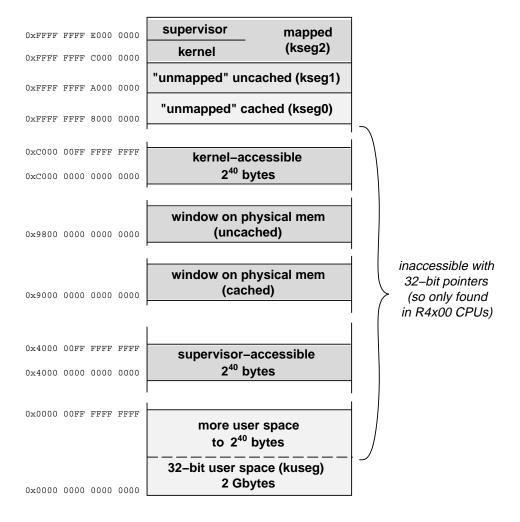

Actually, the picture shown above in Figure 3.1 is not complete. The R4x00 is, after all, a 64-bit CPU and not 32-bits, and the full program address space is 64 bits big. Figure 3.1 is useful because, so long as you only use the 32-bit-compatible part of the MIPS instruction set, registers will only contain 64-bit values whose top 32 bits are all set to the same value as bit 31 - such values look like a "sign extension" of a 32-bit value.

So the 32-bit memory map is in fact the view you get of the whole 64-bit memory map when you leave the middle out. Figure 3.2 shows the big picture:

<sup>&</sup>lt;sup>3</sup> Called *program addresses* here - the term *virtual address* means exactly the same thing but is unfamiliar outside the exotic realms of big operating systems

Figure 3.2 MIPS program address map (entire 64-bit space)

Handling pointers as 64-bit objects is an extravagant use of memory space for an embedded software application; and we reckon most users won't bother. If you need access to the R4x00's 32-bit physical address range outside the low 512Mbytes (so can't just use *kseg0* and *kseg1*) you can use the TLB.

### 3.2. Physical memory map

The CPU generates a 32-bit address. However:

- Following a reset the CPU starts execution at 0x1FC0 0000 (physical) which must therefore map to onboard ROM.

- Much system software finds it easier to operate in the *kseg0* and *kseg1* "unmapped" spaces described above in §3.1, and such programs will only generate physical addresses up to and including 0x1FFF FFFF (the low 512Mbytes of address space).

Note that revisions of this manual before 2.5 describe a different memory map, which turned out to make ISA bus programming difficult. If you wrote software which used the original map, and don't need ISA bus access, the PMON boot monitor will restore the original map if the environment variable "pcimap" is set to "old".

In the memory map Table 3.1 a dagger (†) denotes that the address is software-configured at boot time - the value given is recommended and fits in with the hardware decodings.

| Base<br>Address        | Size   | Class      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------------------------|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0000 0000<br>0400 0000 | 256Mb  | Memory     | onboard DRAM memory<br>Flash SIMM module memory if fitted                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 1000 0000              | 8Mb†   | ISA        | "ISA" memory access window.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                        |        | via<br>PCI | This is a window on the first 8Mbytes of PCI memory space, and should not be allocated to either onboard or add-in PCI controllers.                                                                                                                                                                                                                                                                                                                                                               |  |

|                        |        |            | It's there because some PC legacy controllers - particularly video cards - are hard-wired to respond to some low addresses.                                                                                                                                                                                                                                                                                                                                                                       |  |

| 1080 0000              | 8Mb†   |            | Reserved. This range of memory, as decoded on the PCI bus, provides an unmapped window onto local memory. If the MIPS CPU accessed these locations nothing very useful would happen - the self-decode obstructs access to the ISA bus                                                                                                                                                                                                                                                             |  |

| 1100 0000              | 112Mb† |            | Window on PCI memory space (by default, generates addresses 0x1000 0000<br>lower on the PCI bus). PCI devices get dynamically allocated addresses starting<br>at PCI address 0x0100 0000 which is CPU address 0x1100 0000 Although<br>PCI devices' base addresses are programmable, you should normally leave them<br>where the bootstrap program left them. Find a particular device by reading PCI<br>configuration space and getting the values already programmed into the base<br>registers. |  |

| 1800 0000              | 109Mb  | PCI        | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| led0 0000              | 1Mb    |            | PCI I/O space window†: you'll only use PCI I/O space for PC "legacy" controllers, but this space is reserved for it if needed.                                                                                                                                                                                                                                                                                                                                                                    |  |

| 1ee0 0000              | 1Mb    |            | PCI configuration space: access to PCI devices' configuration registers. In P–4032, PCI device <i>IOSEL</i> signals are derived from high PCI bus address bits see §6.2. ("PCI wiring") on page 28 for details. You need to program some V962PBC registers to make this work.                                                                                                                                                                                                                     |  |

| lef0 0000              | 64Kb†  | V962PBC    | PCI controller's internal registers                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 1ef1 0000              |        |            | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| lfc0 0000              | 1Mb    |            | Boot ROM location. Reads either ROM socket (512Kb only) or flash locations, depending on configuration)                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 1fd0 0000              | 512Kb  | ROM        | Programming window for socketed flash memory                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 1fe0 0000              | 1Mb    |            | Programming window for onboard flash.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 1ff0 0000              | 1 reg  |            | Real time clock "pointer" register                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 1ff0 0004              | 1 reg  |            | Real time clock data                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 1ff1 0000              | 2 reg  | PC-type    | Keyboard controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 1ff2 0010              | 4 reg  | I/O        | LED display cells (leftmost has lowest address)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 1ff3 0000              | x reg  |            | LCD display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 1ff4 0000              | x reg  |            | General-purpose parallel I/O (GPIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 1ff8 07c0              | x reg  |            | Diskette port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 1ff8 0800              | -      | Combi      | unused (Games port)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 1ff8 0be0              | x reg  | I/O        | com2 serial port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 1ff8 0fe0              | x reg  | chip       | com1 serial port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 1ff8 0de0              | x reg  |            | Centronics port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 1ff9 0000              | 3 reg  | ICU        | Interrupt requests/masks                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 1ff9 000c              | 3 reg  |            | Interrupt crossbar registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Base<br>Address | Size    | Class   | Description                                                                     |  |

|-----------------|---------|---------|---------------------------------------------------------------------------------|--|

| 1ff9 001c       | 1 reg   | Ver     | P–4032 design revision                                                          |  |

| lffa Ofd4       | 1 reg   |         | Diskette "DMA acknowledge"                                                      |  |

| 1ffb 0000       | 8×1-bit | PC-type | Board configuration register (1 bit/location)                                   |  |

| 1ffc 0000       | 8×1-bit | I/O     | DRAM configuration register (1 bit/location)                                    |  |

| 1ffd 0000       | 1 reg   |         | Option register                                                                 |  |

| 2000 0000       | 3.5Gb   | PCI     | Use this if you have to (you'll need to program the TLB or use 64-bit pointers) |  |

Table 3.1: P-4032 physical address map

## 4. Processor and options

## 4.1. Clock rate/Clock rate multiplier

The CPU's input clock is derived from a synthesiser IC and is set by a group of jumpers summarised in Table 11.1; likely choices are 50, 60 and 67MHz.

The CPU runs internally at a higher speed (2, 3, 4 or 5 times higher) than the system clock, according to the setting of the "CDIV" field of the jumper J22, described in §9.2. ("Option register") on page 33. Most often, the CPU will run at at  $2 \times$  or  $3 \times$  the bus speed.

## 4.2. CPU daughterboard

Recent boards (serial 1000-) accept a wide range of CPU types, mounted on a small daughterboard. Daughterboards are available for Vr4300, R4640, and RM5230/31. The daughterboard connector is described in §13.2 below, and may be a useful place for looking at raw CPU signals.

The idea of the daughterboard is so we can configure and ship boards with a range of CPUs. We don't want to expose the CPU connector as an "open" interface, because the documentation job would be way beyond cost-effective. Customers who want to be able to switch between two different CPUs should contact Algorithmics for instructions.

But we can tell you that changing a CPU will involve some or all of the following:

- Change the daughterboard itself.

- Change the system logic, which is stored in "flash"-programmable logic chips and can be downloaded through the Centronics port using software and files obtained from Algorithmics' web site.

Some pairs of CPUs (eg. R4640 and RM5230) share a common set of logic, and you may just need to change a jumper.

• Change the CPU input clock rate by changing the clock control jumpers.

## 4.3. Endianness

All MIPS CPUs can be configured with either "endianness" - if you're not sure what this means look at §12. ("CPU endianness") on page 46. With the exception of certain hand-crafted simple sequences, program binaries for big- and little-endian MIPS are different and incompatible; so you have to match the CPU configuration with the software you're running.

On P-4032 there are three pieces of hardware to configure:

• The CPU itself. The NEC Vr4300 is setup in software (it starts up big-endian, but changes sex with an internal register bit). Other CPUs require some kind of reset-time hardware sequence.

The CPU's endianness is set with the "BigEnd" jumper in the option register jumper block, described in §9.2. ("Option register") on page 33. It is always software-readable.

• The CPU bus interface, which interprets the CPU's read and write commands. Partial-word read/writes are signalled by the CPU in an endianness-dependent way.

The CPU bus interface is set up by software, responding to a bit in the configuration register described in §9.1 below. It's initially little-endian, so big-endian CPUs must set this bit before attempting any partial-word accesses.

• The PCI bus interface. PCI is inherently little-endian, and it's wise to have a byte lane swapper between PCI and the rest of the system when the CPU is big-endian.

The V962PBC bridge chip provides a software-selectable byte lane swapper.

Of course, you also have to provide software (including a boot ROM) for the appropriate endianness. The standard boot ROM will detect a mismatch between CPU and ROM endianness and give you a diagnostic

message.

Note that getting even this minimal ROM code to operate bi-endian requires that P-4032 be wired so that CPU instructions (and 32-bit loads and stores) are consistently interpreted regardless of the state of any of the above.

Note again: if the CPU and bus interface options don't match, partial-word transfers will transfer garbage.

## 5. Local memory

## 5.1. DRAM configuration

You can fit one or two 72-pin, 36-bit wide DRAM SIMMs - as used on most PCs. If you only have one SIMM, it goes in SIMM0. If you are using a DRAM-compatible flash memory SIMM, it goes in SIMM1.

P-4032 handles a wide range of memories (size, type and speed). The most common options are software selectable; larger sizes and more unusual DRAM types require a logic firmware variant; contact p4032@algor.co.uk.

#### Modules and mixes supported

With the standard decoding logic you can use single-bank or double-bank SIMM memory modules in sizes of  $1M\times32$ ,  $2M\times32$ ,  $4M\times32$  and  $8M\times32$  - the last must be a double-bank type. If you use two double-sided DRAM modules they must be the same size.

You can use 70ns fast page mode or 60ns EDO modules; if two modules are fitted they must be of the same type (a 60ns EDO will work with page mode timings, but slower).

You can fit a flash SIMM module (1M×32 or 2M×32 double-banked) in the second slot.

- DRAM size: some decoding changes are required to accommodate different sizes of DRAM SIMM, and a range of common options can be setup by programming a set of write-only registers, documented below. Algorithmics' startup code figures out the sizes of the installed modules and configures the DRAM controller accordingly.

- DRAM speed and type: P-4032 supports several different DRAM timing sets. The timing is configured under software control by the DRAM configuration register (defined in §5.1 below); but to avoid confusion software should always initialise the DRAM controller as instructed by the "Mem Type" and "Flash SIMM" fields of the option register, described in §9.2. ("Option register") on page 33 below.

All timings are configured in CPU system interface clock cycles. The options are:

- 1. Fast page mode DRAM with 1-clock CAS (suitable for 50MHz system with 60/70ns DRAMs).

- 2. 60ns EDO DRAM with 1-clock CAS (for system at any speed).

There was to be a "burst" system, which would give the best memory performance achievable with our SIMM pinouts; but it has never been implemented.

- 3. Fast page mode DRAM with 2-clock CAS (required for 67MHz system).

- 4. Flash ROM curious SIMM parts using multiplexed addressing. Initial access time is similar to 80ns DRAM, but CAS cycling is much slower.

If flash ROM is fitted, it's base address is always 64Mbytes (0x0400 0000).

#### Jumper configuration for DRAM type/speed

Figure 5.1 Software option jumper J22 (DRAM bits)

In Algorithmics' startup code the configuration bits relating to the type and speed of the SIMM modules are copied from the "software option" jumper block to a write-only configuration register on power up. The jumper positions are shown in Figure 5.1.

So long as this convention is maintained the links need to be set up to match the installed SIMM modules, as shown in Table 5.1.

| Jumper<br>Name | in/<br>out |           | Effect                    |

|----------------|------------|-----------|---------------------------|

| Slow           | in         |           | 70ns DRAM on 67MHz system |

|                | J22 13-14  | J22 11-12 |                           |

|                | out        | out       | reserved                  |

| DRAM type      | out        | in        | regular EDO               |

|                | in         | out       | reserved                  |

|                | in         | in        | fast page mode            |

| Flash SIMM     | in         |           | Flash ROM module in SIMM1 |

Table 5.1: Configuring SIMM module types

### **DRAM Configuration register**

Implemented as an array of single-bit registers. This is a bit odd - but you don't expect to change it very often.

In Table 5.2:

• *BankSz*: bank size of the memory array plugged into SIMM0. Accesses at and beyond "BankSz" will either go to SIMM1 (single-banked module in SIMM0) or the second bank on SIMM0.

If SIMM1 is single-banked, then the hardware doesn't need to know it's size; it extends all the way up to the maximum DRAM address space limit. The software sizing routine can figure out what it really is.

But if SIMM1 is double-sided, the hardware has to know when to switch to the second bank; and under these circumstances SIMM1 is assumed to have the same bank size as SIMM0.

• *Sngl0/Sngl1*: set 0 if the memory array in SIMM0/SIMM1 respectively has two separate 32-bit banks using four separate *RAS*\* signals.

| Offset       | name           | Value                                                                                                              | Effect                                                                                                                                                              |

|--------------|----------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x1c         | Flash SIMM     | 1=DRAM, 0=flash                                                                                                    | 0 if SIMM1 module is a flash<br>ROM module                                                                                                                          |

| 0x18<br>0x14 | DRAM<br>type   | <ul> <li>0 = Page mode DRAM</li> <li>0 1 = reserved</li> <li>1 0 = regular EDO</li> <li>1 1 = reserved.</li> </ul> | Select type of DRAM in use                                                                                                                                          |

| 0x10         | Slow           | 1=normal, 0=slow                                                                                                   | Set "slow" for 70ns DRAM in a 67MHz system                                                                                                                          |

| 0x0c         | Sngl1          |                                                                                                                    | SIMM1/SIMM0 module "double                                                                                                                                          |

| 0x08         | Sngl0          | 1=single, 0=double                                                                                                 | banked" - it has a second bank of DRAM on the module, accessed by alternate <i>Ras*</i> signals                                                                     |

| 0x04<br>0x00 | Bank<br>Size 0 | <ul> <li>0 0 = reserved</li> <li>0 1 = 4 Mbyte</li> <li>1 0 = 8 Mbyte</li> <li>1 1 = 16 Mbyte</li> </ul>           | Bank size of SIMM0 module. For<br>single-bank modules, this is the<br>same as the module capacity; for<br>double-bank modules, it's half of<br>the module capacity. |

Table 5.2: DRAM configuration register fields

• *Slow*: set 0 to slow the DRAM access speed down, when using 70ns DRAM in a 67MHz system.

A 67MHz CPU's burst read timing (for cycles not delayed by external access or DRAM refresh) are as follows:

| DRAM type      | Access rate |

|----------------|-------------|

| 70ns page mode | 8-3-3-3     |

| 60ns EDO       | 7-2-2-2     |

#### How to size the DRAM

How should you establish how much memory of what type is fitted, in order to program the controller to talk to it? First of all, look at Table 5.3, which shows how CPU addresses are fed to the DRAM SIMMs in the different sizes:

| Туре   | DRAM address | RAS-time  | CAS-time    | Bank      |

|--------|--------------|-----------|-------------|-----------|

| Type   | row+column   | bits      | bits        | size(s)   |

| 1M×32  | 10+10        | A12-21    | A2-11       | 4Mbyte    |

| 2M×32† | 10+10        | A12-21    | AZ-11       | 2×4Mbyte  |

| 2M×32  | 11+10        | A12-22    | A2-11       | 8Mbyte    |

| 4M×32  | 11+11        | A12-22    | AD 11 00    | 16Mbyte   |

| 8M×32† | 11+11        | A12-22    | A2-11,23    | 2×16Mbyte |

| 8M×32  | 12+11        | A12-22,24 | A2-11,23    | 32Mbyte   |

| 16M×32 | 12+12        | A12-22,24 | A2-11,23,25 | 64Mbyte   |

|        |              |           |             |           |

Table 5.3: How CPU addresses reach the DRAM SIMMs

Some  $2M \times 32$  and  $8M \times 32$  modules (marked with †) use separate *Ras*\* signals to access two banks of RAM on the same module. We call these "double-banked" - they are often physically double-sided, with chips on both sides of the module.

Startup code is expected to figure out whether each of the SIMM modules is double-sided, and their bank sizes.

To sense what size banks you have, set up the board for the *maximum* DRAM size, and for single-bank operation. If the real SIMMs are in fact smaller than the maximum size some address bits will get lost and you will see the memory "wrap around".

The wraparound will happen at the first location which is too big for the actually-installed DRAM.

Once you've discovered and configured the bank size, set the double-bank configuration bit. If the SIMM module is single-banked, you'll now get a "hole" above the good bank addresses in which no DRAM will respond. Take care not to get confused by "ghost" data, returned when a floating bus holds the value you last wrote (see the note on "Outcomes of out-of-range memory accesses" below).

A Flash SIMM module is always accessible from 64Mbytes ( $0 \times 0400 \ 0000$ ) and, if double-sided, is assumed to have 4Mbyte banks.

Now repeat the process for SIMM1. The only irritation is that you can't (yet) support a different bank size for SIMM0 and SIMM1 when SIMM1 is double-banked.

A good algorithm for sizing a bank is:

- Set the word at the bank's base address *Base* to some recognizable pattern such as 0x1234 5678.

- For each *n* which is a plausible size for the SIMM memory size (starting with the *largest* value) set the word at physical address *Base* + *n* to the value *n*. The easiest way to generate the physical address is to use the kseg1 address *Base* + n +  $0 \times a000 \quad 0000$ .

Plausible sizes start at 1Mbyte, and go up in multiples of 4.

• Read the word at physical address zero (ie 0xa000 0000) to obtain the size of the SIMM in bytes.

#### Outcomes of out-of-range memory accesses

The memory controller responds to any access in the region dedicated to "onboard DRAM memory". An access to any part of the region for which DRAM is not configured and installed may result in any of the following:

- Random data returned: the data returned is unpredictable. A write to the location will have no effect.

- *Ghost data returned*: the data returned is the same as the last data written to ANY location in the DRAM system. A write to the location will have no effect. Take care that these "ghost" values don't confuse your memory-sizing code into believing that memory must be there.