# MIPS PR31700 32-bit RISC microprocessor

MIPS PR31700 32-bit RISC microprocessor User Manual Version 0.3

Preliminary specification

1998 Sep 30

Let's make things better.

| Chapter 1 | Overview                     | 1               |

|-----------|------------------------------|-----------------|

| •         | Overview                     | 1               |

|           | References                   | 8               |

| Chapter 2 | Pin Descriptions             | 9               |

| •         | Overview                     | 9               |

|           | Pins                         | 9               |

|           | Memory Pins                  | 9               |

|           | Bus Arbitration Pins         | 11              |

|           | Clock Pins                   | 11              |

|           | CHI Pins                     | 11              |

|           | IO Pins                      | 11              |

|           | Reset Pins                   | 12              |

|           | Power Supply Pins            | 12              |

|           | SIB Pins                     | 12              |

|           | SPI Pins                     | 13              |

|           | UART and IR Pins             | 13              |

|           | Video Pins                   | 13              |

|           | Endianess Pin                | 14              |

|           | Test Pins                    | 14              |

|           | Spare Pins                   | 14              |

|           | Power Supply Pins            | 14              |

|           | Pin Usage Information        | 15              |

| Chapter 3 |                              | 23              |

|           | Overview                     | 23              |

|           | Related Pins                 | 23              |

|           | CPU Core                     | 24              |

|           | Description                  | 24              |

|           | CPU Interface                | 25              |

|           | Block Diagram                | 25              |

|           | Write Buffer                 | 26              |

|           | Interface Controller         | 26              |

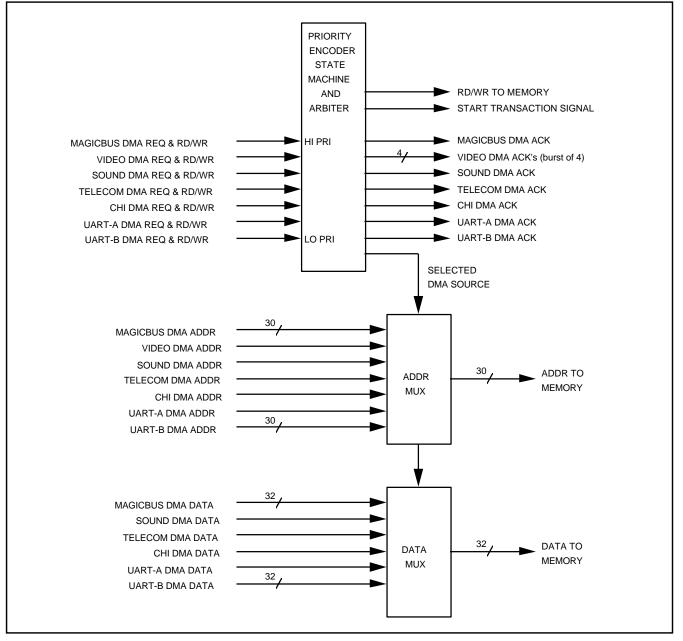

|           | DMA Arbitration              | 27              |

|           | CPU Stop Mode                | 27              |

|           | Test Modes                   | $\overline{28}$ |

|           | Test Bypass Mode             | 28              |

|           | CPU Test Mode                |                 |

| Chapter 4 |                              | 29              |

|           | Overview                     | 29              |

|           | Block Diagram                | 30              |

|           | Address Decoder              | 31              |

|           | System Address Map           | 31              |

|           | Address Generation           | 33              |

|           | Address Re-Mapper Logic      | 34              |

|           | Chip Select Controller       | 35              |

|           | Description                  | 35              |

|           | Access Mapping               | 36              |

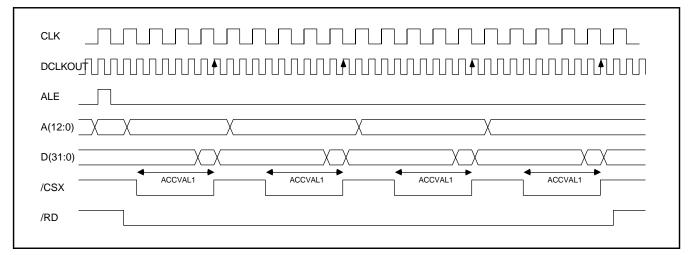

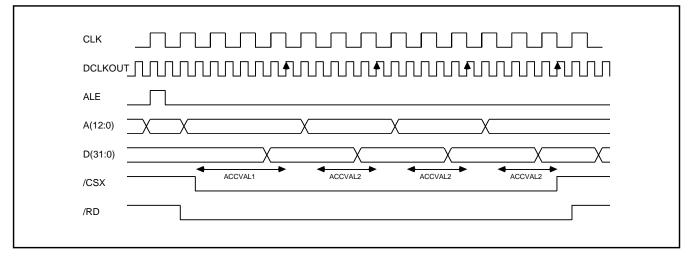

|           | CS3-CS0 and MCS3-MCS0 Timing | 38              |

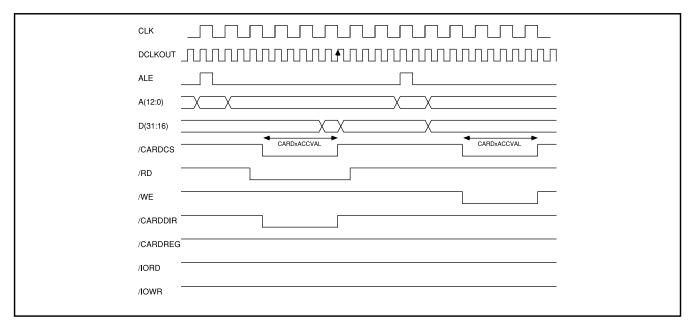

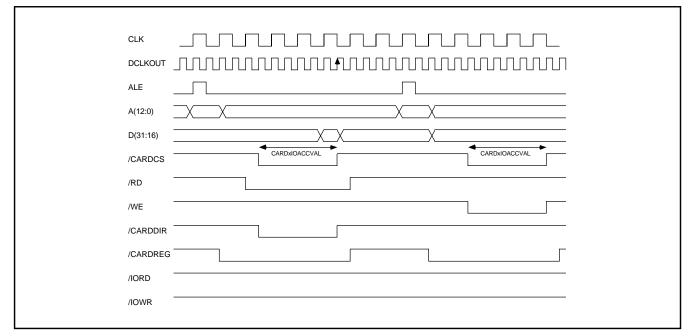

|           | Card 2 and Card 1            | 41              |

|           |                              | -               |

| CS0           | Size Configuration            | 45 |

|---------------|-------------------------------|----|

|               | w PR31700                     | 45 |

|               | M and SDRAM Controller        | 46 |

|               | nory Chips Supported          | 46 |

|               | M and SDRAM Configurations    | 47 |

|               | ΔM                            | 48 |

|               | M Initialization              | 50 |

|               | AM                            | 50 |

| SDR           | AM Initialization             | 50 |

|               | AM Mode Register              | 50 |

|               | AM Power Down Mode            | 50 |

|               | AM Timing                     | 51 |

|               | tration                       | 53 |

|               | esh Controller                | 53 |

|               | rnal Bus Master               | 53 |

| Wate          | ch Dog Timer                  | 53 |

|               | nory Power Down               | 54 |

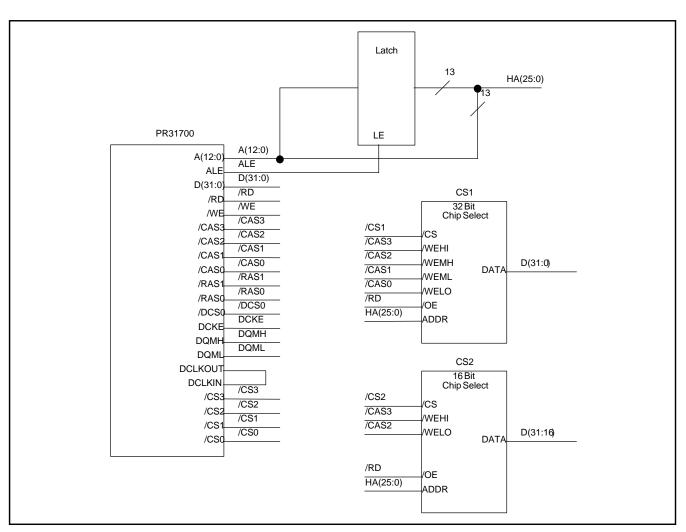

|               | nory Connections              | 56 |

|               | Registers                     | 58 |

| Men           | nory Configuration 0 Register | 58 |

| Men           | nory Configuration 1 Register | 60 |

|               | nory Configuration 2 Register | 61 |

|               | nory Configuration 3 Register | 62 |

| Men           | nory Configuration 4 Register | 63 |

| Men           | nory Configuration 5 Register | 65 |

| Men           | nory Configuration 6 Register | 65 |

|               | nory Configuration 7 Register | 65 |

|               | nory Configuration 8 Register | 65 |

| Chapter 5 SIU | Module                        | 67 |

| Over          | rview                         | 67 |

|               | ementation                    | 68 |

| Bloc          | k Diagram                     | 68 |

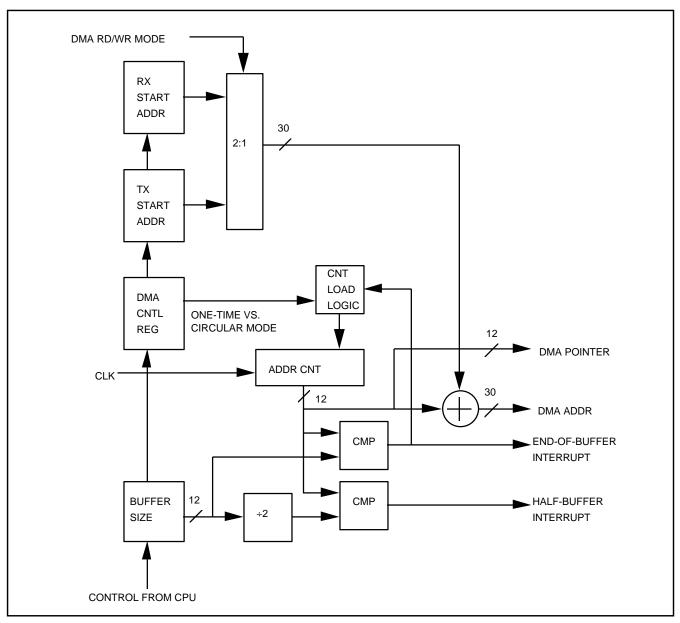

| DM            | A Controller Description      | 69 |

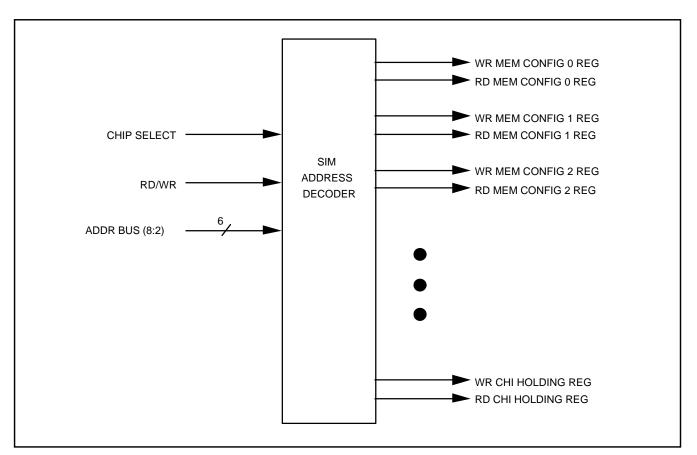

|               | ress Decoder Description      | 69 |

|               | nal PR31700 Registers         | 71 |

| SIU           | Registers                     | 73 |

|               | Test Register                 | 73 |

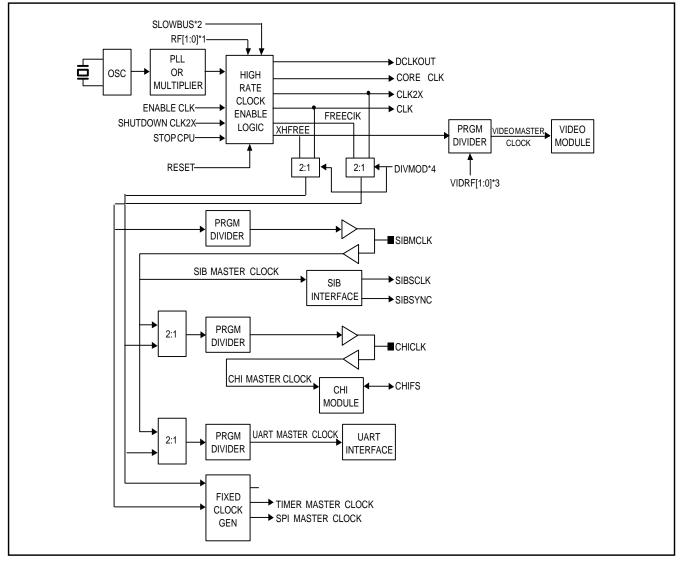

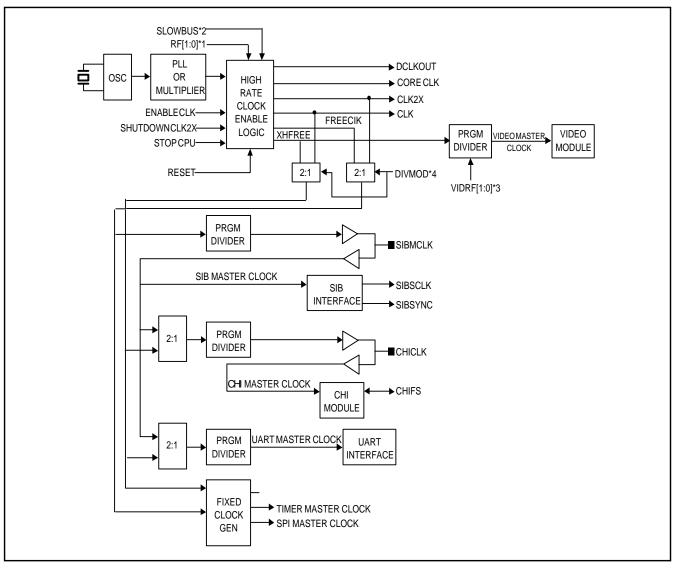

|               | k Module                      | 75 |

| Over          | rview                         | 75 |

| Rela          | ted Pins                      | 75 |

| Impl          | ementation                    | 76 |

|               | k Diagram                     | 76 |

|               | k Module Description          | 77 |

|               | k Registers                   | 79 |

| Cloc          | k Control Register            | 79 |

| Chapter 7 CHI | Module                        | 83 |

|               | rview                         | 83 |

| Rela          | ted Pins                      | 83 |

|               |                               |    |

#### Preliminary

|                  | Interface Requirements            | 84  |

|------------------|-----------------------------------|-----|

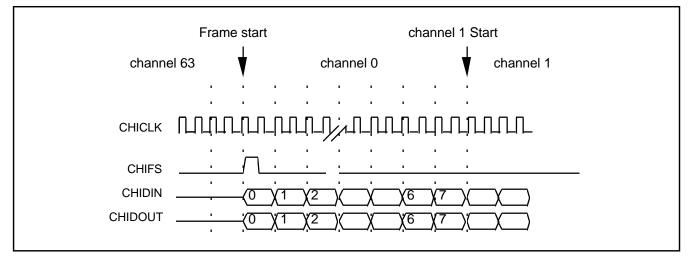

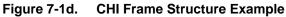

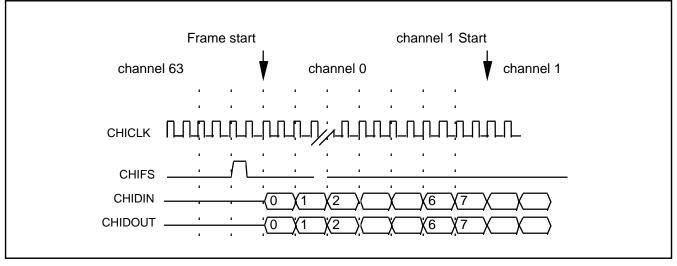

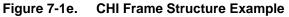

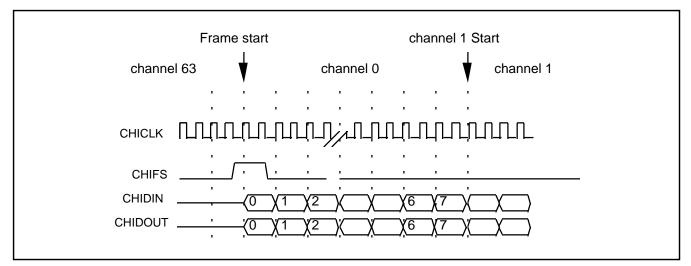

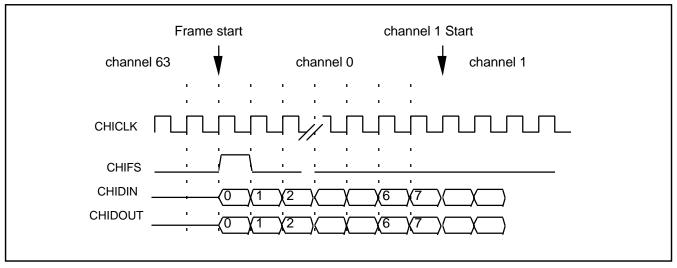

|                  | Frame Structure and Serial Timing |     |

|                  | Configurations                    |     |

|                  | Implementation                    |     |

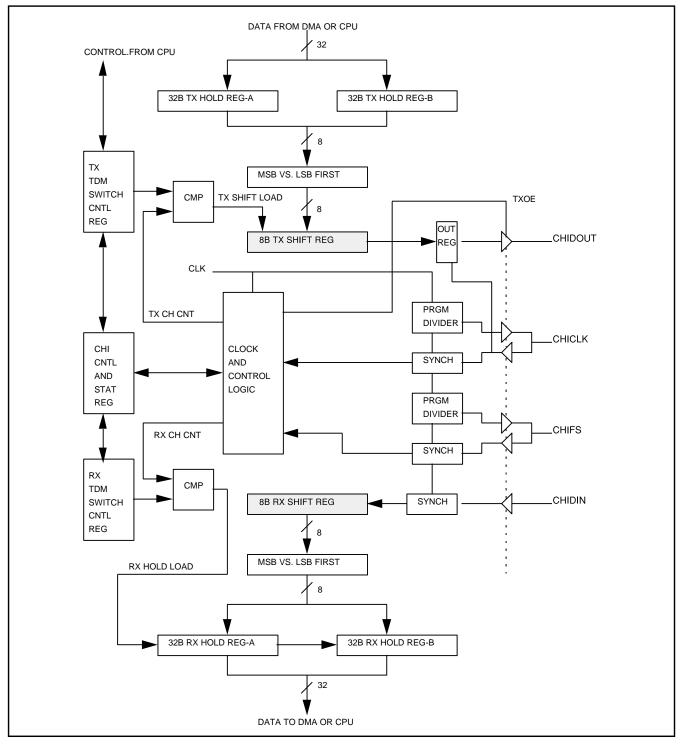

|                  | Block Diagram                     |     |

|                  | Transmitter                       |     |

|                  | Receiver                          |     |

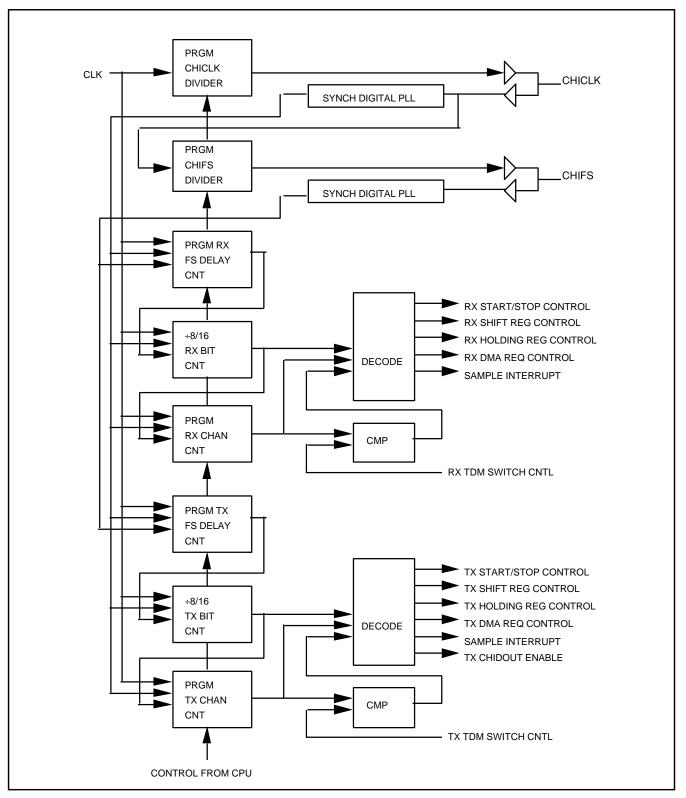

|                  | Clock and Control Generation      |     |

|                  | DMA Address Generation            |     |

|                  | Related Interrupts                |     |

|                  | CHI Registers                     |     |

|                  | CHI Control Register              |     |

|                  | CHI Pointer Enable Register       |     |

|                  | CHI Receive Pointer A Register    |     |

|                  | CHI Receive Pointer B Register    |     |

|                  | CHI Transmit Pointer A Register   |     |

|                  | CHI Transmit Pointer B Register   |     |

|                  | CHI Size Register                 |     |

|                  | CHI RX Start Register             |     |

|                  | CHI TX Start Register             |     |

|                  | CHI TX Holding Register           |     |

|                  | CHI RX Holding Register           |     |

| <b>Chapter 8</b> |                                   | 107 |

| •                | Overview                          | 107 |

|                  | Implementation                    |     |

|                  | Block Diagram                     |     |

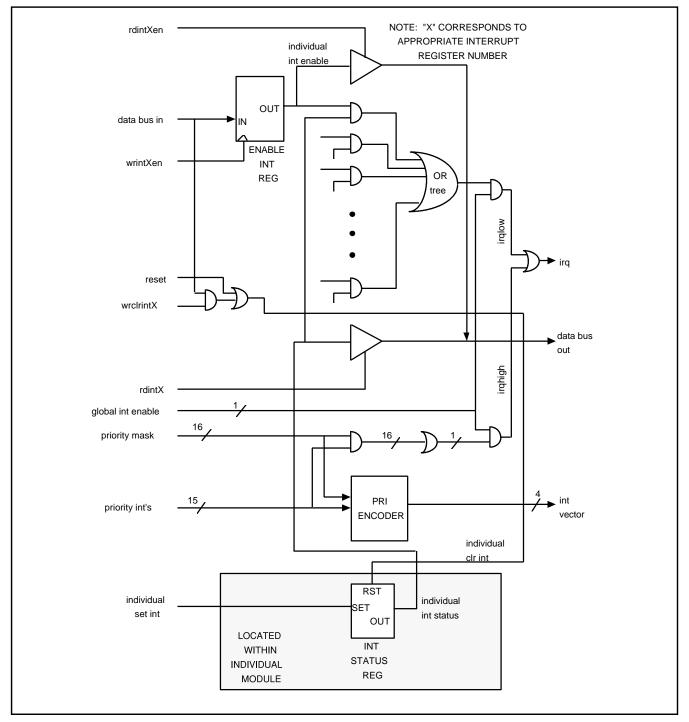

|                  | Interrupt Logic Description       |     |

|                  | Interrupt Registers               |     |

|                  | Interrupt Status 2 Register       |     |

|                  | Interrupt Status 3 Register       |     |

|                  | Interrupt Status 4 Register       |     |

|                  | Interrupt Status 5 Register       |     |

|                  | Interrupt Status 6 Register       |     |

|                  | Clear Interrupt 1 Register        |     |

|                  | Clear Interrupt 2 Register        |     |

|                  | Clear Interrupt 3 Register        |     |

|                  | Clear Interrupt 4 Register        |     |

|                  | Clear Interrupt 5 Register        |     |

|                  | Enable Interrupt 1 Register       |     |

|                  | Enable Interrupt 2 Register       |     |

|                  | Enable Interrupt 3 Register       |     |

|                  | Enable Interrupt 4 Register       |     |

|                  | Enable Interrupt 5 Register       |     |

|                  | Enable Interrupt 6 Register       |     |

| Chapter 9        |                                   | 119 |

| •                | Overview                          |     |

|                  | Related Pins                      |     |

|                  | Implementation                    |     |

|                  | -                                 |     |

| Η          | Block Diagram                | 1 | 20 |

|------------|------------------------------|---|----|

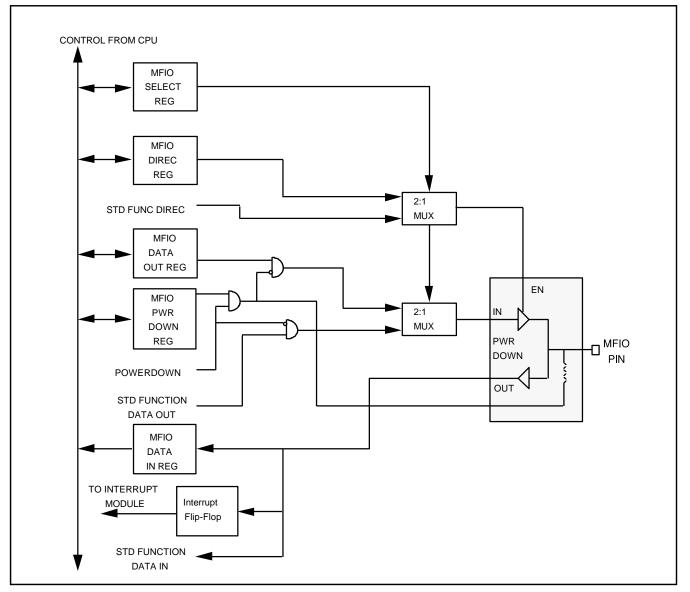

|            | General Purpose IO Ports     |   |    |

|            | Multi-function IO Ports      |   |    |

|            | Related Interrupts           |   |    |

|            | O Registers                  |   |    |

|            | O Control Register           |   |    |

|            | MFIO Data Output Register    |   |    |

|            | MFIO Direction Register      |   |    |

|            | MFIO Data Input Register     |   |    |

|            | MFIO Select Register         |   |    |

|            | O Power-Down Register        |   |    |

|            | MFIO Power-Down Register     |   |    |

|            | 0                            |   | 27 |

|            | Overview                     |   |    |

|            | Related Pins                 |   |    |

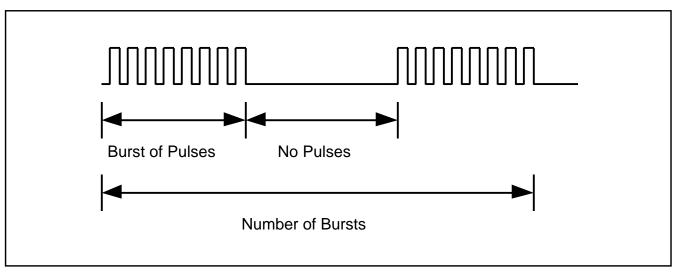

|            | Consumer IR                  |   |    |

|            | Requirements                 |   |    |

|            | Implementation               |   |    |

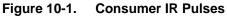

|            | Block Diagram                |   |    |

|            | Related Interrupts           |   |    |

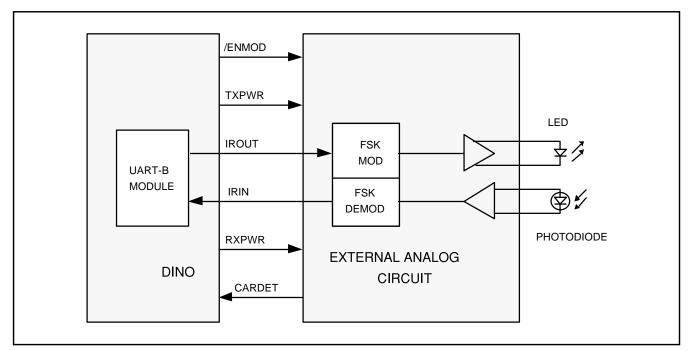

|            | Two-Way Communication Via IR |   |    |

|            | Requirements                 |   |    |

|            | Block Diagram                |   |    |

|            | Carrier Detect State Machine |   |    |

|            | Requirements                 |   |    |

|            | Block Diagram                |   |    |

|            | Functional Description       |   |    |

|            | Related Interrupts           |   |    |

|            | IR Registers                 |   |    |

|            | IR Control 1 Register        |   |    |

|            | IR Control 2 Register        |   |    |

|            | IR Holding Register          |   |    |

|            | Power Module                 |   |    |

| onapter 11 | Overview                     |   |    |

|            | Power Signals                |   |    |

|            | Related Pins                 |   |    |

|            | Description                  |   |    |

|            | Power On Reset               |   |    |

|            | Power Up                     |   |    |

|            | Force Shut Down              |   |    |

|            | Power Down                   |   |    |

|            | Software Considerations      |   |    |

|            | Stop Mode                    |   |    |

|            | Stop Timer                   |   |    |

|            | Power Module Interrupts      |   |    |

|            | Power Registers              |   |    |

|            | Power Control Register       |   |    |

|            |                              | - |    |

| Chapter 12 SIB Module            | 147 |

|----------------------------------|-----|

| Overview                         |     |

| Related Pins                     | 147 |

| Interface Requirements           | 149 |

| Frame Structure                  |     |

| Timing Requirements              |     |

| Configurations                   |     |

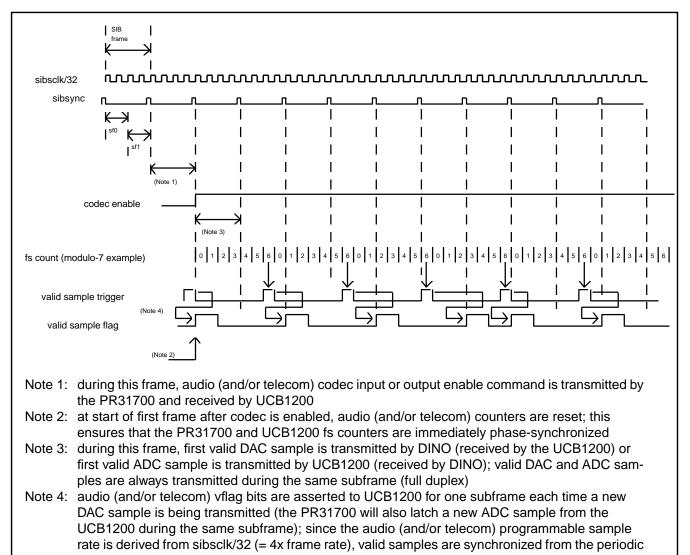

| Sample Rates                     |     |

| Enable/Disable Sequencing        |     |

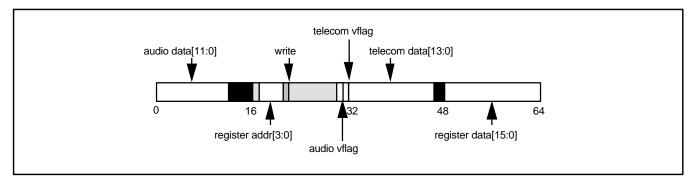

| Data formats                     |     |

| Implementation                   |     |

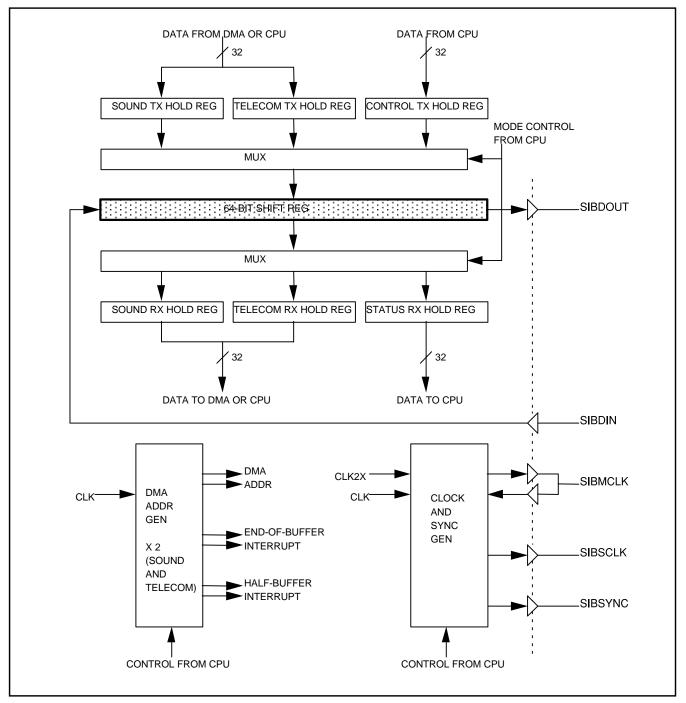

| Block Diagram                    |     |

| Holding and Shift Registers      |     |

| Subframe Formats                 |     |

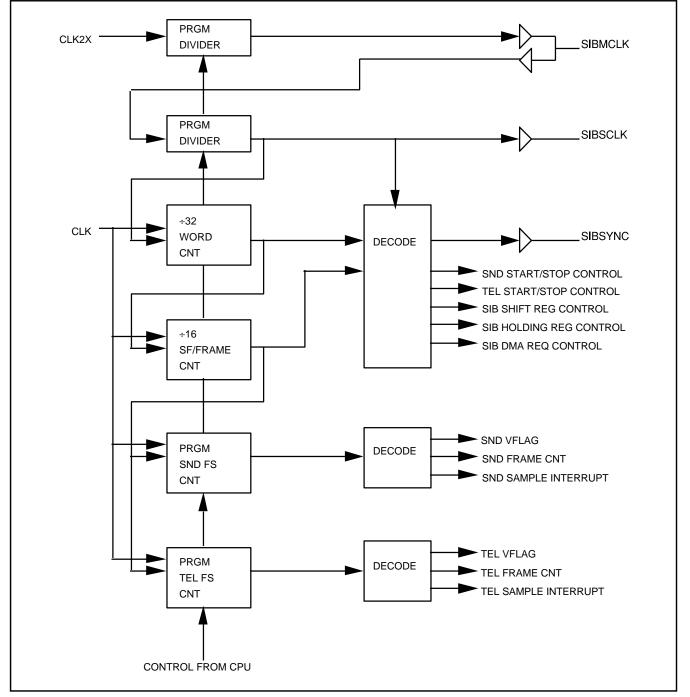

| Clock and Sync Generation        |     |

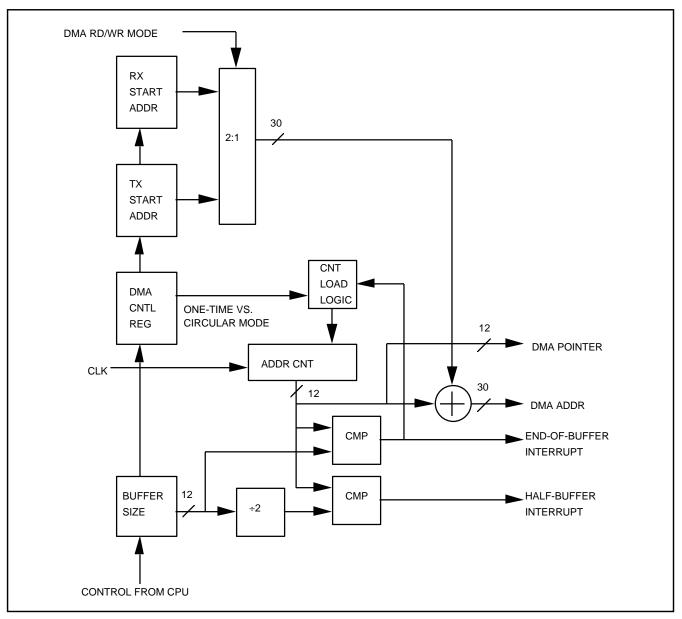

| DMA Address Generation           |     |

| Related Interrupts               |     |

| SIB Registers                    |     |

| SIB Size Register                |     |

| SIB Sound RX Start Register      |     |

| SIB Sound TX Start Register      |     |

| SIB Telecom RX Start Register    |     |

| SIB Telecom TX Start Register    |     |

| SIB Control Register             |     |

| SIB Sound TX Holding Register    |     |

| SIB Sound RX Holding Register    |     |

| SIB Telecom TX Holding Register  |     |

| SIB Telecom RX Holding Register  |     |

| SIB Subframe 0 Control Register  |     |

| SIB Subframe 1 Control Register  |     |

| SIB Subframe 0 Status Register   |     |

| SIB Subframe 1 Status Register   |     |

| SIB DMA Control Register         |     |

| Chapter 13 SPI Module            |     |

| Overview                         | 173 |

| Related Pins                     |     |

| Description                      |     |

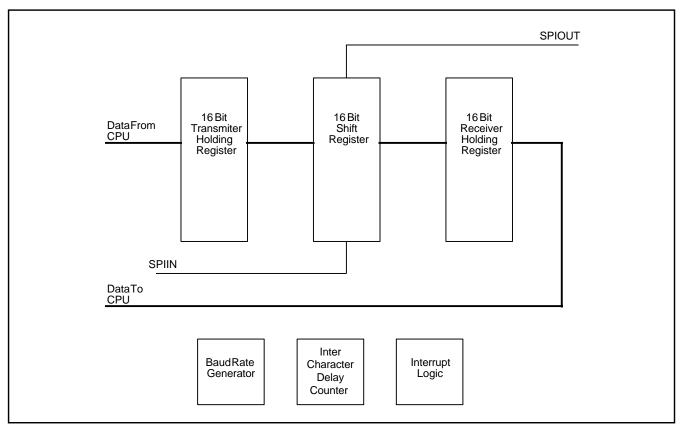

| Block Diagram                    |     |

| Baud Rate Generator              | 175 |

| Transmitter/Receiver             | 175 |

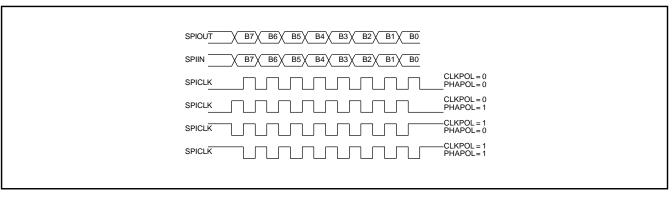

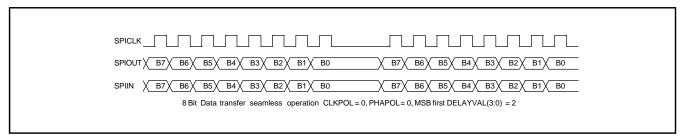

| CLKPOL/PHAPOL                    | 176 |

| SPI Registers                    | 178 |

| SPI Control Register             |     |

| SPI Transmitter Holding Register | 179 |

| SPI Receiver Holding Register    | 179 |

| Chapter 14 Timer Module          | 181 |

| Overview                         |     |

| Related Pins                     | 181 |

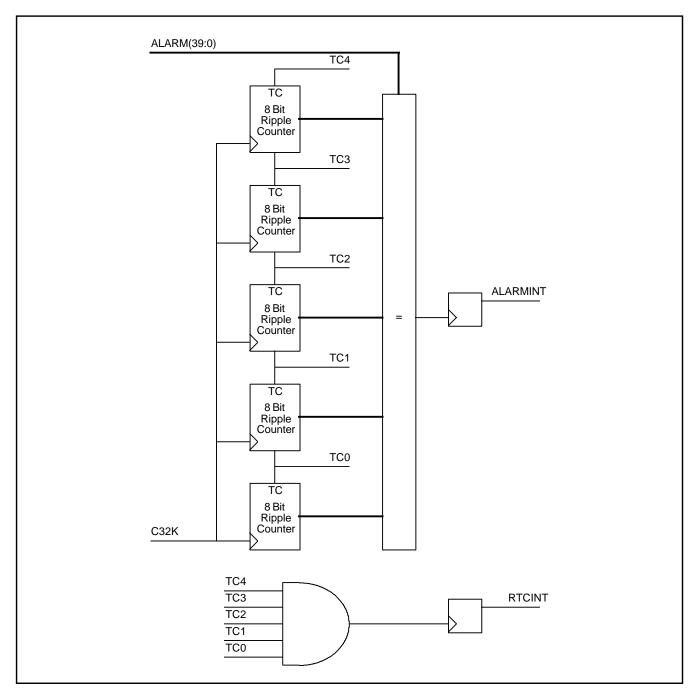

| ]          | RTC                                    | 182 |

|------------|----------------------------------------|-----|

| ]          | RTC Block Diagram                      | 182 |

|            | RTC Description                        |     |

|            | RTC Interrupts                         |     |

|            | Periodic Timer                         |     |

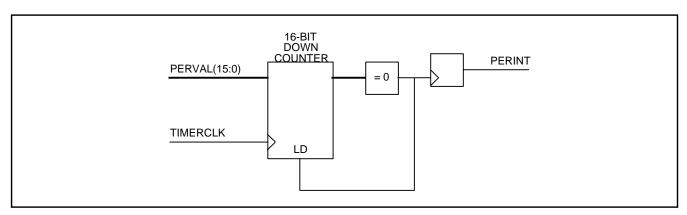

| ]          | Periodic Timer Block Diagram           | 184 |

| ]          | Periodic Timer Description             | 184 |

| ]          | Periodic Timer Interrupts              | 184 |

| r          | Timer Registers                        | 185 |

| ]          | RTC Register                           | 185 |

| 1          | Alarm Register                         | 185 |

| r          | Fimer Control Register                 | 185 |

| ]          | Periodic Timer Register                | 186 |

| Chapter 15 | UART Module                            | 187 |

| (          | Overview                               | 187 |

| ]          | Related Pins                           | 187 |

| (          | Overall Operation                      | 188 |

|            | Power On/Off                           |     |

| ]          | Baud Rate and Communication Parameters | 188 |

| ]          | Interrupt Operation                    | 188 |

| ]          | Responding to Interrupt Status Bits    | 189 |

| ]          | Related Interrupts                     | 190 |

| ]          | DMA Operation                          | 191 |

|            | Internal Loopback                      |     |

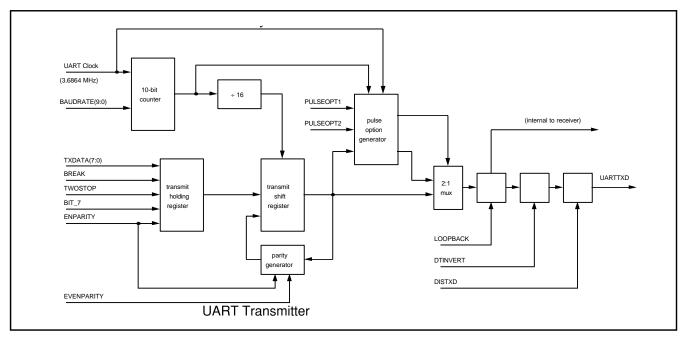

|            | Fransmitter Operation                  |     |

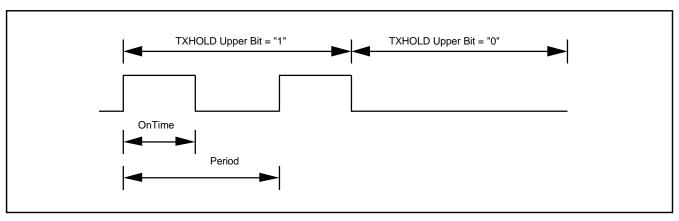

|            | Fransmitter Pulse Output Operation     |     |

|            | Transmitter Disable Operation          |     |

|            | Transmitter BREAK Operation            |     |

| r.         | Fransmitter Overrun                    | 193 |

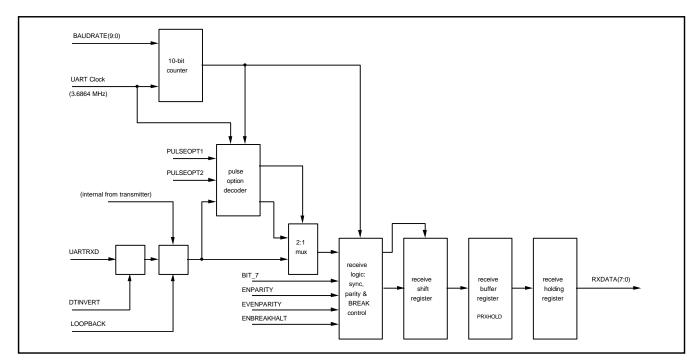

| ]          | Receiver Operation                     | 194 |

|            | Receiver BREAK Operation               |     |

|            | Receiver Frame Error Condition         |     |

|            | Receiver Overrun Condition             |     |

|            | Receiver Parity Error Condition        |     |

|            | Receiver Pulse Operation               | 195 |

|            |                                        | 196 |

|            | UART Control 1 Register                |     |

| l          | UART Control 2 Register                | 197 |

|            | UART DMA Control 1 Register            |     |

|            | UART DMA Control 2 Register            |     |

|            | UART DMA Count                         |     |

|            | UART Transmit Holding Register         |     |

|            | UART Receiver Holding Register         |     |

|            |                                        | 199 |

|            | Overview                               |     |

|            | Related Pins                           |     |

|            | Interface Requirements                 |     |

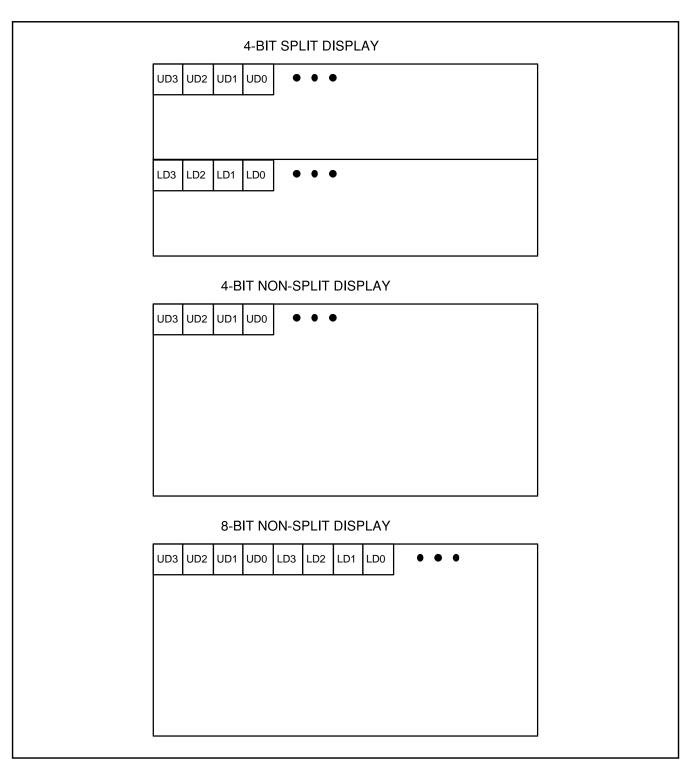

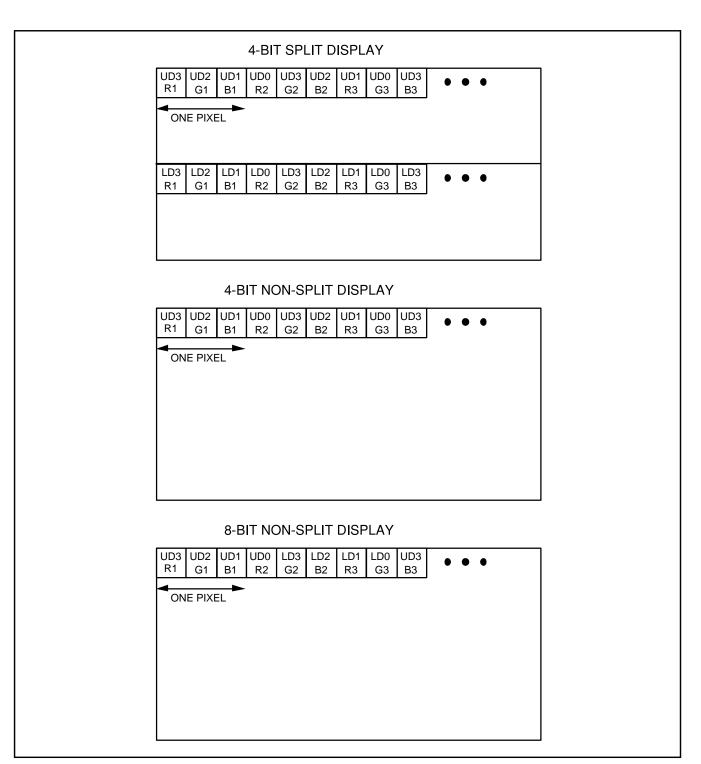

| ]          | Display Types                          | 200 |

#### Preliminary

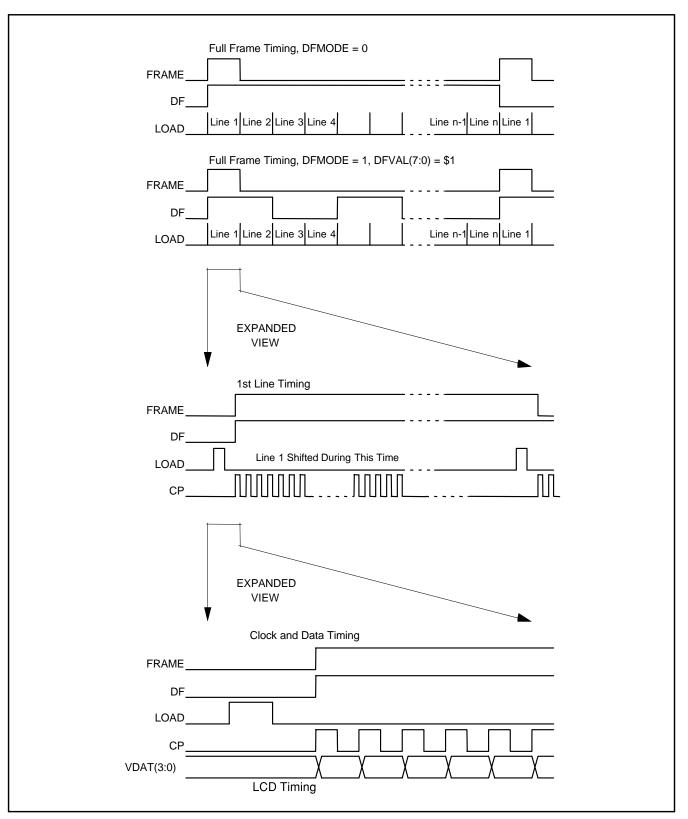

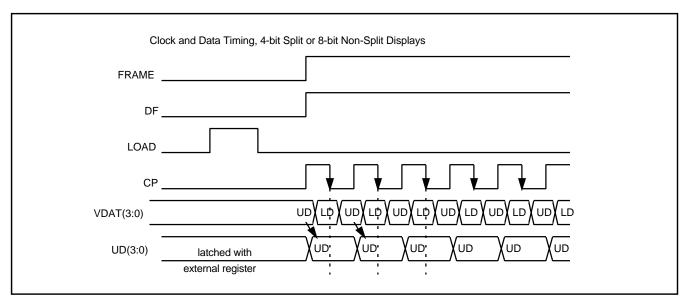

| Timing Requirements                                        | 203 |

|------------------------------------------------------------|-----|

| Synchronization                                            | 206 |

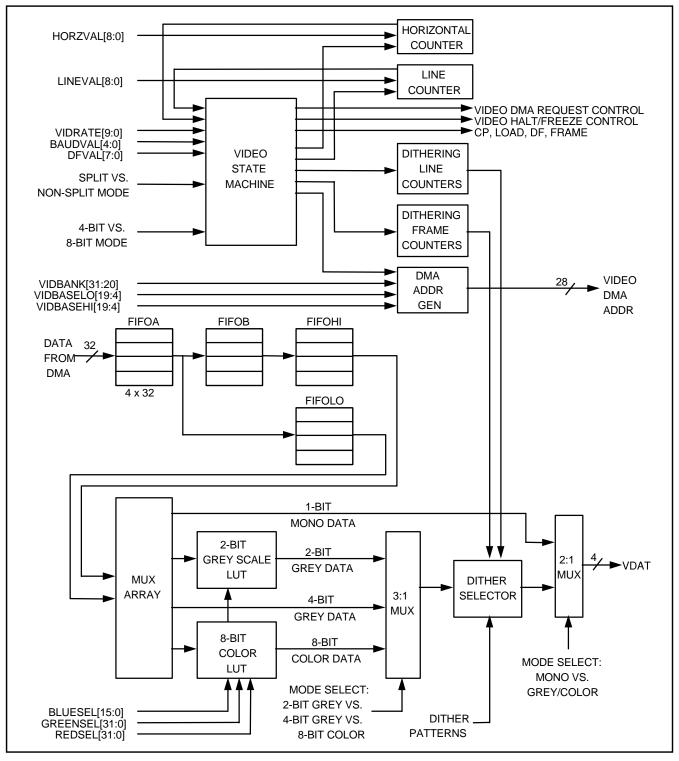

| Implementation                                             | 207 |

| Block Diagram                                              |     |

| Video State Machine                                        | 208 |

| Horizontal Counter                                         | 209 |

| Line Counter                                               | 210 |

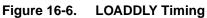

| DMA Address Generation                                     | 210 |

| Video FIFO                                                 | 212 |

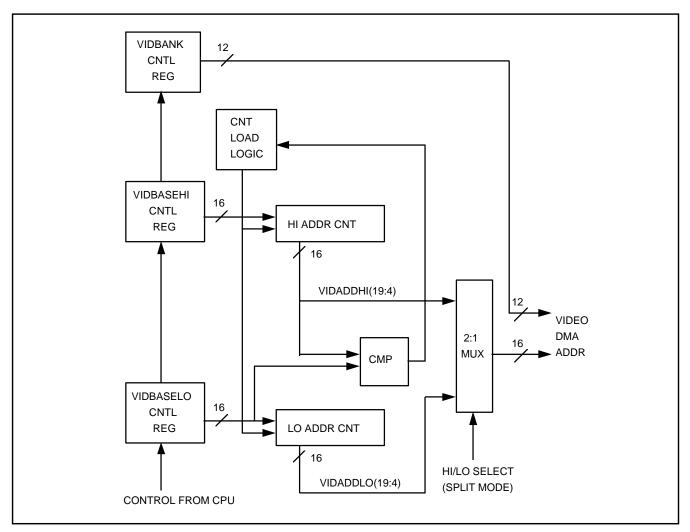

| Grey Scale LUT                                             | 213 |

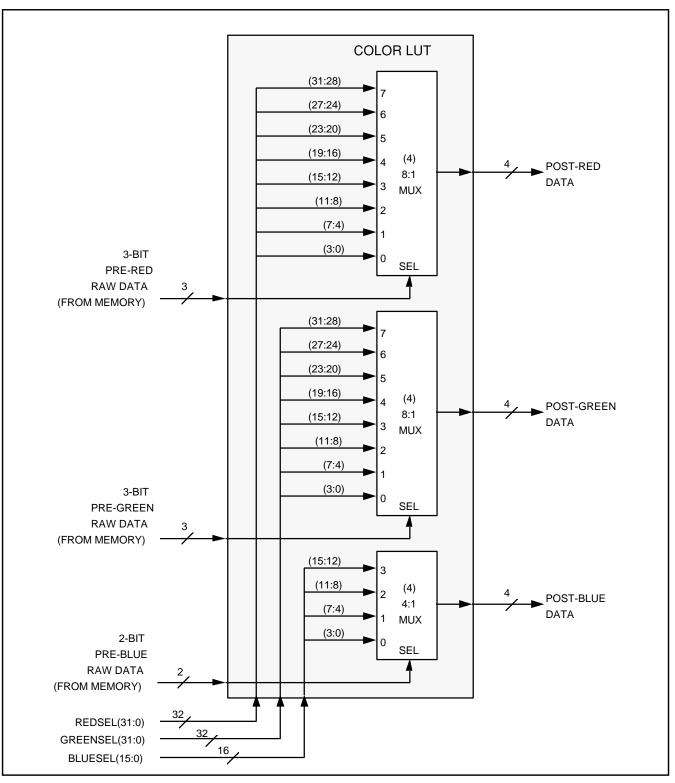

| Color LUT                                                  | 214 |

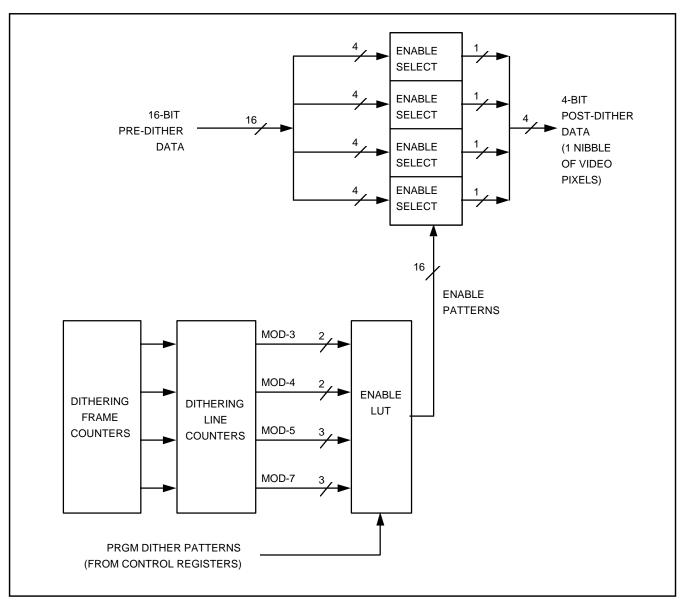

| Dithering                                                  | 216 |

| Related Interrupts                                         | 218 |

| Video Registers                                            | 219 |

| Video Control 1 Register                                   | 219 |

| Video Control 2 Register                                   | 220 |

| Video Control 3 Register                                   | 220 |

| Video Control 4 Register                                   | 221 |

| Video Control 5 Register                                   | 221 |

| Video Control 6 Register                                   | 222 |

| Video Control 7 Register                                   | 222 |

| Video Control 8 Register                                   | 222 |

| Video Control 9 Register                                   | 223 |

| Video Control 10 Register                                  | 223 |

| Video Control 11 Register                                  | 223 |

| Video Control 12 Register                                  | 224 |

| Video Control 13 Register                                  | 224 |

| Video Control 14 Register                                  | 224 |

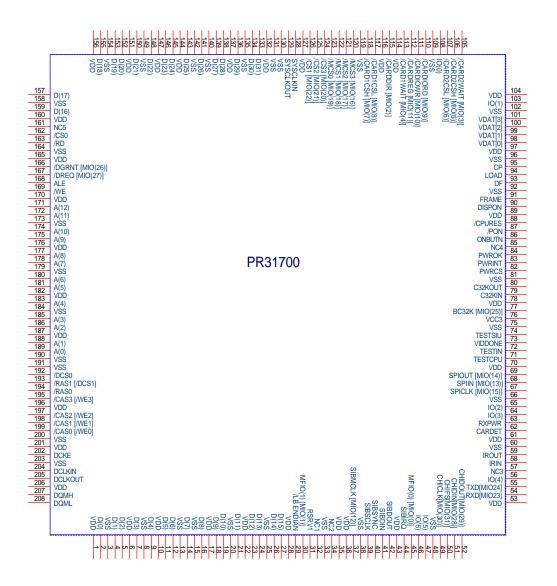

| Chapter 17 Package Information                             | 225 |

| Package Information                                        | 225 |

| Pin Assignment                                             | 225 |

| 208-Pin Plastic Quad Flat Pack                             | 225 |

| Appendix                                                   |     |

| I. The changes and differences between PR31500 and PR31700 |     |

| II. Updates PR31700 user manual version 0.1 to 0.3         | 230 |

PR31700 V0.3

# **Revision History**

| Version | Date     | Changes from Last Version Page             |  |

|---------|----------|--------------------------------------------|--|

| 0.1     | 9/15/97  | Original Issue (Draft)                     |  |

| 0.2     | 12/03/97 | Modify the clock module block diagram      |  |

|         |          | • Fix the clock matrix table77             |  |

|         |          | • Rewrite the paragraph on page 99 and 100 |  |

|         |          | Correct the description of DIVMOD          |  |

|         |          | Insert the missing equation of CP rate     |  |

| 0.3     | 7/14/98  | Complete document reformat                 |  |

# Chapter 1 Overview

# PR31700 V0.3

This section provides an overview of the features and functions of the PR31700 Processor.

### 1.1 Overview

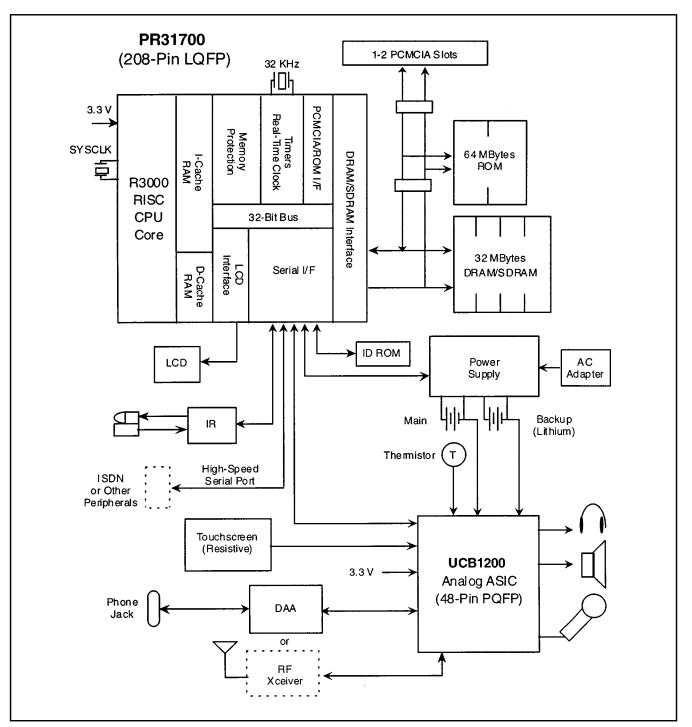

The PR31700 Processor is the single-chip, low-cost, integrated embedded processor consists of MIPS R3000 core and system support logic to interface with varieties of devices. Figure 1-1 shows a system block diagram using the PR31700 Processor.

The PR31700 is available today and has a core runs at a doubled speed of 74 MHz. The new PR31700 described in this manual is pin to pin compatible and functionally identical to the PR31500, but enhancement is made in power consumption during idle mode of operation and added the modification to support 8 bit PC-card access. Please refer appendix in the back of the manual for more detail modification and enhancement.

The PR31700 consists of a MIPS R3000 RISC CPU with 4 KBytes of instruction cache memory and 1 KByte of data cache memory, plus integrated functions for interfacing to numerous system components and external I/O modules. The R3000 RISC CPU is also augmented with a multiple/ accumulate module to allow integrated DSP functions, such as a software modem for high-performance standard data and fax protocols. The PR31700 also contains multiple DMA channels and a high-performance and flexible Bus Interface Unit (BIU) for providing an efficient means for transferring data between external system memory, cache memory, the CPU core, and external I/O modules. The types of external memory devices supported include dynamic random access memory (DRAM), synchronous dynamic random access memory (SDRAM), static random access memory (SRAM), Flash memory, read-only memory (ROM), and expansion cards (PCMCIA). The PR31700 also contains a System Interface Module (SIM) containing integrated functions for interfacing to numerous external I/O modules such as liquid crystal displays (LCD's), the UCB1200 ASIC (which handles most of the analog functions of the system, including sound and telecom codecs and touchscreen ADC), ISDN/high-speed serial, infrared, wireless peripherals, etc. Lastly, the PR31700 contains support for implementation of power management for the entire device, whereby various PR31700 internal modules and external subsystems can be individually (under software control) powered up and down. The PR31700 contains the following overall features:

- high level of integration on a single chip, optimized for low cost, small board space, low pin count, low power, and high performance

- Plastic 208-pin quad flat pack (LQFP) package

- 32-bit R3000 RISC CPU, cache memory, multiply-accumulate module, multi-channel DMA controller, bus interface unit and memory controller, power management, and other peripheral subsystems all on a single integrated chip

- minimal number of inter-chip connections

- 74 MHz version available

- low power consumption

- maximum peak current running at 73.728 MHz = 100 to 120 mA (estimated)

- standby current = 10 A (typ.)

- entire PR31700 operation is 3.3V

- real-time clock based on 32.768 KHz reference

- CPU clock stop state for low standby current

- power-down modes for individual internal peripheral modules

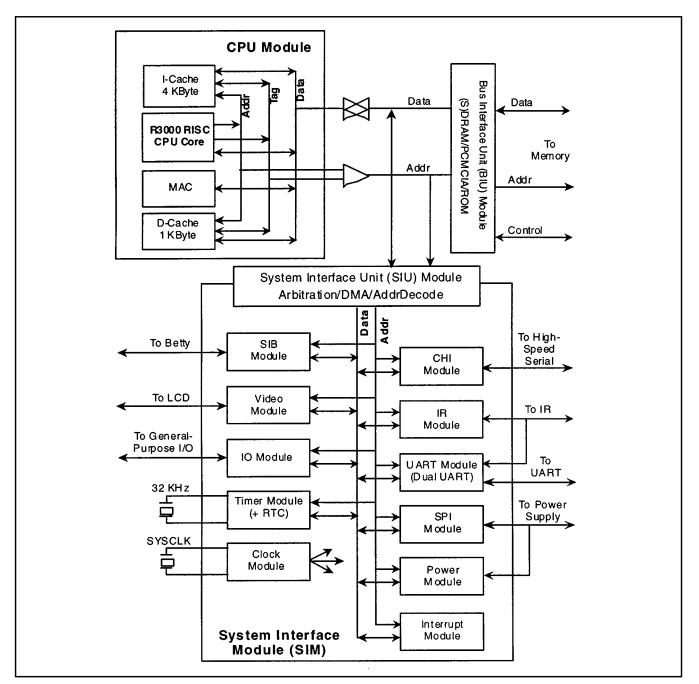

Figure 1-2 shows a block diagram of the PR31700 . The key functions and features for each PR31700 module are briefly described in following sections.

# Chapter 1 Overview

Figure 1-1. System Block Diagram

# Chapter 1 Overview

# PR31700 V0.3

#### **CPU Module**

- R3000 RISC central processing unit core

- full 32-bit operation (registers, instructions, addresses, etc.)

- 32 general purpose 32-bit registers; 32-bit program counter

- MIPS RISC Instruction Set Architecture (ISA) supported

- 32 x 64-bit wide entries, on-chip Translation Look-aside Buffers (TLBs) provide the virtual-to-physical address translation that is essential in implementing a powerful operating system

- on-chip cache

- 4 KByte direct-mapped instruction cache (I-cache)

- · physical address tag and valid bit per cache line

- programmable burst size

- · instruction streaming mode supported

- 1 KByte two-way associative data cache (D-cache)

- · physical address tag and valid bit per cache line

- programmable burst size

- write-through

- cache address snoop mode supported for DMA

- four-stage write buffer

- · programmable memory protection

- separate read and write protection control for kernel and user space

- 8 total protectable regions available, each individually programmable, using breakpoint address, mask, control, and status registers

- causes address exception on illegal reads or writes

- · high-speed multiplier/accumulator

- on-chip hardware multiplier

- supports 16x16 or 32x32 multiplier operations, with 64-bit accumulator

- existing multiply instructions are enhanced and new multiply and add instructions are added to R3000 instruction set to improve the performance of DSP applications

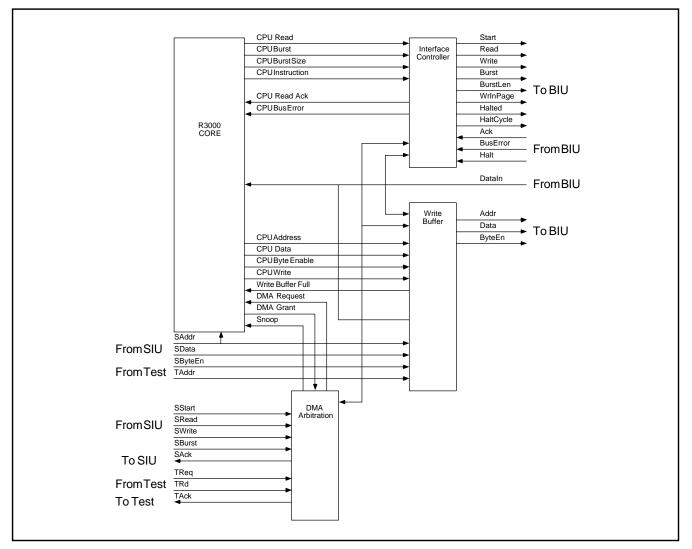

- CPU interface

- handles data bus, address bus, and control interface between CPU core and the rest of the PR31700 logic

Chapter 1

Overview

Figure 1-2. PR31700 Processor Block Diagram

# PR31700 V0.3

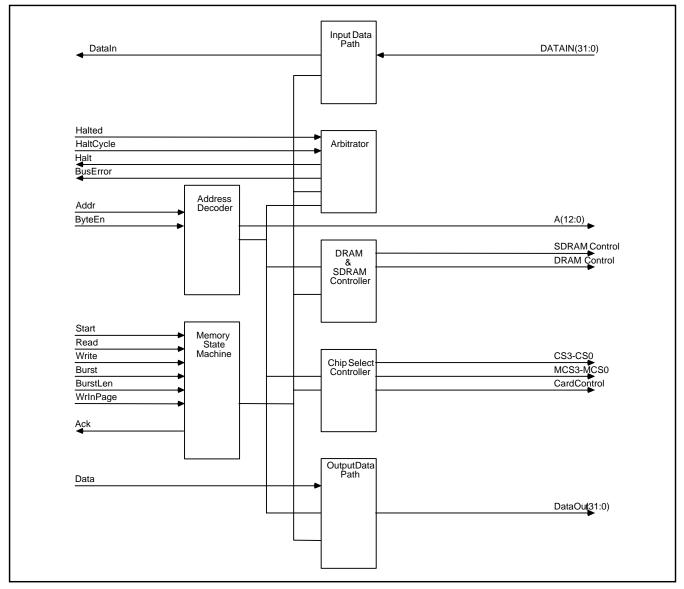

#### **BIU Module**

- system memory and PR31700 Bus Interface Unit (BIU)

- supports up to 2 banks of physical memory

- supports self-refreshing DRAM and SDRAM programmable parameters for each bank of DRAM or SDRAM (row/column address configuration, refresh, burst modes, etc.)

- · programmable chip select memory access

- 4 programmable (size, wait states, burst mode control) memory device and general purpose chip selects

- · available for system ROM, SRAM, Flash

- · available for external port expansion registers

- 4 programmable (wait states, burst mode control) general purpose chip selects

- PR31700 provides the chip select and card detect signals

- supports card insertion/removal timeouts

- supports up to 2 identical full PCMCIA ports

- PR31700 and UCB1200 provide the control signals and accepts the status signals which conform to the PCMCIA version 2.01 standard

- appropriate connector keying and level-shifting buffers required for 3.3V versus 5V PCMCIA interface implementations

- support 16-bit and 8-bit PC-Card access.

#### **SIU Module**

- multi-channel 32-bit DMA controller and System Interface Unit (SIU)

- independent DMA channels for video, SIB to/from UCB1200 audio/telecom codecs,

- · high-speed serial port, IR UART, and general purpose UART

- · address decoding for submodules within System Interface Module (SIM)

#### **Clock Module**

- PR31700 supports system-wide single crystal configuration, besides the 32 KHz RTC XTAL (reduces cost, power, and board space)

- common crystal rate divided to generate clock for CPU, video, sound, telecom, UARTs, etc.

- · independent enabling or disabling of individual clocks under software control, for power management

#### **CHI Module**

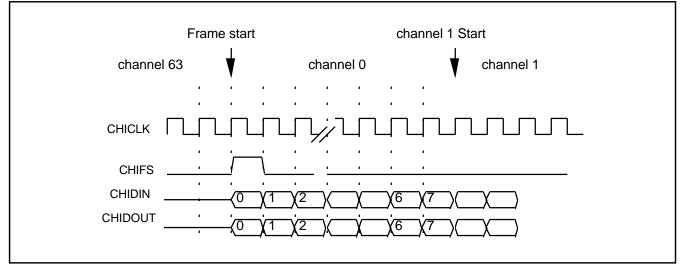

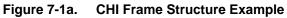

- high-speed serial Concentration Highway Interface (CHI) contains logic for interfacing to external full-duplex serial time-division-multiplexed (TDM) communication peripherals

- supports ISDN line interface chips and other PCM/TDM serial devices

- CHI interface is programmable (number of channels, frame rate, bit rate, etc.) to provide support for a variety of formats

- supports data rates up to 4.096 Mbps independent DMA support for CHI receive and transmit

# PR31700 V0.3

#### **Interrupt Module**

- · contains logic for individually enabling, reading, and clearing all PR31700 interrupt sources

- interrupts generated from internal PR31700 modules or from edge transitions on external signal pins

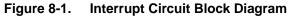

#### **IO Module**

- contains support for reading and writing the 7 bi-directional general purpose IO pins and the 32 bi-directional multi-function IO pins

- · each IO port can generate a separate positive and negative edge interrupt

- independently configurable IO ports allow PR31700 to support a flexible and wide range of system applications and configurations

#### **IR Module**

- IR consumer mode

- allows control of consumer electronic devices such as stereos, TVs, VCRs, etc.

- programmable pulse parameters

- external analog LED circuitry

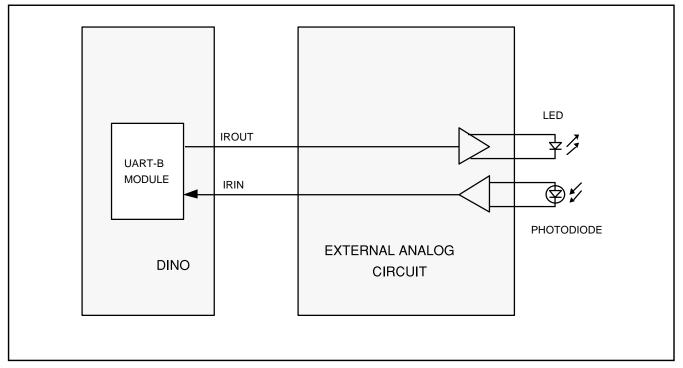

- · IrDA communication mode

- allows communication with other IrDA devices such as FAX machines, copiers, printers, etc.

- supported by UART module within the PR31700

- external analog receiver preamp and LED circuitry

- data rate = up to 115 Kbps at 1 meter

- IR FSK communication mode

- supported by UART module within the PR31700

- external analog IR chip(s) perform frequency modulation to generate the desired IR communication mode protocol

- data rate = up to 36000 bps at 3 meters

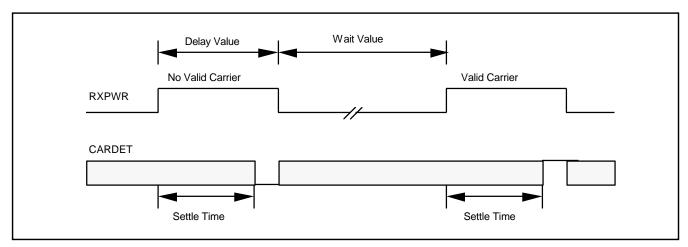

- · carrier detect state machine

- periodically enables IR receiver to check if a valid carrier is present

#### **Power Module**

- · power-down modes for individual internal peripheral modules

- · serial (SPI port) power supply control interface supported

- power management state machine has 3 states: ACTIVE, IDLE (DOZING) and SLEEP

#### **SIB Module**

- The PR31700 contains holding and shift registers to support the serial interface to the UCB1200 ASIC and/or other optional codec devices

- synchronous, frame-based protocol

- The PR31700 always master source of clock and frame frequency and phase; programmable clock frequency

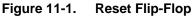

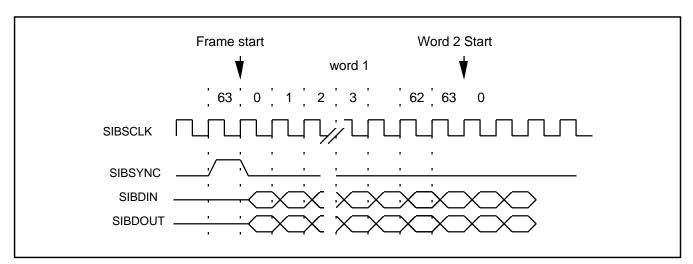

- each SIB frame consists of 128 clock cycles, further divided into 2 subframes or words of 64 bits each (supports up to 2 devices simultaneously)

Chapter 1

Overview

# PR31700 V0.3

- · independent DMA support for audio receive and transmit, telecom receive and transmit

- · supports 8-bit or 16-bit mono telecom formats

- · supports 8-bit or 16-bit mono audio formats

- · independently programmable audio and telecom sample rates

- · CPU read/write registers for subframe control and status

#### **SPI Module**

- · provides interface to SPI peripherals and devices

- full-duplex, synchronous serial data transfers (data in, data out, and clock signals)

- The PR31700 supplies dedicated chip select and interrupt for an SPI interface serial power supply

- · 8-bit or 16-bit data word lengths for the SPI interface

- programmable SPI baud rate

#### **Timer Module**

- · Real Time Clock (RTC) and Timer

- 40-bit counter (30.517 sec granularity); maximum uninterrupted time = 388.36 days

- 40-bit alarm register (30.517 sec granularity)

- 16-bit periodic timer (0.868 sec granularity); maximum timeout = 56.8 msec

- · interrupts on alarm, timer, and prior to RTC roll-over

#### **UART Module**

- 2 independent full-duplex UARTs

- · programmable baud rate generator

- · UART-A port used for general purpose serial control interface

- UART-B port used for serial control interface to external IR module

- · UART-A and UART-B DMA support for receive and transmit

#### Video Module

- bit-mapped graphics

- · supports monochrome, grey scale, or color modes

- time-based dithering algorithm for grey scale and color modes

- · supports multiple screen sizes

- · supports split and non-split displays

- · variable size and relocatable video buffer

- · DMA support for fetching image data from video buffer

# PR31700 V0.3

Chapter 1 Overview

#### 1.2 References

#### (1) Philips Semiconductors PR31700 User Manual, Revision 1.0

This document contains a preliminary description of the PR31700 Processor. This document includes pin descriptions, address memory map, theory of operation and block diagrams for each submodule, register assignments and functions, and interface timing diagrams and protocols.

#### (2) Philips Semiconductors UCB1100/1200 Advanced modem/audio analog front-end, 1997 Jun. 12

This document contains an objective specification of the mixed signal telecomm/audio codec. This document includes pin descriptions, block diagrams, register assignments and functions, and interface timing diagrams.

# PR31700 V0.3

This section describes the pins of the PR31700 Processor.

#### 2.1 Overview

The PR31700 processor contains 208 pins consisting of input, output, bi-directional, and power and ground pins. These pins are used to support various functions. The following sections will describe the function of each pin including any special power-down considerations for each pin.

#### 2.2 Pins

The PR31700 Processor contains 208 total pins, consisting of 135 signal pins, 5 spare pins, 34 power pins, and 34 ground pins. Of the 133 signal pins, 32 of them are multi-function and can be independently programmed either as IO ports or for an alternate standard/normal function. As an IO port, any of these pins can be programmed as an input or output port, with the capability of generating a separate positive and negative edge interrupt. See Section 2.3 for a summary of the multi-function IO ports versus their standard functions.

#### 2.2.1 **Memory Pins**

#### D(31:0):

#### **INPUT/OUTPUT**

These pins are the data bus for the system. 8-bit SDRAMs should be connected to bits 7:0 and 16-bit SDRAMs and DRAMs should be connected to bits 15:0. All other 16-bit ports should be connected to bits 31:16. Of course, 32-bit ports should be connected to bits 31:0. These pins are normally outputs and only become inputs during reads, thus no resistors are required since the bus will only float for a short period of time during bus turn-around.

#### A(12:0):

# OUTPUT

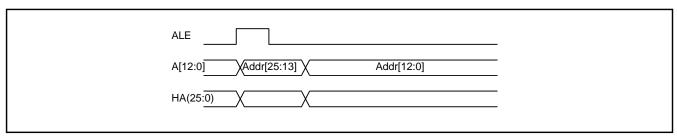

These pins are the address bus for the system. The address lines are multiplexed and can be connected directly to SDRAM and DRAM devices. To generate the full 26-bit address for static devices, an external latch must be used to latch the signals using the ALE signal. For static devices, address bits 25:13 are provided by the external latch and address bits 12:0 (directly connected from the PR31700's address bus) are held afterward by the PR31700 processor for the remainder of the address bus cycle.

#### ALE

#### OUTPUT

This pin is used as the address latch enable to latch A(12:0) using an external latch, for generating the upper address bits 25:13.

OUTPUT

#### /RD:

This pin is used as the read signal for static devices. This signal is asserted for reads from /MCS3-0, /CS3-0, /CARD2CS and /CARD1CS for memory and attribute space, and for reads from PR31700 processor accesses if SHOWPR31700 is enabled (for debugging purposes).

#### /WE:

# OUTPUT

OUTPUT

This pin is used as the write signal for the system. This signal is asserted for writes to /MCS3-0, /CS3-0, /CARD2CS and /CARD1CS for memory and attribute space, and for writes to DRAM and SDRAM.

#### /CAS0 (/WE0):

#### This pin is used as the CAS signal for SDRAMs, the CAS signal for D(7:0) for DRAMs, and the write enable signal for D(7:0) for static devices.

#### /CAS1 (/WE1):

#### OUTPUT

This pin is used as the CAS signal for D(15:8) for DRAMs and the write enable signal for D(15:8) for static devices.

#### /CAS2 (/WE2):

OUTPUT This pin is used as the CAS signal for D(23:16) for DRAMs and the write enable signal for D(23:16) for static devices.

#### /CAS3 (/WE3):

This pin is used as the CAS signal for D(31:24) for DRAMs and the write enable signal for D(31:24) for static devices.

# OUTPUT

9

#### /RAS0: OUTPUT

#### This pin is used as the RAS signal for SDRAMs and the RAS signal for Bank0 DRAMs.

#### /RAS1 (/DCS1):

This pin is used as the chip select signal for Bank1 SDRAMs and the RAS signal for Bank1 DRAMs.

OUTPUT

OUTPUT

OUTPUT

INPUT

#### /DCS0:

This pin is used as the chip select signal for Bank0 SDRAMs.

#### DCKE:

This pin is used as the clock enable for SDRAMs.

#### DCLKIN:

This pin must be tied externally to the DCLKOUT signal and is used to match skew for the data input when reading from SDRAM and DRAM devices.

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

#### DCLKOUT:

This pin is the (nominal) 73.728 MHz clock for the SDRAMs.

#### DQMH:

This pin is the upper data mask for a 16-bit SDRAM configuration.

#### DQML:

This pin is the lower data mask for a 16-bit SDRAM or 8-bit SDRAM configuration.

#### /CS3-0:

These pins are the Chip Select 3 through 0 signals. They can be configured to support either 32-bit or 16-bit ports.

#### /MCS3-0:

These pins are the auxiliary Chip Select 3 through 0 signals. They only support 16-bit ports.

#### /CARD2CSH,L: These pins are the Chip Select signals for PCMCIA card slot 2.

/CARD1CSH,L:

These pins are the Chip Select signals for PCMCIA card slot 1.

#### /CARDREG:

This pin is the /REG signal for the PCMCIA cards.

#### /CARDIORD:

This pin is the /IORD signal for the PCMCIA IO cards.

#### /CARDIOWR:

This pin is the /IOWR signal for the PCMCIA IO cards.

#### /CARDDIR:

This pin is used to provide the direction control for bi-directional data buffers used for the PCMCIA slot(s). This signal will assert whenever /CARD2CSH or /CARD2CSL or /CARD1CSH or /CARD1CSL is asserted and a read transaction is taking place.

#### /CARD2WAIT:

This pin is the card wait signal from PCMCIA card slot 2.

### /CARD1WAIT:

This pin is the card wait signal from PCMCIA card slot 1.

# 10

# PR31700 V0.3

Preliminary

OUTPUT

OUTPUT

OUTPUT

INPUT

INPUT

OUTPUT

OUTPUT

1998 Sep 30

#### 2.2.2 **Bus Arbitration Pins**

#### /DREQ:

INPUT

This pin is used to request external arbitration. If the TESTSIU signal is high and the TESTSIU function has been enabled, then once /DGRNT is asserted, external logic can initiate reads or writes to PR31700 processor registers by driving the appropriate input signals. If the TESTSIU signal is low or the TESTSIU function has not been enabled, then PR31700 memory transactions are halted and certain memory signals will be tri-stated when /DGRNT is asserted in order to allow an external master to access memory.

#### /DGRNT:

This pin is asserted in response to /DREQ to inform the external test logic or bus master that it can now begin to drive signals.

OUTPUT

#### 2.2.3 **Clock Pins**

#### SYSCLKIN:

This pin should be connected along with SYSCLKOUT to an external crystal which is the main PR31700 clock source.

OUTPUT

INPUT

#### SYSCLKOUT:

This pin should be connected along with SYSCLKIN to an external crystal which is the main PR31700 clock source.

#### C32KIN:

This pin along with C32KOUT should be connected to a 32.768 KHz crystal.

#### C32KOUT:

This pin along with C32KIN should be connected to a 32.768 KHz crystal.

#### BC32K:

This pin is a buffered output of the 32.768 KHz clock.

#### CHI Pins 2.2.4

#### CHIFS:

This pin is the CHI frame synchronization signal. This pin is available for use in one of two modes. As an output, this pin allows the PR31700 to be the master CHI sync source. As an input, this pin allows an external peripheral to be the master CHI sync source and the PR31700 CHI module will slave to this external sync.

#### CHICLK:

#### **INPUT/OUTPUT**

**INPUT/OUTPUT**

This pin is the CHI clock signal. This pin is available for use in one of two modes. As an output, this pin allows the PR31700 to be the master CHI clock source. As an input, this pin allows an external peripheral to be the master CHI clock source and the PR31700 CHI module will slave to this external clock.

OUTPUT

INPUT

#### CHIDOUT:

This pin is the CHI serial data output signal.

#### CHIDIN:

This pin is the CHI serial data input signal.

#### 2.2.5 IO Pins

#### IO(6:0):

### **INPUT/OUTPUT**

These pins are general purpose input/output ports. Each port can be independently programmed as an input or output port. Each port can generate a separate positive and negative edge interrupt. Each port can also be independently programmed to use a 16 to 24 msec debouncer.

#### MFIO(1:0):

#### **INPUT/OUTPUT**

These pins are multi-function input/output ports. Each port can be independently programmed as an input or output port, or can be programmed for multi-function use to support vendor-dependent test signals (for debugging purposes only). Each port can generate a separate positive and negative edge interrupt. Note that 30 other multifunction pins are available for usage as multi-function input/output ports. These pins are named after their respective standard/normal function and are not listed here.

# PR31700 V0.3

# OUTPUT

INPUT

# OUTPUT

#### 2.2.6 Reset Pins

#### /CPURES:

This pin is used to reset the CPU core. This pin should be connected to a switch for initiating a reset in the event that a software problem might hang the CPU core. The pin should also be pulled up to VSTANDBY through an external pull-up resistor.

INPUT

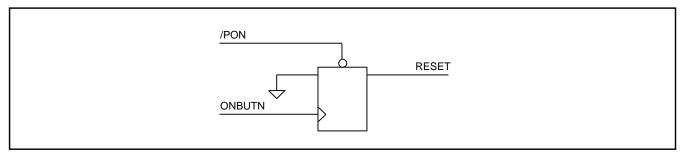

#### /PON:

#### INPUT

This pin serves as the Power On Reset signal for PR31700. This signal must remain low when VSTANDBY is asserted until VSTANDBY is stable. Once VSTANDBY is asserted, this signal should never go low unless all power is lost in the system.

#### 2.2.7 Power Supply Pins

#### ONBUTN:

This pin is used as the On Button for the system. Asserting this signal will cause PWRCS to set to indicate to the System Power Supply to turn power on to the system. PWRCS will not assert if the PWROK signal is low.

#### **PWRCS**:

### OUTPUT

INPUT

INPUT

This pin is used as the chip select for the System Power Supply. When the system is off, the assertion of this signal will cause the System Power Supply to turn VCCDRAM and VCC3 on to power up the system. The Power Supply will latch SPI commands on the falling edge of PWRCS.

#### **PWROK**:

This pin provides a status from the System Power Supply that there is a good source of power in the system. This signal typically will be asserted if there is a Battery Charger supplying current or if the Main Battery is good and the Battery Door is closed. If PWROK is low when the system is powered off, PWRCS will not assert as a result of the user pressing the ONBUTN or an interrupt attempting to wake up the system. If the device is on when the PWROK signal goes low, the software will immediately shut down the system since power is about to be lost. When PWROK goes low, there must be ample warning so that the software can shut down the system before power is actually lost.

#### **PWRINT**:

This pin is used by the System Power Supply to alert the software that some status has changed in the System Power Supply and the software should read the status from the System Power Supply to find out what has changed. These will be low priority events, unlike the PWROK status, which is a high priority emergency case.

INPUT

### VCC3:

# for the R

INPUT

OUTPUT

OUTPUT

This pin provides the status of the power supply for the ROM, UCB1200, system buffers, and other transient components in the system. This signal will be asserted by the System Power Supply when PWRCS is asserted, and will always be turned off when the system is powered down.

### 2.2.8 SIB Pins

#### SIBDIN:

This pin contains the input data shifted from the UCB1200 and/or external codec device.

### SIBDOUT:

This pin contains the output data shifted to the UCB1200 and/or external codec device.

#### SIBSCLK:

This pin is the serial clock sent to the UCB1200 and/or external codec device. The programmable SIBSCLK rate is derived by dividing down from SIBMCLK.

#### SIBSYNC:

#### OUTPUT

This pin is the frame synchronization signal sent to the UCB1200 and/or external codec device. This frame sync is asserted for one clock cycle immediately before each frame starts and all devices connected to the SIB monitor SIBSYNC to determine when they should transmit or receive data.

#### SIBIRQ:

INPUT

This pin is a general purpose input port used for the SIB interrupt source from the UCB1200. This interrupt source can be configured to generate an interrupt on either a positive and/or negative edge.

Preliminary

#### **INPUT/OUTPUT**

This pin is the master clock source for the SIB logic. This pin is available for use in one of two modes. First, SIBMCLK can be configured as a high-rate output master clock source required by certain external codec devices. In this mode all SIB clocks are synchronously slaved to the main PR31700 system clock CLK2X. Conversely, SIBMCLK can be configured as an input slave clock source. In this mode, all SIB clocks are derived from an external SIBMCLK oscillator source, which is asynchronous with respect to CLK2X. Also, for this mode, SIBMCLK can still be optionally used as a high-rate master clock source required by certain external codec devices.

#### **SPI Pins** 2.2.9

#### SPICLK:

SIBMCLK:

This pin is used to clock data in and out of the SPI slave device.

#### SPIOUT:

This pin contains the data that is shifted into the SPI slave device.

#### SPIIN:

This pin contains the data that is shifted out of the SPI slave device.

#### 2.2.10 UART and IR Pins

#### TXD:

This pin is the UART transmit signal from the UARTA module.

#### RXD:

This pin is the UART receive signal to the UARTA module.

#### **IROUT:**

This pin is the UART transmit signal from the UARTB module or the Consumer IR output signal if Consumer IR mode is enabled.

#### **IRIN:**

This pin is the UART receive signal to the UARTB module.

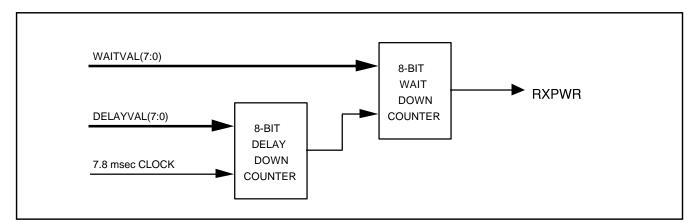

#### **RXPWR:**

This pin is the receiver power output control signal to the external communication IR analog circuitry.

#### CARDET:

INPUT

This pin is the carrier detect input signal from the external communication IR analog circuitry.

#### 2.2.11 Video Pins

#### FRAME:

This pin is the frame synchronization pulse signal between the Video Module and the LCD, and is used by the LCD to return it's pointers to the top of the display. The Video Module asserts FRAME after all the lines of the LCD have been shifted and transferred, producing a full frame of display.

#### DF:

OUTPUT

OUTPUT

This pin is the AC signal for the LCD. Since LCD plasma tends to deteriorate whenever subjected to a DC voltage, the DF signal is used by the LCD to alternate the polarity of the row and column voltages used to turn the pixels on and off. The DF signal can be configured to toggle on every frame or can be configured to toggle every programmable number of LOAD signals.

#### LOAD:

#### OUTPUT

OUTPUT

This pin is the line synchronization pulse signal between the Video Module and the LCD, and is used by the LCD to transfer the contents of it's horizontal line shift register to the LCD panel for display. The Video Module asserts LOAD after an entire horizontal line of data has been shifted into the LCD.

#### CP:

This pin is the clock signal for the LCD. Data is pushed by the Video Module on the rising edge of CP and sampled by the LCD on the falling edge of CP.

# PR31700 V0.3

OUTPUT

OUTPUT

INPUT

INPUT

OUTPUT

#### OUTPUT

OUTPUT

INPUT

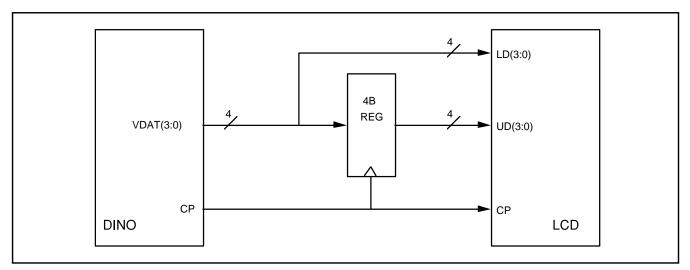

#### VDAT(3:0):

# OUTPUT

These pins are the data for the LCD. These signals are directly connected to the LCD for 4-bit non-split displays. For 4-bit split and 8-bit non-split displays, an external register is required to demultiplex the 4-bit data into the desired 8 parallel data lines needed for the LCD.

OUTPUT

OUTPUT

#### DISPON:

This pin is the display-on enable signal for the LCD.

#### **VIDDONE:**

This pin will provide a synchronization pulse external to the PR31700 that can be used to externally synchronize events to periods when the video is not shifting.

#### 2.2.12 Endianess Pin

#### **/LBENDIAN:**

This pin is used to select the endianess of the PR31700. The pin should be tied to GND for the little endian and VCC for the big endian mode of operation.

INPUT

INPUT

#### 2.2.13 Test Pins

#### **TESTSIU:**

The TESTSIU pin is used for two functions in the PR31700. The first function is to define if the Boot ROM is 16 or 32 bits wide. The second function is to enable or disable the Test Bypass Mode. This second mode allows external logic to initiate read or write transactions to the PR31700 registers. The TESTSIU mode is enabled by toggling this signal after the device has powered up. Once the function is enabled, if the TESTSIU pin is high when the bus is arbitrated (using /DREQ and /DGRNT), then external logic can initiate read and write transactions to the PR31700 registers. This pin is used for debugging purposes only. (refer to section 3.4 Test Modes for more detail for both function)

#### **TESTCPU:**

# INPUT

This pin allows numerous internal CPU core signals to be brought to the external PR31700 pins, in place of the normal signals assigned to these pins. The CPU core signals assigned to their respective pins during TESTCPU mode are vendor-dependent. The TESTCPU mode is enabled by asserting this TESTCPU signal, and this function is provided for generating test vectors for the CPU core. This pin is used for debugging purposes only and should be tied to GND for normal operation.

#### TESTIN:

### INPUT

This pin is reserved for vendor-dependent use and used for debugging purposes only. This pin should be tied to GND for enabling internal Phase Lock Loop (PLL) for normal operation.

RESERVED

#### 2.2.14 Spare Pins

#### NC5-1:

**NO CONNECT** These pins are reserved for future use and should be left unconnected.

#### RSRV1:

This pin is reserved for future use and should be connected to ground.

#### 2.2.15 Power Supply Pins

#### VDD (34 each):

+3.3V These pins are the power pins for the PR31700 and should be connected to the digital +3.3V power supply VSTANDBY.

GND

#### VSS (34 each):

These pins are the ground pins for the PR31700 and should be connected to digital ground.

NOTE: For some vendor-dependent implementations of PR31700, pin 131 may be used for a filter capacitor for the SYSCLK oscillator (capacitor connected between pin 131 and digital ground).

# PR31700 V0.3

### 2.3 Pin Usage Information

This section contains tables summarizing various aspects of the pin usage for the PR31700. Table 2-1 lists the standard/normal versus multi-function usage for each the PR31700 pin, if applicable. Those signal names shown in parentheses are test signals for debugging purposes only. The column showing the multi-function select signal and reset state indicates the internal control signal used to select the multi-function mode, as well as the default configuration of each multi-function pin during reset. The "Bus Arb State" column shows which pins are tri-stated whenever the /DGRNT signal is asserted in response to a /DREQ (external bus arbitration request).

| PR31700<br>pinout | standard function<br>(I = input,<br>O = output) | multi-function | multi-function<br>select<br>(reset state:<br>1 = multi-function<br>mode selected;<br>0 = standard<br>mode selected; | Bus Arb State |

|-------------------|-------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------|---------------|

| d[31:0]           | d[31:0]                                         | x              | x                                                                                                                   | Z             |

| a[12:0]           | a[12:0]                                         | х              | x                                                                                                                   | Z             |

| ale               | ale (O)                                         | х              | x                                                                                                                   | Z             |

| /rd               | /rd (O)                                         | х              | x                                                                                                                   | Z             |

| /we               | /we (O)                                         | х              | x                                                                                                                   | Z             |

| /cas0             | (/we0) (O)                                      | х              | x                                                                                                                   | Z             |

| /cas1             | (/we1) (O)                                      | х              | x                                                                                                                   | Z             |

| /cas2             | (/we2) (O)                                      | х              | x                                                                                                                   | Z             |

| /cas3             | (/we3) (O)                                      | х              | x                                                                                                                   | Z             |

| /ras0             | /ras0 (O)                                       | x              | x                                                                                                                   | Z             |

| /ras1             | (/dcs1) (O)                                     | х              | x                                                                                                                   | Z             |

| /dcs0             | /dcs0 (O)                                       | х              | x                                                                                                                   | Z             |

| dcke              | dcke (O)                                        | x              | x                                                                                                                   | Z             |

| dclkin            | dclkin (I)                                      | Х              | x                                                                                                                   |               |

| dclkout           | dclkout (O)                                     | Х              | x                                                                                                                   | Z             |

| dqmh              | dqmh (O)                                        | x              | x                                                                                                                   | Z             |

| dqml              | dqml (O)                                        | x              | x                                                                                                                   | Z             |

| /dreq             | /dreq (I)                                       | mio[27]        | miosel[27] (0)                                                                                                      |               |

| /dgrnt            | /dgrnt (O)                                      | mio[26]        | miosel[26] (0)                                                                                                      |               |

| sysclkin          | sysclkin (I)                                    | x              | x                                                                                                                   |               |

| sysclkout         | sysclkout (O)                                   | x              | x                                                                                                                   |               |

| c32kin            | c32kin (I)                                      | Х              | х                                                                                                                   |               |

#### Table 2-1. PR31700 Standard and Multi-Function Pin Usage

# PR31700 V0.3

#### Table 2-1. PR31700 Standard and Multi-Function Pin Usage (Continued)

| PR31700<br>pinout | standard function<br>(I = input,<br>O = output) | multi-function | multi-function<br>select<br>(reset state:<br>1 = multi-function<br>mode selected;<br>0 = standard<br>mode selected; | Bus Arb State |

|-------------------|-------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------|---------------|

| c32kout           | c32kout (O)                                     | x              | x                                                                                                                   |               |

| bc32k             | bc32k (O)                                       | mio[25]        | miosel[25] (1)                                                                                                      |               |

| vdat[3]           | vdat[3] (O)                                     | (berr)         | IrqTest (0)                                                                                                         |               |

| vdat[2]           | vdat[2] (O)                                     | (cpu_stall)    | IrqTest (0)                                                                                                         |               |

| vdat[1]           | vdat[1] (O)                                     | (irqhigh)      | IrqTest (0)                                                                                                         |               |

| vdat[0]           | vdat[0] (O)                                     | (irqlow)       | IrqTest (0)                                                                                                         |               |

| ср                | ср (О)                                          | х              | x                                                                                                                   |               |

| load              | load (O)                                        | х              | x                                                                                                                   |               |

| df                | df (O)                                          | x              | x                                                                                                                   |               |

| frame             | frame (O)                                       | х              | x                                                                                                                   |               |

| dispon            | dispon (O)                                      | х              | x                                                                                                                   |               |

| viddone           | viddone (O)                                     | х              | x                                                                                                                   |               |

| pwrcs             | pwrcs (O)                                       | x              | x                                                                                                                   |               |

| pwrint            | pwrint (I)                                      | x              | x                                                                                                                   |               |

| pwrok             | pwrok (I)                                       | х              | x                                                                                                                   |               |

| onbutn            | onbutn (I)                                      | x              | x                                                                                                                   |               |

| /cpures           | /cpures (I)                                     | x              | x                                                                                                                   |               |

| /pon              | /pon (O)                                        | х              | x                                                                                                                   |               |

| txd               | txd (O)                                         | mio[24]        | miosel[24] (0)                                                                                                      |               |

| rxd               | rxd (O)                                         | mio[23]        | miosel[23] (0)                                                                                                      |               |

| /cs0              | /cs0 (O)                                        | х              | x                                                                                                                   | Z             |

| /cs1              | /cs1 (O)                                        | mio[22]        | miosel[22] (0)                                                                                                      |               |

| /cs2              | /cs2 (O)                                        | mio[21]        | miosel[21] (0)                                                                                                      |               |

| /cs3              | /cs3 (O)                                        | mio[20]        | miosel[20] (0)                                                                                                      |               |

| /mcs0             | /mcs0 (O)                                       | mio[19]        | miosel[19] (1)                                                                                                      |               |

| /mcs1             | /mcs1 (O)                                       | mio[18]        | miosel[18] (1)                                                                                                      |               |

#### Preliminary

# PR31700 V0.3

#### Table 2-1. PR31700 Standard and Multi-Function Pin Usage (Continued)

| PR31700<br>pinout | standard function<br>(I = input,<br>O = output) | multi-function | multi-function<br>select<br>(reset state:<br>1 = multi-function<br>mode selected;<br>0 = standard<br>mode selected; | Bus Arb State |

|-------------------|-------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------|---------------|

| /mcs2             | /mcs2 (O)                                       | mio[17]        | miosel[17] (1)                                                                                                      |               |

| /mcs3             | /mcs3 (O)                                       | mio[16]        | miosel[16] (1)                                                                                                      |               |

| chifs             | chifs (I/O)                                     | mio[31]        | miosel[31] (1)                                                                                                      |               |

| chiclk            | chiclk (I/O)                                    | mio[30]        | miosel[30] (1)                                                                                                      |               |

| chidout           | chidout (I/O)                                   | mio[29]        | miosel[29] (1)                                                                                                      |               |

| chidin            | chidin (I/O)                                    | mio[28]        | miosel[28] (1)                                                                                                      |               |

| vcc3              | vcc3 (I)                                        | x              | x                                                                                                                   |               |

| io6               | io6 (I/O)                                       | x              | x                                                                                                                   |               |

| io5               | io5 (I/O)                                       | x              | x                                                                                                                   |               |

| io4               | io4 (I/O)                                       | x              | x                                                                                                                   |               |

| io3               | io3 (I/O)                                       | x              | x                                                                                                                   |               |

| io2               | io2 (I/O)                                       | x              | x                                                                                                                   |               |

| io1               | io1 (I/O)                                       | х              | x                                                                                                                   |               |

| io0               | io0 (I/O)                                       | х              | x                                                                                                                   |               |

| spiclk            | spiclk (O)                                      | mio[15]        | miosel[15] (0)                                                                                                      |               |

| spiout            | spiout (O)                                      | mio[14]        | miosel[14] (0)                                                                                                      |               |

| spiin             | spiin (I)                                       | mio[13]        | miosel[13] (0)                                                                                                      |               |

| sibsync           | sibsync (O)                                     | х              | x                                                                                                                   |               |

| sibdout           | sibdout (O)                                     | х              | x                                                                                                                   |               |

| sibdin            | sibdin (I)                                      | x              | x                                                                                                                   |               |

| sibmclk           | sibmclk (I/O)                                   | mio[12]        | miosel[12] (0)                                                                                                      |               |

| sibsclk           | sibsclk (O)                                     | x              | x                                                                                                                   |               |

| sibirq            | sibirq (I)                                      | x              | x                                                                                                                   |               |

| rxpwr             | rxpwr (O)                                       | x              | x                                                                                                                   |               |

| cardet            | cardet (I/O)                                    | x              | x                                                                                                                   |               |

| irout             | irout (O)                                       | х              | x                                                                                                                   |               |

# PR31700 V0.3

### Table 2-1. PR31700 Standard and Multi-Function Pin Usage (Continued)

| PR31700<br>pinout | standard function<br>(I = input,<br>O = output) | multi-function | multi-function<br>select<br>(reset state:<br>1 = multi-function<br>mode selected;<br>0 = standard<br>mode selected; | Bus Arb State |

|-------------------|-------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------|---------------|

| irin              | irin                                            | х              | X                                                                                                                   | x             |

| testsiu           | testsiu                                         | x              | x                                                                                                                   | x             |

| testcpu           | testcpu                                         | х              | x                                                                                                                   | x             |

| testin            | testin                                          | х              | X                                                                                                                   | x             |

| /cardreg          | /cardreg (O)<br>(showdino /CS)                  | mio[11]        | miosel[11] (1)                                                                                                      |               |

| /cardiowr         | /cardiowr                                       | mio[10]        | miosel[10] (1)                                                                                                      |               |

| /cardiord         | /cardiord                                       | mio[9]         | miosel[9] (1)                                                                                                       |               |

| /card1csl         | /card1csl (O)                                   | mio[8]         | miosel[8] (1)                                                                                                       |               |

| /card1csh         | /card1csh (O)                                   | mio[7]         | miosel[7] (1)                                                                                                       |               |

| /card2csl         | /card2csl (O)                                   | mio[6]         | miosel[6] (1)                                                                                                       |               |

| /card2csh         | /card2csh (O)                                   | mio[5]         | miosel[5] (1)                                                                                                       |               |

| /card1wait        | /card1wait (I)                                  | mio[4]         | miosel[4] (1)                                                                                                       |               |

| /card2wait        | /card2wait (I)                                  | mio[3]         | miosel[3] (1)                                                                                                       |               |

| /carddir          | /carddir (O)                                    | mio[2]         | miosel[2] (1)                                                                                                       |               |

| mfio[1]           | (master)                                        | mio[1]         | miosel[1] (1)                                                                                                       |               |

| mfio[0]           | (cpu_data_cyc)                                  | mio[0]         | miosel[0] (1)                                                                                                       |               |

| nc[6:1]           | spare                                           | x              | x                                                                                                                   |               |

| Reseved[0]        | spare                                           | x              | x                                                                                                                   |               |

| vdd - 34 each     | +3.3V                                           | x              | x                                                                                                                   |               |

| vss - 34 each     | GND                                             | x              | x                                                                                                                   |               |

Table 2-2 lists various power-down states and conditions for each PR31700 pin. The "Power-Down Control" column shows the conditions which trigger a power-down for each respective pin. This column also shows the reset state for each of these conditions.

The "/PON state" column defines the state of each pin at power-on reset (/PON). This condition is defined as initial power up of the PR31700, whereby the PR31700 is initialized and the PR31700 pins are reset to the state shown in the table. This state is entered after power is applied for the very first time (VSTANDBY is turned on but VCC3 is still turned off).

The "1st-time power-up state" column defines the state of each pin after power-up mode (RUNNING STATE) is executed for the first time. This mode is defined as VCC3 applied to the entire system and is initiated by the user pressing the ONBUTN while in the power-on reset (/PON) state. Note that the defined state of various pins for 1st-time power-up may depend on the configuration of external devices attached to these pins. After 1st-time power-up, the software could change the state of various pins to be different from those shown in the table. Thereafter, subsequent transitions from SLEEP STATE to RUNNING STATE might result in different states for these pins. The "power-down state" column defines the state of each pin during power-down mode (SLEEP STATE). This mode is defined as VCC3 turned off to the entire system, except for the PR31700 (RTC and interrupts alive) and any persistent memory.

| PR31700<br>pinout | Power-Down Control<br>powerdown =<br>/(vccon&vcc3)<br>(reset state) | /PON state | 1st time power-up state | power-down state |