# NUBI - A Revised ABI for the MIPS<sup>®</sup> Architecture

Document Number: MD00438 Revision 0.19 October 5, 2005

MIPS Technologies, Inc 1225 Charleston Road Mountain View, CA 94043-1353

Copyright © 2004–2005 MIPS Technologies, Inc. All rights reserved. PRELIMINARY INFORMATION FOR REVIEW ONLY. Copyright © 2004–2005 MIPS Technologies, Inc. All rights reserved.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS Technologies is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.

THIS DOCUMENT CONTAINS PRELIMINARY INFORMATION THAT IS PROVIDED FOR REVIEW ONLY AND SUBJECT TO CHANGE WITHOUT NOTICE. EXCEPT AS SET OUT ABOVE, ANY USE OF THIS INFORMATION (IN WHOLE OR IN PART) IS STRICTLY PROHIBITED.

MIPS TECHNOLOGIES DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION CONTAINED IN THIS DOCUMENT, AND MAKES NO COMMITMENT TO COMPLETE, UPDATE, KEEP CURRENT, PRODUCTIZE, LICENSE OR OTHERWISE COMMERCIALIZE THIS INFORMATION.

MIPS Technologies reserves the right to change the information contained in this document for any reason. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS Technologies, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies.

MIPS, MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS–3D, MIPS16, MIPS16e, MIPS32, MIPS64, MIPS–Based, MIPSsim, MIPSpro, MIPS Technologies logo, MIPS RISC CERTIFIED POWER logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, 5K, 5Kc, 5Kf, 20Kc, 24K, 24Kc, 24KE, 24KEc, 24KEf, 25Kf, 34K, R3000, R4000, R5000, ASMACRO, Atlas, "At the core of the user experience.", BusBridge, CorExtend, CoreFPGA, CoreLV, EC, FastMIPS, JALGO, Malta, MDMX, MGB, PDtrace, the Pipeline, Pro Series, QuickMIPS, SEAD, SEAD–2, SmartMIPS, SOC–it, and YAMON are trademarks or registered trademarks of MIPS Technologies, Inc. in the United States and other countries.

All other trademarks referred to herein are the property of their respective owners.

Template: B1.14, Built with tags: 2C MIPS32 ABI

## Table of Contents

| Table of Contents                                                   |    |

|---------------------------------------------------------------------|----|

| Figures                                                             | 5  |

| Tables                                                              | 6  |

| Chapter 1 Introduction, scope and goals                             | 7  |

| 1.1 Why does the MIPS Architecture need a new ABI?                  | 8  |

| ABI History                                                         |    |

| Specific Goals for NUBI                                             |    |

| 1.1.1 Introducing NUBI                                              |    |

| Chapter 2 Data Organization in a NUBI program                       |    |

| 2.1 Sizes of basic types                                            |    |

| 2.1 Sizes of basic types                                            |    |

| 2.3 "long double" floating point types                              |    |

| 2.5 long double mount point types                                   |    |

|                                                                     |    |

| 2.5 Alignment requirements for basic types                          |    |

| 2.6 Memory layout of basic types and how it changes with endianness |    |

| 2.7 Memory layout and alignment of derived types                    |    |

| 2.7.1 Bit fields in structures                                      |    |

| 2.8 Soft-float: floating point values in integer storage            |    |

| Chapter 3 Register and calling conventions                          |    |

| 3.1 NUBI register convention                                        |    |

| 3.1.1 Floating point register convention                            |    |

| 3.2 Register usage in legacy (o32, n32, n64) ABIs                   |    |

| 3.3 NUBI calling convention                                         |    |

| Stack- and Register-orientated calling conventions                  |    |

| 3.4 NUBI calling convention                                         |    |

| 3.5 NUBI stack frame standards                                      |    |

| Chapter 4 Programs in memory                                        | 24 |

| GP-relative data                                                    |    |

| Chapter 5 Object code formats                                       |    |

| 5.1 ELF object file - components                                    |    |

| 5.1.1 The ELF file header                                           |    |

| 5.1.2 The ELF Program header table                                  |    |

| 5.1.3 The ELF Section header table                                  |    |

| 5.1.4 Relocations and relocation types                              |    |

| 5.1.5 Notes sections for compiler/instruction set options           |    |

| Design principles for NUBI's ELF object standards                   |    |

|                                                                     |    |

| Chapter 6 Debug conventions                                         |    |

| A note on DWARF Debug information in the object files               |    |

| 6.1 Stack frame and code conventions for debugger navigation        |    |

| Chapter 7 Linux position-independent code                           |    |

| 7.1 How link units get into a program                               |    |

| 7.2 Global Offset Table ("GOT") organization                        |    |

| 7.2.1 The GOT and demand-loading                                    |    |

| 7.3 Conventions to help optimize position-independent code          |    |

| Optimizing intra-link-unit data references and calls                |    |

| Optimizing calls                                                    |    |

|                                                                     |    |

| Chapter 8 Signals, signal frames and the "sigcontext" structure | 51 |

|-----------------------------------------------------------------|----|

| 8.1 NUBI signal data structure                                  |    |

| Chapter 9 Thread-local storage                                  | 53 |

| Appendix A: References                                          |    |

| Other manuals on ABIs and object code                           | 54 |

| MIPS Architecture reference material                            |    |

| General MIPS reading                                            | 54 |

| Appendix B: Evolving NUBI                                       | 55 |

| Guidelines for early implementors                               | 55 |

| Compatibility testing                                           |    |

| Appendix C: 64-/32-bit interworking tricks                      | 56 |

| 32-/64-bit calling gasket                                       |    |

| Building gaskets                                                |    |

| Appendix D: Revision History                                    | 57 |

## Figures

| Figure 3-1: Stack layout in NUBI                                               | 22 |

|--------------------------------------------------------------------------------|----|

| Figure 4-1: The simplest memory map                                            |    |

| Figure 5-1: What's in an ELF file?                                             |    |

| Figure 5-2: Fields in the ELF "e_flags" entry for MIPS                         |    |

| Figure 5-3: Fields of a MIPS "jal" instruction                                 |    |

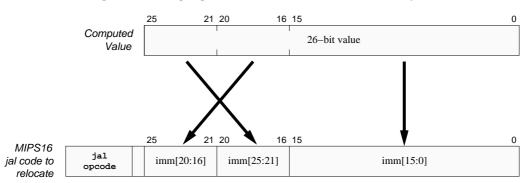

| Figure 5-4: Mangling address fields to relocate MIPS16 "jal"                   |    |

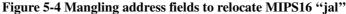

| Figure 5-5: Mangling address fields to relocate MIPS16 extended-immediate insn |    |

| Figure 7-1: Linux program memory image                                         |    |

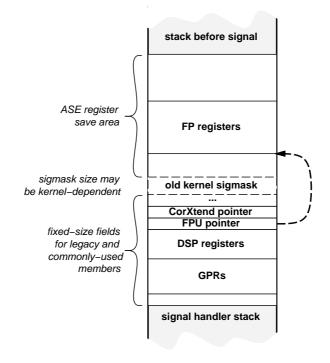

| Figure 8-1: Signal frame (sigcontext) elements for a MIPS/NUBI program         |    |

|                                                                                |    |

## Tables

| Table 2-1: Basic Data types and memory representations                        |    |

|-------------------------------------------------------------------------------|----|

| Table 2-2: C data types in memory                                             | 12 |

| Table 3-1: Register roles for NUBI                                            | 17 |

| Table 3-2: Floating point register usage conventions                          |    |

| Table 3-3: Legacy register conventions in o32, n32, n64                       |    |

| Table 5-1: ELF file header field values in NUBI                               | 27 |

| Table 5-2: Relationship between mainstream MIPS architecture revisions        | 29 |

| Table 5-3: Object code section types ("sh_type" values)                       |    |

| Table 5-4: Fields in the section header "sh_flags" word                       |    |

| Table 5-5: Machine/OS-dependent fields in the section headder "sh_flags" word |    |

| Table 5-6: Section names used in MIPS ABIs                                    |    |

| Table 5-7: Relocation type calculations for NUBI                              |    |

| Table 5-8: ASE numbers and values for NUBI notes sections                     | 43 |

|                                                                               |    |

## Introduction, scope and goals

The sections of this manual address what a useful ABI should encompass:

- Chapter 2 "Data Organization in a NUBI program" determines how you represent long int, int, short, char and pointer types.

- Chapter 3 "Register and calling conventions" describes registers reserved for particular purposes, stack conventions, who saves what, where arguments are found and where values are returned.

- Chapter 5 "Object code formats" describes the basic encompassing standard (ELF, usually) and its architecturespecific options. In particular this includes a set of "relocation types": a relocation type is a recipe for modifying a program to adapt to the run-time locations of data or function calls. In ELF, each relocation type gets a code number.

ELF object formats are (essentially) defined using C source code, and this manual references a particular version of source code from the GNU project.

NUBI will use DWARF 2 debug information. The debug formats are not described here, and you should refer to [DWARF2] or the source code.

- Chapter 6 "Debug conventions": to find its way through your program, the debugger relies on some conventions about stack arrangements, as well as explicit information passed through DWARF sections in the object file.

- Chapter 7 "Linux position-independent code": Linux applications and shared libraries come as binaries which permit both code and data to be conveniently relocated in the virtual address space.

- Chapter 8 "Signals, signal frames and the "sigcontext" structure": the old Unix signal mechanism lets an application choose to catch a signal event, providing a subroutine entry point for a *signal handler* (within the application program) which will be called by the kernel if the signal condition occurs.

This is more complicated than it might sound. Once the signal handler is running, the kernel simply believes the application is running, and forgets any saved state from the deferred pre-signal activity. Information required to restart the interrupted part of the user program is held on the user-space stack, in a structure called a *signal frame*.

The signal frame has to hold all the state (machine registers etc) for the interrupted user thread, but also has to fake a calling stack for the signal handler so that when it returns it will invoke the signeturn () system call.

The signal frame is a compatibility nightmare: it's affected by the Linux kernel build, the C library, and by the CPUs repertoire of registers. But it's definitely down to the ABI to define it!

- Chapter 9 "Thread-local storage": much discussed recently. Multi-threaded applications and libraries alike are commonly requiring language support, allowing programmers to specify "per-thread" variables and have the system implement something convenient and efficient.

- *Instruction set issues*: there have been many variants of the MIPS instruction set in different CPUs prior to the definition of MIPS32 and MIPS64. MIPS Technologies would like to see maximum use of those standards (and in particular release 2 of the MIPS32 and MIPS64 architecture specifications): but we recognize that the wider community includes users of slightly different instruction sets, and NUBI must work there too if it is to become a viable standard. NUBI will recognize a range of base architectures, each a superset of the last.

As is commonplace with modern architectures with embedded applications, there are also various optional extensions to the instruction set. For NUBI's purposes we only have to concern ourselves with instructions which might be generated by a compiler (and are available in user mode - privileged instructions are hand-coded with the assembler). So the extensions which matter are the MIPS16e compact ISA, and the MIPS DSP ASE's set of fractional, SIMD and multiply-accumulate variants.

Compliant NUBI programs carry in the object file an identifier for the base instruction set plus any extensions which account for all the user-mode instructions in the program.

The o32 ABI defines a fair number of object-code fields which encode ISA variants: but those fields filled up some time ago and their encoding is a cause of strife. NUBI judiciously extends the range of one field in the ELF header to define the base instruction set, but the use of instruction set extensions is in additional "option" object code sections, modelled on one of SGI's ELF extensions.

It is our intention to leave a fair amount of background and motivational information in this specification to keep it comprehensible (and thus provide some defense against corruption of the specification when people evolve it without having understood why things were done a particular way).

Where detail would duplicate that already provided in source code - notably in header files which define the "ELF" data structures - we will not recite that source code in this document. We will reference specific public versions of source code when necessary.

### 1.1 Why does the MIPS Architecture need a new ABI?

An "ABI" ("Application Binary Interface", though that hardly helps) is a set of rules governing compiled programs which - if followed - make the programs able to be linked together (for calling and to share data) and to be comprehensible to various useful bits of software - that includes debuggers, the Linux kernel, and run-time loaders.

Earlier MIPS ABIs were interpreted as machine-specific extensions to the cross-architecture [SVR4]; but the definition of OS services in a unix-like system now falls to POSIX and (specifically) Linux. This specification does not include the machine-independent parts of SVR4 ABI by reference or otherwise.

The existing MIPS ABIs were evolved substantially by Silicon Graphics Inc ("SGI") for various versions of their "Irix" OS; they are fairly typical of ABIs for Linux and other sophisticated operating systems. At least to date most MIPS embedded systems have got by using a subset of SGI's complicated ABI.

### **ABI History**

The MIPS ABI took shape as a set of register usage and calling conventions established from the earliest days of MIPS CPUs. It picked up the "ABI" acronym and a defined binding to object code with the AT&T-inspired "Unix System V" document which is rooted with [SVR4].

That process had coalesced as early as 1990 into much of the "o32" ABI which is widely used today. By about 1994 the ABI was expanded to encompass position-independent code and the ELF object code "syntax", and there have been no substantive and intentional changes since.

SGI pioneered 64-bit operating systems for MIPS in the early 1990s, and the o32 ABI was quite unsuitable for real 64-bit computing. SGI defined a 64-bit ABI called "n64" suitable for the largest applications; and then - belatedly realizing that n64's 64-bit pointer and long types bloated programs and caused portability problems to many applications which didn't need them - produced the very similar standard "n32", which differs primarily in having 32-bit pointers.

From 1995 or so SGI used solely 64-bit-capable MIPS CPUs, so they had no need to revisit a 32-bit ABI. As a result the embedded MIPS world is still stuck on the 20-year-old o32 standard. A series of talks five years ago failed to come up with a replacement.

Meanwhile, the perceived deficiencies of o32 have led to the proliferation of variants and more narrowly-focussed alternatives, to the point where there are now as many as 15 incompatible MIPS ABIs.

It may yet prove the least worst decision for us all to continue to use o32 "forever": but escaping from o32 could noticeably improve performance and ease various kinds of compatibility. So this is MIPS Technologies' proposal to do so: but this won't make sense unless we can take the community with us and end up with fewer ABIs - not just another family to add to the overlong list.

### **Specific Goals for NUBI**

- *Replace multiple existing ABIs* : a new family should be "good enough" for all the applications we can make contact with, and a seed for consolidation on a single standard.

- *Make better use of registers*: o32's limit of four argument registers causes unnecessary stack shuffling, and programs would run slightly better if we reserved more. Eight argument registers has been tried with success, notably by n64/n32.

We will define more "saved" registers. Not only is this common for other architectures, but it is evident that the GNU C compiler would quite often generate better code with a few more of these.

- Add a thread pointer: a per-thread pointer in a reserved register makes for efficient thread-local storage.

- Avoid unnecessary trouble with MIPS16e<sup>™</sup>: the "MIPS16" compact-code standard<sup>1</sup> uses half-size (16-bit) instructions, and one of the trade-offs made means it only has first-class access to eight general-purpose registers. We want to ensure the ABI's register use does not cause avoidable pain to MIPS16e programs<sup>2</sup>.

- *Better position-independent code ("PIC")*: all Linux shared libraries and applications are built PIC, so PIC efficiency matters. The general PIC code sequences for external data access and subroutine linkage are quite slow: we want to permit more optimizations of PIC calling and data referencing sequences.

- *Reduce 32-/64-bit incompatibility*: as systems grow to 64-bits we expect there to be some demand to interlink 32- and 64-bit code. This will never be seamless, but we believe it's worth making it practicable in controlled circumstances.

#### 1.1.1 Introducing NUBI

We've chosen this name, for now. We intend to improve on o32 with something simpler, but which prefers being trouble-free for the MIPS programming community over ground-breaking innovation.

Unfortunately there can't be just one NUBI. We believe there are three basic choices (related to the hardware) which will create NUBI variants, but which it's essential to support:

- Endianness: big- and little-endian programs are wholly incompatible. However, with some care this document covers both. When we need to distinguish them we'll use a suffix "L" or "B" for little/big-endian.

- Use of 64-bit integer instructions: whether the software is restricted to a MIPS32 instruction set ("NUBI32"), or can use the whole of MIPS64 ("NUBI64"). If you only ever use MIPS32 instructions all general-purpose registers might as well be 32-bits wide.

Even NUBI32 software is assumed to have access to double-precision floating point operations,

• Size of basic C types: we need to recognize a variant of NUBI64 with 64-bit pointers and long. I'm going to use NUBI64W ("W" for "wide") to denote this for now. Better suggestions welcomed.

In the medium term we expect the "narrow" 64-bit ABI which uses 32-bit pointers and long type to be more popular.

That leads to the following list of six main variants: NUBI32L, NUBI32B, NUBI64L, NUBI64B, NUBI64WL and NUBI64WB. We'll use "NUBI32" to mean "NUBI32L and NUBI32B", and - at a pinch - NUBI-L to mean "NUBI32L and NUBI32L and NUBI64L".

How's NUBI different from o32?

- *More argument registers* : eight instead of four.

- Argument registers shared with return-value registers : helps avoid having too many registers with pre-defined roles.

- Adds a thread pointer : for efficient TLS.

- *o32 was stack based, NUBI is register-based*: at bottom o32 used a stack-based calling convention, though it's disguised because the first, notional, 4×32-bit locations of the underlying stack argument structure are left unwritten, with the real data passed in four argument registers.

At the time o32 was introduced C programs were frequently written without "function prototypes" to describe the types of the arguments expected by an external function. Without any prototypes calls to functions with nonstandard arguments or (worse) with a variable number of arguments, like printf(), were difficult to get right. The underlying stack structure helped; a troubled function could save the four registers onto the stack to obtain a

<sup>1</sup> MIPS16e is the name for the instruction set provided by MIPS32 CPUs in 16-bit-instruction mode, whereas MIPS16 may be used for the name of the mode. MIPS16e adds a few instructions (which noticeably improve code compression) to the instruction set defined for earlier MIPS16 CPUs.

$^2$  Since the normal 32-bit MIPS register set treats pretty much all registers the same, the MIPS16e constraint should be unproblematic.

completely predictable memory structure for its arguments.

The stack-based structure also made it possible to pass data of derived types (structures, principally) by value. This has advantages: sometimes the data types you think are obscure turn out to be common.

In o32's generation, the critical example of this was the Fortran complex-number data type (which is a pair of floating point values).

However, in NUBI32's time the problem is more likely to be that we'd like to handle long long arguments and return values more efficiently. This might be worth a special case (which would cover complex and double-precision floating point numbers too).

• *o32 was irredeemably 32-bit, NUBI makes interworking possible* : a call between a NUBI64 program and a NUBI32 program will always need "gasket" code, but a gasket which is automatically produced would be a useful tool for complicated applications which are migrating from 32-bit to 64-bit, and where not all the components are recompiled together.

11

## Data Organization in a NUBI program

This chapter describes how data should be stored in memory in the run-time image of a NUBI program.

Those of you familiar with traditional ABIs for the MIPS architecture will note that it is entirely compatible with "o32".

The intent of this specification is to be restate the "o32" conventions, but the description has been completely re-written in the interests of clarity and brevity. If in that process we have unintentionally changed some obscure corner case in o32, we reserve the right to prefer a consistent interpretation of this text over o32.

For the purposes of this document memory is taken as an array of unsigned 8-bit quantities, whose index is the virtual address. For all compliant compilers the memory array corresponds to a C definition unsigned char [].

Like all modern computers, MIPS uses 2s-complement representation for signed integers - so in any data size "-1" is represented by binary all-ones. The overwhelming advantage of 2s-complement numbers is that the basic arithmetic operations (add, subtract, multiply, divide) have the same implementation for signed and unsigned data types<sup>3</sup>.

C integer data types come in signed and unsigned versions, which are always the same size and alignment. A declaration without a signed/unsigned keyword is interpreted as signed<sup>4</sup>.

In the medium term we expect to see some programs using fixed-point fractional data types, and perhaps even fixed-length vectors of small fixed-point types (which at the hardware level are carried in single registers). The fractional types will be declared by attaching an attribute to an integer declaration. A compiler may act on that declaration to give particular semantics to arithmetic operations: the ABI will only require that such data is managed according to the rules applicable to the underlying integer type.

Vector types could require an extension to NUBI. It's our goal that we should leave it possible to do that in a way which preserves compatibility for software which doesn't use vectors.

## 2.1 Sizes of basic types

Table 2-1 lists fundamental C data types and how they're implemented for MIPS architecture CPUs. We'll come back to the long and pointer types a bit later - their size changes according to whether you use the NUBI32 or NUBI64 ABI.

| C type      | MIPS asm name | size (bytes) |

|-------------|---------------|--------------|

| _Bool       | byte          | 1            |

| char        | byte          | 1            |

| short       | half          | 2            |

| int         | word          | 4            |

| longlong    | dword         | 8            |

| float       | .single       | 4            |

| double      | .double       | 8            |

| long double |               | 16           |

#### Table 2-1 Basic Data types and memory representations

<sup>&</sup>lt;sup>3</sup> At least, until the result has greater precision than the operands.

<sup>&</sup>lt;sup>4</sup> Some old code assumes that char is unsigned, and that behavior is available from GCC with a compiler flag. Strictly speaking, such behavior is non-compliant with NUBI.

## 2.2 Size of "long" and pointer types

Although these vary according to the type, in practice they're always the same as something else... For NUBI64W long is implemented just like the long long shown above, while for all other NUBI variants long is implemented just like an int.

It's good portability practice to have a pointer and long the same size, and all NUBI variants do so.

## 2.3 "long double" floating point types

We propose that NUBI follows in the footsteps of SGI's "n64" and "n32" standards and include an extended precision floating point number as a long double.

SGI implemented this as a pair of double variables whose sum is the number represented; one effectively holds the most significant bits of the number, the other the least significant bits. This cannot represent numbers outside the range of a regular double, but provides 50+ bits extra precision and is relatively efficient to compute with using a double-precision FPU. IBM's PPC64 ABI does the same.

We are inclined to use an SGI-compatible definition for NUBI; comments welcome.

## 2.4 Extended integer and "complex" types

GNU C has syntax for defining longer integer types, and modern C compilers are expected to support complex number types (corresponding to each floating point type). But for the purposes of this ABI such types will be dealt with exactly as if they consisted of a structure containing an array of scalars.

For extended integers the underlying scalar type will be the longest basic integer type which can be put together to form an extended type of the right bit-size.

We do not see any medium-term likelihood that any complex or extended types will get hardware support, and the largest alignment requirement for any object in NUBI shall be to an 8 byte unit.

## 2.5 Alignment requirements for basic types

Data types can only be directly handled by standard MIPS instructions if they are *naturally aligned*: that is, a 2-byte datum starts at an address which is even (zero modulo 2), a 4-byte datum starts at an address which is zero modulo 4, and an 8-byte datum starts at an address which is zero modulo  $8^5$ .

Consequently, NUBI requires that all the primitive data types be naturally aligned.

## 2.6 Memory layout of basic types and how it changes with endianness

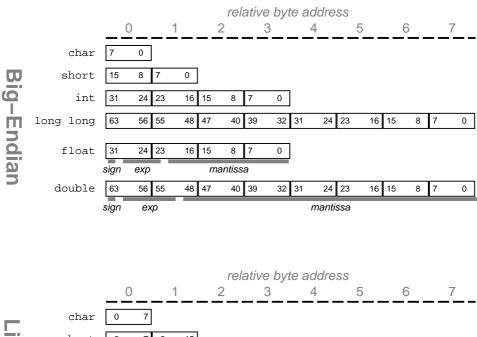

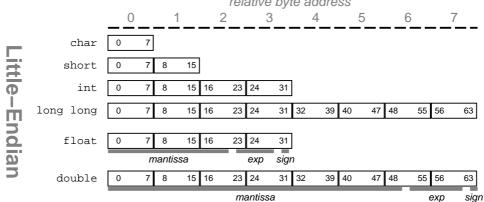

Table 2-2 shows how each basic type is laid out in our byte-addressed memory; the arrangement is different for bigendian and little-endian software.

In Table 2-2 the bit numbering is reversed between the two endianness layouts, which makes the bitwise depiction of the fields of floating point numbers easier to absorb (and prettier). It's a useful opportunity to give a warning: this neither adds nor subtracts any meaning. Bytes are indivisible 8-bit objects, and bit-numbers (where used in this specification) annotate the arithmetic significance of bits within an 8-, 16-, 32- or 64-bit integer type.

Each of these data types must be naturally aligned, as described above.

"Endianness" can be a troubling subject. If you are uneasy about it, read it up in [SMR].

<sup>&</sup>lt;sup>5</sup> The 8-byte alignment is not a hardware requirement for a MIPS32 CPU (32-bit integer registers) with no floating point hardware - which is likely to be the commonest CPU in embedded systems.

But of course the 8-byte alignment is only produced when you define 8-byte types such as long long and double. We think that making some 32-bit CPUs incompatible isn't worth the small saving in data memory.

Table 2-2 C data types in memory

### 2.7 Memory layout and alignment of derived types

Derived types are built by concatenating simple types, but inserting unused ("padding") bytes between items so as to respect the alignment rules<sup>6</sup>.

It's worth giving a couple of examples. Here's the byte offsets of data items in a struct mixed:

<sup>6</sup> Some compiler systems provide mechanisms to alter the alignment rules for particular data definitions: GNU C supports the data declaration attribute  $\__attribute((align(x)))$  and the slightly more ANSI #pragma pack(x). Both work to reduce the maximum padding by loosening alignment requirements down to 4 bytes, 2 bytes or none.

This allows you to model more possible data patterns with C data declarations, and the compiler will generate appropriate code (with some loss of efficiency) to handle the resulting unaligned basic data types. But such declarations are outside the scope of this document.

It's worth stressing that the byte offsets of the fields of constructed data types (*other than those using C bitfields*, see Section 2.7.1 "Bit fields in structures") are unaffected by endianness.

Constructed data types are aligned in memory to the largest alignment boundary required by a data type defined inside them. So a struct mixed will start on an 8-byte boundary; and that means that if you build an array of these structures you will need padding between each array element. C compilers provide for this by "tail padding" the structure to make it usable for an array, so sizeof(struct mixed) == 24 and the structure should really be annotated:

```

struct mixed {

char c;    /* byte 0 */

/* bytes 1-7 are ``padding'' */

double d;    /* bytes 8-15 */

short s;    /* bytes 16-17 */

/* bytes 18-23 are ``tail padding'' */

};

```

Just to remind you: the size (and consequently the alignment requirement) of pointer and long data types is 4 for NUBI32 and NUBI64, but 8 for NUBI64W.

#### 2.7.1 Bit fields in structures

C allows you to define structures which pack several short "bit field" members into one or more locations of a standard integer type. This is a useful feature for emulation, hardware interfacing, and perhaps for defining dense data structures, but is fairly incomplete. Bitfield definitions are nominally CPU-dependent and substantially endianness-dependent.

One can, for example, define a data structure which permits access to the various fields of a MIPS single-precision floating point number:

```

#if BYTE_ORDER == BIG_ENDIAN

struct ifloat {

unsigned int sign:1;

unsigned int bexp:8;

unsigned int mant:23;

};

#else /* little-endian */

struct ifloat {

unsigned int mant:23;

unsigned int bexp:8;

unsigned int sign:1;

};

#endif

```

In this case (as you'd hope and expect) the three fields are packed into one 32-bit int storage unit. How do the two cases differ? Well, for both endianness the bitfields are allocated with the first-defined field occupying the lowest byte-addressed part of the int. For big-endian, that means the high-order bits are occupied first; for little-endian, it's the low-order bits.

Does this make sense? Certainly some; if you tried to implement bitfields in a less endianness-dependent way, then in the following example struct fourbytes would have a different memory layout from struct fouroctets- and that doesn't seem reasonable:

```

struct fourbytes {

signed char a; signed char b; signed char c; signed char d;

}

struct fouroctets {

int a:8; int b:8; int c:8; int d:8;

}

```

A bitfield can only be packed inside one storage unit of its defined type; if we try to define a structure for a MIPS double-precision floating point number, the mantissa field contains part of two 32-bit int storage units and can't be defined in one go. The best we can do in ANSI C is something like this:

```

struct ieee754dp_konst {

unsigned sign:1;

unsigned bexp:11;

unsigned manthi:20; /* cannot get 52 bits into... */

unsigned mantlo:32; /* .. a regular C bitfield */

};

```

You're permitted to leave out the name of the field definition, so you don't have to invent names for fields which are just there for padding.

Bitfields of type other than a signed or unsigned int (or \_Bool) are not mandated by most C standards. But many compilers will support bitfields in longer integer types. If we were confident that all the compilers we would ever need support an unsigned long long bit field, we could have defined the double-precision floating point structure without having to split the mantissa over two fields.

The full alignment rules for bit-fields are complicated:

• As we said above, a bit-field must reside entirely in its *storage unit* - which is the enclosing, properly aligned location of the bit-field's defined type.

Thus a bit-field never crosses an alignment boundary of its defined type.

- Bit-fields can share their storage unit with other struct/union members, including members that are not bit-fields (to pack together, of course, the adjacent structure member would have to be of a smaller type).

- Structures inherit their own alignment requirement (recursively) from the alignment requirement of their most demanding field type. Named bit-fields will cause the structure to be aligned at least as well as the type requires.

Unnamed fields - regardless of their defined type - only force the storage unit or overall structure alignment to that of the smallest integer type which can accommodate that many bits.

• You might want to be able to force subsequent structure members to occupy a new storage unit. In a NUBIcompliant compiler you can do that with an *unnamed zero-width* field. Zero-width fields are otherwise pointless, and named zero-width fields are illegal.

You now know everything you need to map C data declarations to memory the NUBI way.

#### 2.8 Soft-float: floating point values in integer storage

Many CPUs oriented to the embedded market have no floating point hardware. When you compile C code using floating point for such a CPU you can leave it to the run-time system to catch the "coprocessor unusable" exceptions and emulate the floating point operations, but that's horribly inefficient.

Compilers will typically implement a "soft-float" option where floating point data types are implemented as if they were integers of the same size, and floating point operations implemented by a judicious mix of inline code and calls to a somewhat-invisible library.

If you want to be strict, you could see the soft-float option as yet another doubling of NUBI variants. But that would be counterproductive. Fortunately, the difference between regular and soft-float code can be confined to the

compiler. So we rule that when you compile soft-float then for all ABI purposes float will be treated as an alias for int, and double an alias for longlong.

Compilers should provide a flag in object files and in debug records which note the soft-float option; linkers should give a warning when mixing soft- and hard-float modules, but should not treat this as a fatal error which cannot be overriden.

## Register and calling conventions

The MIPS architecture makes nearly all the registers the same; only \$0 (which is just an always-zero bit bucket) and \$31 (used implicitly for a return address by the **jal** instruction which has no encoding space to pick a different register) are different.

It's a nice paradox that confronted by such an orthogonal architecture, software tools end up laying down some pervasive conventions which almost no software can break. And one of the conventions governs the use of the registers; in principle this is just part of the ABI.

MIPS currently favor a re-work of register conventions which is not backward compatible. It seems to be too constraining to conserve arbitrary assembler code, and relatively easy to automate conversion of assembler source in the face of any change we choose to make.

To refresh your memory on the older ABIs, refer to Section 3.2 "Register usage in legacy (o32, n32, n64) ABIs". But for NUBI we propose to:

- *Combine return-value and argument registers*: this is done in other ABIs and there's no obvious problem with it so it allows us to increase the number of re-assignable registers.

- Demote the "assembler temporary" register: compilers should not generate assembler code which implicitly uses registers, so should generate all their code under a ".noat". This (temporary) register should still be avoided when you're writing assembler code and want to use more complicated addressing modes in store instructions (etc).

- More saved and less temporary registers : four ex-temporary registers become "saved".

- *Define small-data-pointer as "saved"*: in particular the gp register used as the GOT pointer in PIC code or for "small-data" access in bare-iron code is redefined as "saved" and in programs which are neither GOT nor use small data, it's free for reuse.

In this case NUBI follows a change already made for n32/n64.

• Add a thread pointer : as widely agreed.

## 3.1 NUBI register convention

NUBI's register assignments are shown in Table 3-1.

### **3.1.1** Floating point register convention

MIPS CPUs which have FPU hardware have 32 floating point registers, whose assembler names are \$f0 - \$f31. Even 32-bit MIPS CPUs support the 64-bit IEEE double-precision format.

The now mostly obsolete 32-bit MIPS I CPUs do arithmetic only in the 16 even-numbered<sup>7</sup> registers f0-f30. NUBI does not officially support them.

All modern MIPS CPUs have 32 64-bit, full double-precision, registers and can do arithmetic with any of them.

Table 3-2 shows NUBI's convention. Where it is harmless to do so, we've remained consistent with n64's naming and register use conventions: but NUBI has 12 temporary, 12 saved and 8 argument registers (n64 had 14, 8, and 8 respectively, with two more dedicated for return values).

| Reg<br>No | Hardware constraint  | NUBI<br>Name | Use                                                    | o32<br>Name |

|-----------|----------------------|--------------|--------------------------------------------------------|-------------|

| \$0       | Always reads zero    | zero         |                                                        | zero        |

| \$1       |                      | AT/t3        | assembler temporary (additional temp in compiled code) | AT          |

| \$2       |                      | t0/pf        | PIC-code function call address/temporary               | v0          |

| \$3       | MIPS16 accessible    | gp/s13†      | global data pointer/GOT pointer/saved register         | v1          |

| \$4-\$7   |                      | a0-a3        | arguments/return values                                | a0-a3       |

| \$8-\$11  |                      | a4-a7        | more arguments                                         | t0-t3       |

| \$12-\$15 |                      | s0-s3        |                                                        | t4-t7       |

| \$16-\$17 | MIPS16 accessible    | s4-s5        | saved registers                                        | s0-s1       |

| \$18-\$23 |                      | s6-s11       |                                                        | s2-s7       |

| \$24      | MIPS16 cond. code    | t1           | temporary                                              | t8          |

| \$25      |                      | t2           | temporary                                              | t9          |

| \$26-\$27 |                      | k0-k1        | reserved for interrupt/trap handler                    | k0-k1       |

| \$28      |                      | tp           | thread pointer                                         | gp          |

| \$29      | MIPS16 stack pointer | sp           | stack pointer                                          | sp          |

| \$30      |                      | s12/fp       | saved register recycled as frame pointer if required   | s8/fp       |

| \$31      | link for jal         | ra           | Return address for subroutine                          | ra          |

Table 3-1 Register roles for NUBI

Table 3-2 Floating point register usage conventions

| Reg         |          | NUBI                            | n64       |

|-------------|----------|---------------------------------|-----------|

| No          | Name     | Use                             | Name      |

| \$f0        | ft10     |                                 | fv0       |

| \$f1        | ft0      | Temporary (not saved)           | ft0       |

| \$f2        | ft11     | remporary (not saved)           | fv1       |

| \$f3-\$f11  | ft1-9    |                                 | ft1-9     |

| \$f12-\$f19 | fa0-fa7  | Arguments/return values         | fa0-fa7   |

| \$f20-\$f23 | fs8-fs11 | Values saved over function call | ft10-ft13 |

| \$f24-\$f31 | fs0-fs7  | values saved over function can  | fs0-fs7   |

<sup>&</sup>lt;sup>†</sup> Non-position-independent code does not need a GOT pointer, and the use of the "small data" region is optional for bare-iron software. Where neither is specified, this becomes an additional "saved" register.

## 3.2 Register usage in legacy (032, n32, n64) ABIs

Table 3-3 shows how registers have been used to date.

| Register Nos | name  |                    | use             |                            |  |  |  |  |

|--------------|-------|--------------------|-----------------|----------------------------|--|--|--|--|

| \$0          | zero  | always zero        | always zero     |                            |  |  |  |  |

| \$1          | AT    | assembler tempo    | rary            |                            |  |  |  |  |

| \$2-\$3      | v0-v1 | return value from  | function        |                            |  |  |  |  |

| \$4-\$7      | a0-a3 | function argumer   | nts             |                            |  |  |  |  |

|              |       | <i>o32</i>         |                 | n32/n64                    |  |  |  |  |

|              | name  | use                | name            | use                        |  |  |  |  |

| \$8-\$11     | t0-t3 |                    | a4-a7           | more arguments             |  |  |  |  |

| \$12-\$15    | t4-t7 |                    | t0-t3           | temporaries (value         |  |  |  |  |

| \$24-\$25    | t8-t9 | temporaries        | t8-t9           | must be assumed            |  |  |  |  |

|              |       |                    |                 | lost over                  |  |  |  |  |

|              |       |                    |                 | subroutine call)           |  |  |  |  |

| \$16-\$23    | s0-s7 | saved registers (v | alue preserve   | ed over subroutine call)   |  |  |  |  |

| \$26-\$27    | k0-k1 | reserved for inter | rupt/trap han   | dler                       |  |  |  |  |

| \$28         | gp    | global data point  | er/GOT point    | er                         |  |  |  |  |

| \$29         | sp    | stack pointer      |                 |                            |  |  |  |  |

| \$30         | s8/fp | stack frame point  | ter if required | (additional saved register |  |  |  |  |

|              |       | if not)            |                 |                            |  |  |  |  |

| \$31         | ra    | Return address for | or subroutine   |                            |  |  |  |  |

#### Table 3-3 Legacy register conventions in o32, n32, n64

Chapter 3 Register and calling conventions

#### **3.3** NUBI calling convention

One of the most significant differences between contemporary ABIs is they way in which they pass arguments to functions. All agree that it's desirable to ensure that most arguments are passed in registers rather than on the stack. All - in the last resort, when arguments are very large or very numerous - resort to passing arguments in memory. However, there are two distinct styles of calling convention, with different characteristic advantages and problems.

### Stack- and Register-orientated calling conventions

• *Stack-orientated* : all arguments are notionally laid out on the stack. It's almost as if you were just applying the data-storage rules described in the previous chapter, though separate arguments are subject to an additional alignment requirement, to ensure that each starts on a register-sized boundary.

Then as many bytes of arguments as can be accommodated are sucked up into the registers available for argument passing, in order. Where the whole of a register-sized and aligned chunk contains a floating point value, it is passed in a floating point register.

Advantages: a stack-orientated mechanism allows you to pass any data type (even a structure passed by value) in registers. While this is not terribly useful in generality there are cases - like software quadprecision, or complex numbers represented as pairs of floating point - which are important in particular application areas.

There's a subdivision according to whether the nominal stack-space whose data is in registers should exist or not (it does in o32 and the 64-bit PowerPC specification, but does not exist in n64).

Disadvantages: mapping derived types to the stack is relatively complicated and liable to corner-case incompatibilities. It also requires a lot of copying, which is sometimes unnecessary.

We want to define sub-ABIs for 32-bit and 64-bit CPUs, and the way the "register size" unit determines the mapping of structure arguments creates troublesome incompatibilities.

• *Register-orientated* : all arguments are reduced to a form which will fit in a register, and passed in registers. When you run out of registers, you notionally put the argument into a register and save it to memory, then stack such register images.

For structure arguments, the form which fits in a register is a pointer to a structure in memory.

A naive register-orientated scheme requires that arguments which don't fit in a register be copied by the caller - C arguments passed by value should not be at risk of being modified by the callee. More sophisticated variants - which we'd choose - get the called function to make a copy of the argument, but only if it either writes or shares the address of that argument.

Register-orientated schemes only allocate stack space when there are more arguments than will fit in registers.

Advantages: it's simple to parse, for both machines and programmers. Moreover - particularly for the bulk of functions with less arguments than the number of argument registers - it minimizes the differences between the 32- and 64-bit versions.

Disadvantages: varargs can become ugly. In it's purist form, even small derived types (and things like complex numbers are treated like derived types) are passed by an implicit pointer which forces data out of registers. That can cost efficiency in applications where such structure-by-value arguments are ubiquitous.

The best-known legacy MIPS ABIs (o32, n32 and n64) are all stack-orientated. But MIPS Technologies are inclined to make NUBI register-orientated. Your input is particularly welcomed on this issue.

### 3.4 NUBI calling convention

The NUBI calling convention is register-, not slot-based<sup>8</sup>.

• Arguments : each argument is represented by a single register-sized value. Each of the first 8 arguments travels in the appropriate a0-7 register (or fa0-7 for scalar floating point arguments<sup>9</sup>). If there are more than eight arguments, further ones are formed *as if put in a register* and then saved on the stack into a 64-bit slot<sup>10</sup>.

We use floating point registers for double<sup>11</sup> and float arguments, and integers by value for all integer values which will fit in a register. Simple integer values are as if loaded into the register (ie they occupy the least-significant bits).

Derived types (structures etc) and non-standard scalar types are passed in a register if and only if their memorystored image is register-size aligned and fits into a register<sup>12</sup>. Derived types are mapped into a register by a register-size load (that's **1w** for NUBI32 and **1d** for NUBI64). Note that there is no guarantee that (even in rather simplest structures) a smaller-than-register integer field will end up conveniently positioned in the register.

All other arguments are passed by reference. The callee must copy the argument if it writes it or takes its address.

The long long int type is bigger than a register in NUBI32, and is then passed by reference. All bigger-thanregister derived types are, too.

- *Return value* : an integer value or derived type which fits in a single register is returned in a0, while a floating point value which fits in a register is in fa0. All other return values are returned via a pointer specified by the caller as an implicit extra argument, passed *first*.

- *GOT pointer*: gp will be the GOT pointer for PIC code (which is Linux-compatible). This is not programconstant (different link units must have different GOTs, and different modules may have different GOTs). Functions changing its value should save its value on entry and restore it on return (ie gp is treated as "saved", as is already done by n32/n64).

tp will be the thread pointer for thread-local storage. tp is expected to be set by the OS/library when the thread starts, and is read-only to normal compiled code. Code which does not use thread-local storage should not use this register at all.

<sup>7</sup> In this and in other matters it is influenced by the "EABI" proposals made by a group of GNU C workers some years ago. We've tried to ensure that NUBI is never arbitrarily different from EABI.

<sup>8</sup> This is different from PPC32 or EABI, which were willing to pass 16 arguments in registers if 8 of them happened to be floating point.

<sup>9</sup> Functions with more than 8 arguments are rare enough that we can afford to standardize on the big slots without wasting significant amounts of stack space.

<sup>10</sup> NUBI assumes that a compliant MIPS CPU implements a floating point unit which implements both double (IEEE-754 64-bit standard) and float (IEEE-754 32-bit standard) data types and operations, implement the MIPS architecture load/store double operations, and have 32 64-bit floating point registers.

Historic MIPS I CPUs had only 16 64-bit registers (formed by pairs of 32-bit registers) and did not support load/store double. NUBI doesn't provide for generating convenient floating point for those CPUs - though it does allow for soft float - see above.

<sup>11</sup> We are aware that pass-by-reference for long long - and perhaps for long double and \_complex double too - may sacrifice too much efficiency. We'll do some research to estimate how bad the impact would be, with particular attention to the Linux kernel and libraries.

We will consider an alternative where a derived/extended type which consists of a pair of identical scalars would be passed "as if" it was two arguments, in two registers. If we do that we'd also have to ensure that NUBI64 "skips" an argument register opportunity after an argument which fits in a 64-bit register but requires a pair of 32-bit registers, so subsequent arguments would remain in sync with NUBI32's... this is nasty, and we don't want to do it unless the impact of not doing so is bad.

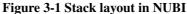

#### **3.5 NUBI stack frame standards**

A NUBI function must maintain the stack pointer at an 8-byte-aligned location at or below the lowest stack location used to date by the function, and restore it immediately before return.

A function's stack use includes, of course, any argument slots required by calling a function with more than 8 arguments.

All further rules about stack management are not essential for successful intercalling, but debuggers and other useful software tools assume these conventions<sup>13</sup>.

Here's a diagram:

#### Notes on the stackframe diagram Figure 3-1

- Argument slots : needed only when there are more than 8 arguments: each is 64 bits (8 bytes) in extent.

- Integer/FP register save area: integer saved registers in NUBI32 occupy 32-bit (4 bytes); all other register-save slots are 64-bit (8 bytes). Registers are saved with the lowest-numbered registers (that's *physically* lowest numbered) at the lowest memory positions.

- *framesize, regoffs, fregoffs*: these are the arguments to an assembler directive which will leave information for the debugger about the shape of the stack.

<sup>&</sup>lt;sup>12</sup> That is, these rules are made compulsory where they don't seem likely to cost anything, to avoid pointless diversity arising by chance.

#### Code Conventions for function stack management.

Commonly a NUBI function will adjust the stack pointer on entry by an amount known at compile time, and keep it there until it returns. The adjustment should be made prior to any branch or label at the start of the function.

Any function whose stack depth is unknown at compile time must maintain a frame pointer in the fp register.

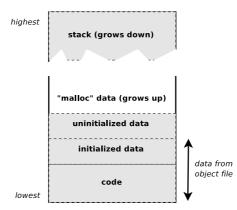

## Programs in memory

Running programs reside in computer memory. The ABI conventions don't determine the memory layout of the program, but the two certainly interact, and some of the practical complications of the ABI are there to allow users to build the memory map their application needs. So it's helpful to draw some pictures: we'll start with the simplest possible one in Figure 4-1.

#### Figure 4-1 The simplest memory map

Complications ensue if - as is often the case with bare-iron software - you are using "unmapped" memory regions like kseg0/kseg1, and need to fit your software onto the hardware's memory map. Sometimes code and read-only data must go in ROM, but writable data and stack must of course be in RAM. We're not going into that here.

## **GP-relative data**

Loading or storing a piece of data at an address known at link time requires a two-instruction sequence on MIPS (typically an **addiu** followed by a **lw/sw**.) But a common MIPS trick with bare-iron programs is to try to bring together the most commonly used data in a program (up to 64Kbytes of it), then to reserve the gp register as a pointer into the middle of this area. That allows data items to be loaded or stored with a single instruction. It's hard to figure out what is really the most commonly-used data in advance, so we pick all data items up to a specific size. With gcc the ``-S8'' option directs all data items whose size is 8 bytes or less to a separate "small data" region. Well, in fact there are two regions, one for initialized data (".sdata") and one for uninitialized (".sbss") - but they are eventually placed next to each other in the memory map.

This trick does not work for Linux applications built of multiple shared objects: it depends on the linker being able to figure out all the offsets from gp at link-time, which is not possible with dynamic loading. For this reason the PIC standard recycles the gp register to become the global offset table pointer.

## Object code formats

Object code is used to represent NUBI binary programs in computer files, and all NUBI object code uses a variant of the ELF format.

ELF was defined as part of the "System V Application Binary Interface" standard [SVR4] and the supplement which described the MIPS ("o32") variant is [SVR4\_MIPS]. This specification is compliant with base ELF, though not with o32: it aims to provide a reference which will replace the latter book<sup>14</sup>. Some generic ELF information is repeated here, as an aid to navigation.

Chapter 2 "Data Organization in a NUBI program" of this ABI defines a precise mapping from a C data structure to an array of bytes, so - within the context of the ABI - binary file data contents are unambiguously defined by C structures. That sounds suspiciously circular, but it works.

The software we will regard as a reference implementation for NUBI (and whose C header files will be authoritative) will be the GNU "binutils" distribution. The principle header files concerned will be:

| File                                 | What's defined here                                        |

|--------------------------------------|------------------------------------------------------------|

| <pre>src/include/elf/external.</pre> | Describes the structure fields of the header and key       |

|                                      | tables. It's "external" because it's describing the        |

|                                      | contents of the files, not the internal data structures of |

|                                      | the library which manipulates object file data.            |

| <pre>src/include/elf/common.h</pre>  | Describes standard values for fields.                      |

| <pre>src/include/elf/mips.h</pre>    | Field values which are specific to the MIPS architecture   |

### 5.1 ELF object file - components

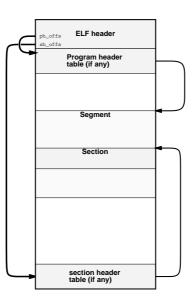

An ELF file might contains several piece as sketched out in Figure 5-1.

#### Figure 5-1 What's in an ELF file?

<sup>&</sup>lt;sup>13</sup> The most important audience for this chapter are programmers constructing compliant object code producers and consumers. None of this audience needs to have machine-independent ELF features reprised.

That is, it's a lump of binary which starts with an *ELF header*; that header tells you the file position of the *Program header table*, which locates and describes a number of chunks called *segments* and the *Section header table*, which locates and describes a number of *sections*. Segments and sections are often made of the same chunks of data: quite often a segment spans a number of different sections.

By original design, segments are for program loaders; sections are for intermediate build tools which write object files. Otherwise they have similar structures and many things which are "sections" early in the build process get packed into segments of the same name and very similar structure in the loadable file. When ELF was created the section/segment distinction was relatively straightforward: but the shared-library system of a modern OS like Linux defers the binding of names to real subroutines to program load time or even run time. As a result the loader does pretty much everything a linker needs to do...

An ELF file starts with its "ELF header". Typically the program header table follows immediately after, with the section header table at the end, and the section/segment contents in between. However, that's not required by the standard and should not be assumed by software which reads ELF.

A good way to get used to the contents of ELF files is to dump them out using the Linux (also available on other Unix-like OS') utility readelf.

#### 5.1.1 The ELF file header

An object file starts with an ELF file header. For NUBI32 that's an Elf32\_External\_Ehdr type, whereas for NUBI64 it's an Elf64\_External\_Ehdr. Both are defined in external.h like this:

```

typedef struct {

unsigned char e_ident[16];

/* ELF "magic number" */

unsigned char e_ident[16]; /* ELF imagic number ,

unsigned char e_type[2]; /* Identifies object file type */

unsigned char e_machine[2]; /* Identifies object file version */

unsigned char e_version[4]; /* Identifies object file version */

unsigned char e_entry[4]; /* Entry point virtual address */

unsigned char e_phoff[4]; /* Program header table file offset */

unsigned char e_flags[4]; /* Processor-specific flags */

unsigned char e_ehsize[2]; /* ELF header size in bytes */

unsigned char e_phentsize[2]; /* Program header table entry size */

unsigned char e_phentsize[2]; /* Program header table entry size */

unsigned char e_phentsize[2]; /* Program header table entry size */

unsigned char e_phnum[2]; /* Program header table entry count */

unsigned char e_shnum[2]; /* Section header table entry count */

unsigned char e_shstrndx[2];

/* Section header string table index */

} Elf32_External_Ehdr;

typedef struct {

unsigned char e_phnum[2]; /* Program header table entry count */

unsigned char e_shentsize[2]; /* Section header table entry size */

```

} Elf64\_External\_Ehdr;

With the exception of e\_ident, these fields are interpreted as integer values of various sizes. In the original SVR4 documents, the ELF header was defined using integer types - which are unambiguous, because their mapping to byte-addressable memory was defined in Chapter 2 "Data Organization in a NUBI program" above. But the GNU binutils project has found it more convenient to use char arrays, which makes the field sizes explicit. That somewhat obfuscates the structure definitions and the code which interprets ELF fields, but means you can make tools which work reliably in a cross-compilation environment (where the compilation host may have different endianness, basic-type size and alignment requirements).

Field values relevant to NUBI<sup>15</sup> are shown in Table 5-1:

<sup>&</sup>lt;sup>14</sup> We have omitted a number of historical field values associated with old MIPS ABIs. The accumulation of these values had become part of the problem rather than the solution. We believe that the NUBI object format will provide all the information linkers and loaders need, but some of the information which was formerly (and unsatisfactorily) squeezed into the header will appear in special "option" sections instead.

#### Chapter 5 Object code formats

| Field          | Legal value           |      | Meaning                                                                                                                                                                                                                                                                                 |

|----------------|-----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e_ident[0]     | ELFMAGO =             | 0x7F |                                                                                                                                                                                                                                                                                         |

| e_ident[1]     | ELFMAG1 =             | 'E'  | "Magic number" which provides informal evidence                                                                                                                                                                                                                                         |

| e_ident[2]     | ELFMAG2 =             | ' L' | that this is, indeed, an ELF file.                                                                                                                                                                                                                                                      |

| e_ident[3]     | ELFMAG3 =             | 'F'  |                                                                                                                                                                                                                                                                                         |

| e_ident[4]     | ELFCLASS32 =          | 1    | 32-bit ELF file. This value is critical, since it determines the size and interpretation of other fields,                                                                                                                                                                               |

|                |                       | 0    | even in the ELF header itself.<br>64-bit ELF file                                                                                                                                                                                                                                       |

|                | ELFCLASS64 =          |      |                                                                                                                                                                                                                                                                                         |

| e_ident[5]     | ELFDATA2LSB =         |      | Little-endian. This not only flags the endianness of the program encoded here, but the encoding of all the bigger-than-byte fields in the ELF file.                                                                                                                                     |

|                | ELFDATA2MSB =         | 2    | Big-endian                                                                                                                                                                                                                                                                              |

| e_ident[6]     |                       | 1    | A version number for the ELF header data structure.<br>Always 1 so far, and unlikely ever to change.                                                                                                                                                                                    |

|                | ELFOSABI_LINUX =      | 3    | Indicates a Linux-compatible ABI (or OS using                                                                                                                                                                                                                                           |

| e_ident[7]     |                       |      | compatible object file)                                                                                                                                                                                                                                                                 |

| c_racine [ , ] | ELFOSABI_STANDALONE = | 255  | Use this for code built non-PIC for "bare-iron" or single-address space RTOS.                                                                                                                                                                                                           |

| e_ident[8]     |                       |      | "ABI version" used to flag incompatible updates to an<br>evolving ABI. This does not seem to have been used<br>for architecture-dependent information.                                                                                                                                  |

|                | ET_REL =              | 1    | Relocatable file (typically an intermediate .o file).<br>NUBI programs should generate this value, but should<br>not rely on it for much.                                                                                                                                               |

| e_type         | ET_EXEC =             | 2    | Executable file                                                                                                                                                                                                                                                                         |

|                | ET_DYN =              | 3    | Shared object (dynamic library) file                                                                                                                                                                                                                                                    |

|                | ET_CORE =             | 4    | "Core file" synthesized by an OS to capture the state of a program for later debug.                                                                                                                                                                                                     |

| e_machine      | EM_MIPS =             | 8    | Originally narrowly defined for "MIPS I" big-endian.<br>But usage has evolved to mean that this denotes any<br>MIPS family architecture, and NUBI will stay with that<br>tradition.                                                                                                     |

| e_version      | EV_CURRENT =          | 1    | ELF version 1 - there has never been another, and probably never will be.                                                                                                                                                                                                               |

| e_flags        |                       |      | Packed field of MIPS-specific information, defined in<br>Figure 5-2 below. NUBI will retain compatibility with<br>the most-used fields, but will encode information about<br>the program encoding in object code sections rather<br>than trying to squeeze it into this overused field. |

| Table 5-1 EI | LF file header | field values | in NUBI |

|--------------|----------------|--------------|---------|

|--------------|----------------|--------------|---------|

#### A note on "e\_flags" and program/CPU compatibility

Earlier MIPS ABIs used many more  $e_flag$  field values than are described here. Some of these fields are no use any more: sometimes that's because all possible values are assigned but more are needed, but sometimes it just isn't clear why any ELF user would want to know.

NUBI object files will contain only the sub-fields shown in Figure 5-2 below.

#### Figure 5-2 Fields in the ELF "e\_flags" entry for MIPS

| 31  | 28 | 27           | 26 | 16 | 15 1 | 2 11 1 | ) 9  | 8          | 7 6 | 5    | 4 2 | 1   | 0 |

|-----|----|--------------|----|----|------|--------|------|------------|-----|------|-----|-----|---|

| ARC | H  | ARCH_ASE_M16 | ×  |    | ABI  | ×      | FP64 | 32BIT_MODE | ×   | ABI2 | ×   | PIC | × |

Where:

• ARCH: (e\_flags & EF\_MIPS\_ARCH) - this 4-bit value can be:

| ARCH                   | Meaning                          |

|------------------------|----------------------------------|

| E_MIPS_ARCH_1 = 0      | Program uses MIPS I instructions |

| $E_MIPS_ARCH_2 = 1$    | MIPS II†                         |

| $E_MIPS_ARCH_3 = 2$    | MIPS III                         |

| $E_MIPS_ARCH_4 = 3$    | MIPS IV                          |

| E_MIPS_ARCH_32 = 5     | MIPS32                           |

| $E_MIPS_ARCH_64 = 6$   | MIPS64                           |

| $E_MIPS_ARCH_32R2 = 7$ | MIPS32 release 2                 |

| $E_MIPS_ARCH_64R2 = 8$ | MIPS64 release 2                 |

Compliant NUBI programs may take any value from 1 through 8. NUBI does not aspire to supporting MIPS I hardware (though MIPS I integer code is unproblematic, the distinct early floating-point dialect will cause trouble).

The MIPS32 specification includes a description of the CPU's OS-only privileged resources. But the privileged instruction set is outside of the scope of this specification.

So for the purposes of this specification the following relationships can be guaranteed:

#### Table 5-2 Relationship between mainstream MIPS architecture revisions

|                                                       | $A \rightarrow B - A \text{ is a subset}$                                                                                                                             | et of B                                                                                                                                                      |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A A is the 32-bit-register<br>↓ only subset of B<br>B | $\begin{array}{rcl} \text{MIPS I} \rightarrow & \text{MIPS II} \rightarrow \\ & \downarrow \\ & \text{MIPS III} \rightarrow & \text{MIPS IV} \rightarrow \end{array}$ | $\begin{array}{ccc} \text{MIPS32} & \rightarrow & \text{MIPS32R2} \\ \downarrow & & \downarrow \\ \text{MIPS64} & \rightarrow & \text{MIPS64R2} \end{array}$ |

There was a specification for a "MIPS V" revision of the ISA. But it's really an "instruction set extension" (or "ASE") which adds paired-single floating point SIMD instructions to MIPS IV. A NUBI program's use of ASE instructions is communicated through special object code "option" section entries, as described in Section 5.1.5 "Notes sections for compiler/instruction set options" below.

- ARCH\_ASE\_M16: (e\_flags & EF\_MIPS\_ARCH\_ASE\_M16) 1 if code uses special half-sized instructions (as in MIPS16 and MIPS16e). NUBI programs should set this, but should read and provide authoritative information will be in object code "option" sections.