### 1. Introduction

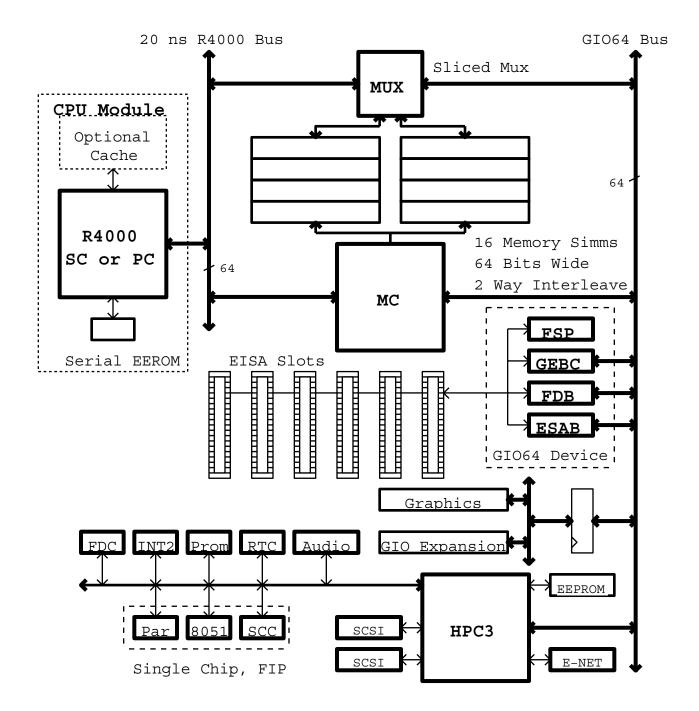

This document specifies the architecture of the MUX gate array for the Fast Forward project. This array connects the R4000 processor to the the memory system and the GIO64 Bus. Each of the two MUX parts handle 36 bits including parity. A block diagram of the full machine is shown below:

#### 1.1 MUX Block Diagram

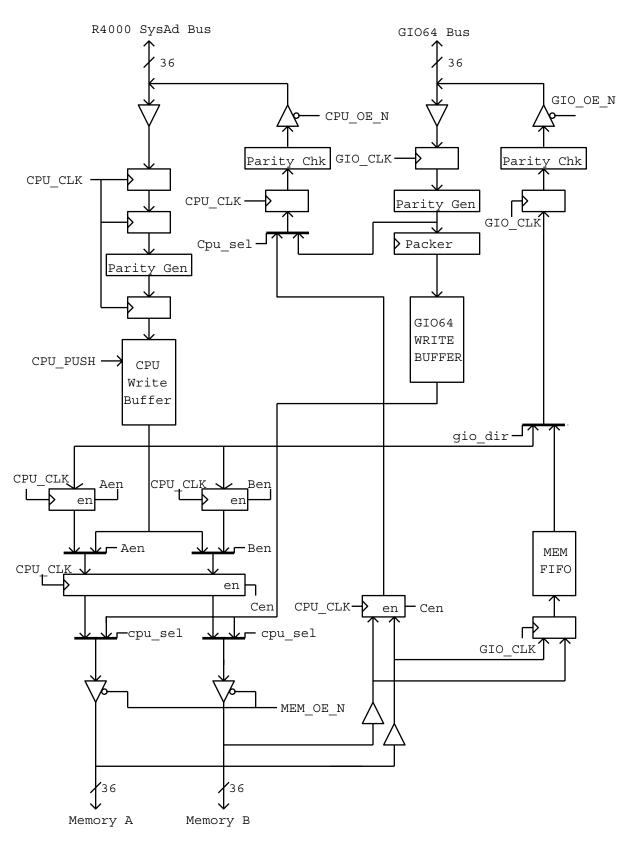

The MUX chip is a data path part that is used to move data between the processor, memory, and GIO64 bus. Since the CPU, and GIO64 run at different clock rates the MUX will help solve flow control problems over the asynchronous boundaries. This will be accomplished using a fifo on writes from the CPU. The GIO64 bus will initially run at 33 MHz so that it can be compatible with GIO, but will be able to run at speeds up to 40 MHz. The interface between GIO64 and memory will be completely synchronous to the GIO64 clock while the interface between the CPU and memory will also be synchronous to the CPU clock (50 MHz). The fifo in the MUX will be used as a write buffer on CPU writes to memory and GIO64. A block diagram of the chip is shown on the next page.

There are six different basic operations that are performed by the MUX chip. These are CPU reads and writes to memory, CPU reads and writes to a GIO64 device, and GIO64 reads and writes to memory. Each of there operations will be explained in detail in the following sections.

The MUX chips has two different clocks, the CPU clock and the GIO clock. Some operations are synchronous to the GIO clock and others are synchronous to the CPU clock. The MUX control signals from MC are used for both types of operations so there is a pair of select signals that indicate to the MUX chip which set of operations are being selected and the clock to flop the MUX control signals. All of the MUX control signals are flopped before they are used. The two select signals are cpu\_sel and gio\_sel. The cpu\_sel signals is active for CPU reads and and writes to main memory. The gio\_sel is active for the other four MUX operations. The two select signals will never both be asserted at the same time.

#### 1.2 Operation Select

Four control signals: gio\_sel, cpu\_sel, mux\_dir, and aen\_mem determine the current MUX operation. Either gio\_sel or cpu\_sel will be asserted during each of the operations. Cpu\_sel is synchronous to the cpu\_clk and gio\_sel is synchronous to the gio\_clk. Below is a chart of the different operations and the source of the bus parity signals:

| <u>cpu_sel</u> | <u>mux_dir</u> | <u>aen_mem</u> | Operation                                    |

|----------------|----------------|----------------|----------------------------------------------|

| 0              | 0              | 0              | CPU GIO64 device read. Parity is generated.  |

| 0              | 0              | 1              | GIO64 write to memory. Parity is generated.  |

| 0              | 1              | 0              | CPU GIO64 device write. Parity is generated. |

| 0              | 1              | 1              | GIO64 read from memory. Parity from memory.  |

| 1              | 0              | d              | CPU memory write. Parity is generated.       |

| 1              | 1              | d              | CPU memory read. Parity from memory.         |

During cpu memory reads and writes the aen\_mem signals is used for another function.

Note that this document references the input csize64, which is no longer an input to MUX. The csize64 input was ncluded to support R3000 processors, but was removed as an input when R3000 support was no longer needed for Fast Forward machines. The internal core of MUX still contains csize64 references, but this signal is pulled high internally

MUX Block Diagram

#### 1.3 Memory Reads and Writes By the CPU

During memory reads and memory writes by the CPU the cpu\_sel signal is asserted and the MUX control signals are clocked with the CPU clock.

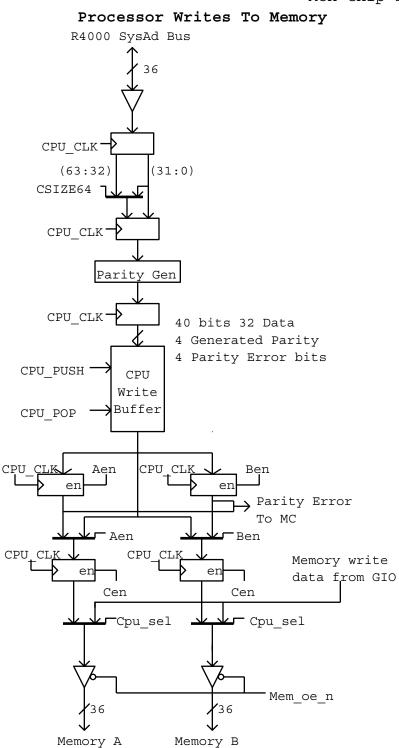

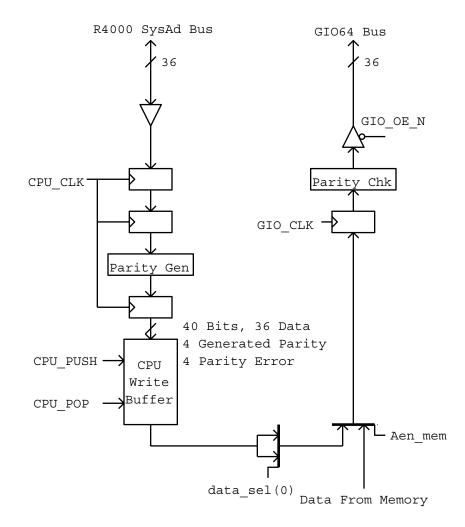

#### 1.3.1 Processor Writes to Memory

Processor writes to memory are a two part operation. In the first part the data is buffered in the MUX chip until it can be written into memory. The data comes over the sysad bus and is flopped three times so that the MC chip has time to determine if the data is valid and send a CPU\_PUSH signal to the MUX chip. If the data is not valid it will not be put into the fifo. The CPU memory write fifo is 32 entries deep. It is important to only put valid data into the fifo since there is no way to purge data from the fifo except to pop the fifo. The MC chip will keep track of how many data entries are in the fifo. CPU write data can be added to the MUX chip fifo at any time, even when the MUX chip is being used for a different operation. The cpu\_sel signals does not have to be asserted. The cpu\_push signal is a dedicated signal so that write data can be added to the fifo at any time. This fifo needs to be 32 entries deep so that it can hold two complete 32 word block writes from the CPU, which is the largest block write the CPU can issue.

The csize64 control signal is a static signal that indicates that the processor has a full 64 bit interface. This signal should be connected to the r4k signal from the MC chip. When this signal is not asserted bottom 32 bits of the sysad bus, (sysad(31:0)), are copied to the top bits of the bus, (63:32), between the first and second set of data input flops. This signal is deasserted for an R3000 processor and will duplicate the write data so that it is ready to write into memory. This signal is pulled high internally since R3000 support was not required for Fast Forward machines.

The second part of a CPU write is actually writing the data into memory. When the fifo is full the MC chip will deassert the processor cpu\_wrrdy\_n signal so that the processor will not issue another write until the data in the write fifo has been written. The MC chip arbitrates for the memory system and then writes the data into memory by popping the data off the fifo and flopping it into the memory data write flops while it is written to memory. During this part of the operation the cpu\_sel signal will be asserted. There are two sets of flops between the output of the CPU write buffer and the memory data outputs. The first set are controlled with the Aen and the Ben control signals. When either of these is active during a write to main memory by the CPU the CPU write buffer is popped. The second set of flops is controlled by the cen signal.

During the second part of the CPU write to memory the MUX control signals have the following meaning:

| gio_sel  | 0 | The gio_sel signal will be 0 during CPU writes to     |

|----------|---|-------------------------------------------------------|

|          |   | memory.                                               |

| cpu_sel  | 1 | The cpu_sel signal will always be 1 during the second |

|          |   | part of a memory write.                               |

| cpu_push | d | The CPU can still be writing data to the CPU memory   |

|          |   | buffer during a memory write.                         |

| cpu_mem_oe    |   | The memory output buffers will be turned on when this signal is asserted.                                                                                                                             |

|---------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| data sel(2:0) | d | These signals are not used.                                                                                                                                                                           |

| mux_dir       | 0 | This signal should be 0 for memory writes.                                                                                                                                                            |

| graphics(1:0) | d | These signals are not used.                                                                                                                                                                           |

| aen_mem       |   | When this signal is asserted the A register will be<br>enabled and the CPU memory buffer will be popped.                                                                                              |

| ben_ctrl      |   | When this signal is asserted the B register will be<br>enabled and the CPU memory buffer will be popped.                                                                                              |

| cen fifo      |   | When this signal is asserted the C register will be                                                                                                                                                   |

| _             |   | enabled. If both cen_fifo and aen_mem or ben_ctrl are<br>both asserted in the same cycle the data from the CPU<br>memory buffer instead of the A or B register will be<br>loaded into the C register. |

| giostb        | d | This signal is not used.                                                                                                                                                                              |

| par_flush     |   | When this signal is asserted bad memory parity will be<br>written into main memory. This is used for<br>diagnostics.                                                                                  |

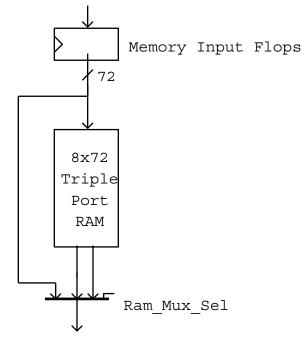

A block diagram of the CPU memory write path is shown on the following page.

MUX Chip Specification

The CPU Write buffer is implemented such that the data being written does not have to be available to be read the same cycle. This is accomplished by using the by-pass muxes with the Fifo\_Empty control signal. Also, if a read address changes value, the data associated with the new address does not have to be valid until two cycles later. This is accomplished by using a triple-port RAM and "ping-ponging" the read data from one port to another. The Ram\_Mux\_Sel control signal is used for this purpose. All additional control signals and muxes are included so that 65 MHz worse case timing can be met using RAMs currently available from LSI logic in their 100k series.

7

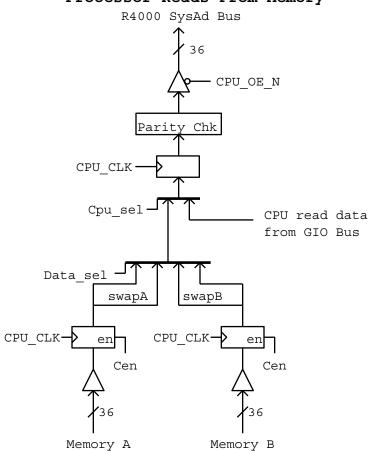

#### 1.3.2 Processor Reads From Memory

The MUX chip acts as an interleave multiplexer during CPU reads from memory. The data from memory comes in the two memory data ports on MUX and is flopped with the cpu\_clk. This flop is enabled with the cen\_fifo control signal. The data that is to be sent back to the processor is selected with the data\_sel control signals. Parity is then generated and checked. This data is then flopped and sent over the sysad bus.

The MUX control signals during processor reads from memory have the following meaning:

| gio_sel                  | 0 | The gio_sel signal will be 0 during CPU reads from memory.                                                                                                                                                                                   |

|--------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cpu_sel                  | 1 | The cpu_sel signal will be 1 during CPU reads from memory.                                                                                                                                                                                   |

| cpu_push                 | d | The CPU can still be writing data to the CPU memory<br>buffer during a memory read, although when the read is<br>returning data to the processor the sysad bus is busy<br>and so therefore can not be used by the CPU to send<br>write data. |

| csize64                  | d | This signal is not used.                                                                                                                                                                                                                     |

| cpu_mem_oe               |   | The sysad output buffers will be turned on when this signal is asserted.                                                                                                                                                                     |

| data_sel(2)              | d | This signals is not used.                                                                                                                                                                                                                    |

| <pre>data_sel(1:0)</pre> |   | These signal determine the source of the memory read<br>data.<br>0 - mem_a(63:32) -> sysad(31:0), d -> sysad(63:32)<br>1 - mem_b(63:32) -> sysad(31:0), d -> sysad(63:32)<br>2 - mem_a -> sysad<br>3 - mem_b -> sysad                        |

| mux_dir                  |   | This signal should be 1 for memory reads.                                                                                                                                                                                                    |

| graphics(1:0)            |   | These signals are not used.                                                                                                                                                                                                                  |

| aen_mem                  | d |                                                                                                                                                                                                                                              |

| ben_ctrl<br>cen_fifo     | d | This signal is not used.<br>When this signal is asserted the memory data input<br>flop is enabled.                                                                                                                                           |

| giostb                   | d | This signal is not used.                                                                                                                                                                                                                     |

| par_flush                | d | This signal is not used.                                                                                                                                                                                                                     |

A block diagram of the CPU memory read path is shown on the following page.

Processor Reads From Memory

#### 1.4 GIO Operations

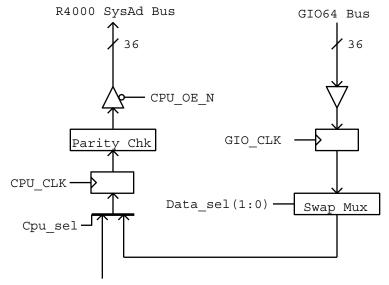

#### 1.4.1 Processor Reads From GIO64/EISA

The R4000 processor can issue a read to any device on the GIO64 bus. The address is sent to the MC chip which decodes it and then arbitrates for the GIO64 bus. Once it has been granted the bus it sends out the address on the GIO64 bus. The read data from the GIO64 device is flopped by the MUX chip and then sent through a mux where a word swap operation may be performed. The data is then flopped again and sent over the sysad bus back to the processor. There are two different word swap operations that are needed. The first is directly sending gio\_ad(63:0) to sysad(63:0). The second operation is to duplicate the lower word on the GIO64 bus onto both words of the sysad bus. This is necessary when the R4000 is reading from a 32 bit GI064 device. The third operation is moving the high word on the GI064 bus to the low word on the sysad bus. This is needed when the R3000 reads data from a 64 bit GIO64 device and the data is returned on the high bits of the bus.

The data that is returned to the processor is not synchronized in the MUX chip. Instead the data is held on the GIO64 bus for a few clocks before it is sent to the processor. As long as the cpu\_mem\_oe signal is asserted while gio\_sel is asserted, mux\_dir is deasserted, and aen\_mem is deasserted the data from the GIO64 bus will be flopped onto the sysad bus.

EISA reads look just like GIO64 device reads as far as the MUX is concerned.

The MUX control signals during processor reads from the GIO64 bus have the following meaning:

| gio_sel                  | 1 | This is a GIO operation.                             |

|--------------------------|---|------------------------------------------------------|

| cpu sel                  | 0 | This signal must be 0.                               |

| cpu_push                 | d | This signal will be 0 since the CPU is waiting for a |

|                          |   | read response.                                       |

| csize64                  | d | This signal is not used.                             |

| cpu_mem_oe               |   | The sysad output buffers will be turned on when this |

|                          |   | signal is asserted.                                  |

| data_sel(2)              | d | This signals is not used.                            |

| <pre>data_sel(1:0)</pre> |   | These signal determine the word swap operation.      |

|                          |   | 0 – gio_ad(63:0) -> sysad(63:0)                      |

|                          |   | 1 - gio ad(31:0) -> sysad(31:0)                      |

|                          |   | gio_ad(31:0) -> sysad(63:32)                         |

|                          |   | 2 - gio ad(63:32) -> sysad(31:0), d -> sysad(63:32)  |

|                          |   | 3 - reserved                                         |

| mux_dir                  | 0 | This signal should be 0 for GIO64 reads.             |

| graphics(1:0)            | d | This signal is not used.                             |

| aen_mem                  | 0 | This signal should be 0 for GIO64 reads.             |

| ben ctrl                 | d | This signal is not used.                             |

| cen fifo                 | d | This signal is not used.                             |

| giostb                   | d | This signal is not used.                             |

| par_flush                |   | This signal is not used.                             |

A block diagram of the CPU GIO64 read path is shown on the following page.

### Processor Reads From GIO64/EISA

Data from memory

#### 1.4.2 Processor Writes to GIO64

The R4000 processor can issue a write to any device on the GIO64 bus. Data is pushed into the cpu write fifo synchronous to the CPU\_CLK and popped out synchronous to the GIO\_CLK. The MC writes the data to the CPU write buffer using the cpu\_push signal. The MC chip must make sure the data is in the write buffer before it tries to pop it off the fifo. Cache writes are supported to devices that are 64 bits wide when the processor is a R4000. For each piece of data to be written the MC chip sends the MUX chip a GIO command. The GIO command is put into a twelve entry command fifo in the MUX chip and then as each piece of data is transferred the command fifo is popped. When the fifo is empty the MUX should turn off it gio\_ad output buffer. Normal GIO writes will only have one GIO command, but cache block writes to EISA can result in many commands. Part of the GIO command is which GIO delay signal to use to determine when the data has been transferred.

As each GIO command has been satisfied the MUX chip needs to wait a dead clock before transferring the data for the next GIO command. During cache block writes the CPU will assert masdly during these dead cycles.

The MUX control signals during processor writes to the GIO64 bus have the following meaning:

| gio_sel       | 1 | This is a GIO operation.                               |

|---------------|---|--------------------------------------------------------|

| cpu_sel       | 0 | This signal must be 0.                                 |

| cpu_push      | d | This signal is not used.                               |

| csize64       | d | This signal is not used.                               |

| cpu_mem_oe    | 0 | This signal should be 0.                               |

| data_sel(2:1) | d | These signals are not used.                            |

| data_sel(0)   |   | This signal determines the word swap operation.        |

|               |   | 0 – sysad(63:0) -> gio_ad(63:0)                        |

|               |   | 1 - sysad(31:0) -> gio_ad(63:32)                       |

|               |   | sysad(63:32) -> gio_ad(31:0)                           |

| mux_dir       | 1 | This signal should be 1 for CPU GIO64 writes.          |

| graphics(1:0) |   | These signals determine which delay signal is from the |

|               |   | addressed slave.                                       |

|               |   | 0 - slvdly                                             |

|               |   | 1 - grxdly0                                            |

|               |   | 2 - grxdly2                                            |

|               |   | 3 – grxdly3                                            |

| aen_mem       |   | This signal should be 0 for CPU GIO64 writes.          |

| ben_ctrl      |   | This signal is not used.                               |

| cen_fifo      | d | This signal is not used.                               |

| giostb        |   | This signal is asserted each time a new GIO command is |

|               |   | sent to the MUX.                                       |

| par_flush     | d | This signal is not used.                               |

|               |   |                                                        |

A block diagram of the CPU GIO64 write path is shown on the following page.

### Processor Writes To GIO64/EISA

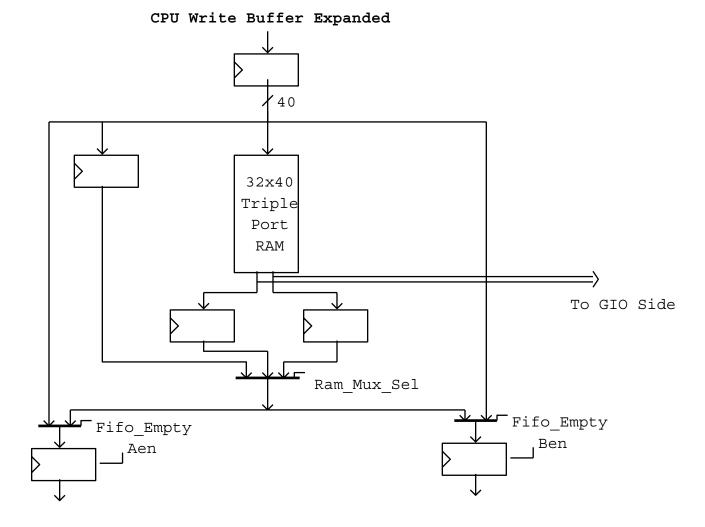

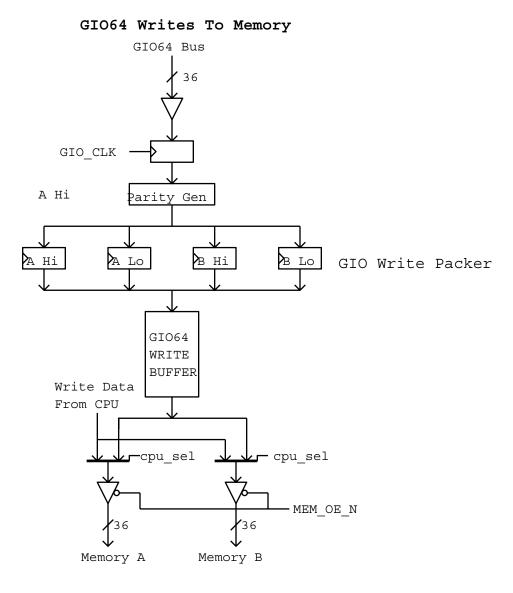

#### 1.4.3 GIO Writes To Memory

The MUX chip is used to buffer and pack data that is being written into main memory. The MUX chips packs data from 32 and 64 bit bus masters into 128 bit quad words to be written into main memory. There is also a six entry write buffer between the GIO64 bus and the memory data outputs. This isolates GIO bus stalls from the memory write.

GIO memory writes use GIO commands from the MC chip it indicate the packing operations that are to be performed. There is one GIO command for each piece of data that is transferred on the GIO64 bus. A GIO command is indicated by the MC chip asserting the giostb signal. The ben\_ctrl signal is used to pop data off the write fifo. This signal is not part of the GIO command. When the fifo is empty the fifo output should be the contents of the GIO packing registers. The graphics signal is used to indicate to the MUX chip which delay signal is from the bus master. If the write fifo in the MUX chip gets filled up the MC chip will assert slvdly to throttle the transfer and the MUX chip will not have any new GIO commands. Once a piece of data has been transferred on the bus, which can be determined by looking at the bus masters delay signal the GIO command is popped and the next GIO command is executed.

If the transfer gets preempted the par\_flush signal will be asserted to indicate that the GIO command fifo should be flushed of any valid entries and that the write fifo counters should be cleared.

The MUX chip does not have to worry about the write buffer being over filled. The MC chip has to keep track of how many entries are in the buffer. The MC chip controls how full the write buffer is by only sending out enough GIO commands to keep the write buffer full. When the MUX chip has run out of new GIO commands because the write buffer is full the MC chip will assert slvdly to stall the bus master.

The MUX control signals during GIO64 writes to main memory have the following meaning:

| gio_sel         | 1 | This is a GIO operation.                               |

|-----------------|---|--------------------------------------------------------|

| cpu sel         | 0 | This signal must be 0.                                 |

| cpu push        | d | This signal is not used.                               |

| csize64         |   | This signal is not used.                               |

| cpu mem oe      |   | This signal should be 0.                               |

| data $sel(2:0)$ |   | This signal determines which data in the packer        |

| —               |   | register is written.                                   |

|                 |   | 0 - Write A Lo, gio ad(31:0) -> A lo                   |

|                 |   | 1 – Write B Lo, gio ad(31:0) -> B lo                   |

|                 |   | 2 - Write A Hi, gio ad(31:0) -> A hi                   |

|                 |   | 3 - Write B Hi, gio ad(31:0) -> B hi                   |

|                 |   | 4 - Write A Hi and Lo, gio ad(31:0) -> A lo            |

|                 |   | gio $ad(63:32) -> A hi$                                |

|                 |   | 5 - Write B Hi and Lo, gio ad(31:0) -> B lo            |

|                 |   | gio ad(63:32) -> B hi                                  |

|                 |   | 6 - Reserved                                           |

|                 |   | 7 - Reserved                                           |

| mux dir         | 0 | This signal should be 0 for GIO64 writes to memory.    |

| graphics(1:0)   |   | These signals determine which delay signal is from the |

|                 |   | addressed slave.                                       |

|                 |   |                                                        |

|           | 0 - masdly                                             |

|-----------|--------------------------------------------------------|

|           | 1 - grxdly0                                            |

|           | 2 – grxdly2                                            |

|           | 3 – grxdly3                                            |

| aen mem   | 1 This signal should be 1 for GIO64 writes to memory.  |

| ben ctrl  | This signal is used to pop data off the write fifo.    |

| cen fifo  | This signal is used to push data onto the write fifo.  |

| giostb    | This signal is asserted each time a new GIO command is |

|           | sent to the MUX.                                       |

| par flush | When this signal is asserted the GIO command fifo and  |

|           | the GIO write fifo should be flushed.                  |

A block diagram of the GIO64 memory write path is shown on the following page.

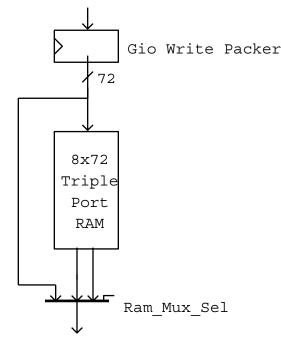

### GIO Write Buffer Expanded

To Memory Output Muxes

The GIO Write buffer is implemented such that the data being written does not have to be available to be read the same cycle. This is accomplished by using the by-pass muxes with the Ram\_MUX\_Sel control signal. Also, if a read address changes value, the data associated with the new address does not have to be valid until two cycles later. This is accomplished by using a triple-port RAM and "ping-ponging" the read data from one port to another. The Ram\_Mux\_Sel control signal is also used for this purpose. The additional control signal and mux are included so that 40 MHz worse case timing can be met using RAMs currently available from LSI logic in their 100k series.

#### 1.4.4 GIO Reads From Memory

The Mux chip is a data buffer and unpacker during GIO64 reads from main memory. Like GIO memory reads the memory writes work off of a GIO command. The GIO command determines when the GIO read data fifo is popped and which data is sent over the GIO64 bus. The graphics signal indicates which master delay signal should be used in determining when a piece of data has been transferred. When a piece of data has been transferred the GIO command fifo is popped and the next command should be executed in the following cycle. The cen fifo signal is part of the GIO command and indicates when the GIO read fifo should be popped. The ben\_ctrl signal is not part of the GIO command and is used to push data onto the GIO read fifo. The GIO memory read fifo is three entries deep.

When the par flush signal is asserted the GIO command fifo and the GIO read fifo should be flushed.

When the GIO command fifo is empty the MUX chip should stop driving the GIO bus. When the memory system can not keep up with a GIO64 device the MUX chip will run out of GIO commands. During this time the MC chip will assert slvdly to stall the GIO64 master.

The MUX control signals during GIO64 reads to main memory have the following meaning:

| gio_sel<br>cpu_sel<br>cpu_push<br>csize64<br>cpu_mem_oe<br>data_sel(2) | 1<br>0<br>d<br>0<br>d | This signal is not used.<br>This signal is not used.<br>This signal should be 0.<br>This signal is used to determine whether MUX should<br>drive the gio bus. This is included so that for back |

|------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| data_sel(1:0)                                                          |                       | to back reads, MUX does not turn off its drivers, and<br>then quickly turn them back on again<br>This signal determines which data is sent over the<br>GIO64 bus.                               |

|                                                                        |                       | 0 - Mem_A(63:0) -> GIO_AD(63:0)<br>1 - Mem_B(63:0) -> GIO_AD(63:0)<br>2 - Mem_A(63:32) -> GIO_AD(31:0), d -> GIO_AD(63:32)<br>3 - Mem_B(63:32) -> GIO_AD(31:0), d -> GIO_AD(63:32)              |

| <pre>mux_dir graphics(1:0)</pre>                                       | 1                     | This signal should be 1 for GIO64 reads from memory.<br>These signals determine which delay signal is from the<br>addressed slave.<br>0 - masdly<br>1 - grxdly0<br>2 - grxdly1<br>3 - grxdly2   |

| aen_mem<br>ben_ctrl<br>cen_fifo<br>giostb                              | 1                     | This signal is used to push data on the read fifo.<br>This signal is used to pop data off the read fifo.<br>This signal is asserted each time a new GIO command is<br>sent to the MUX.          |

| par_flush                                                              |                       | When this signal is asserted the GIO command fifo and<br>the GIO read fifo should be flushed.                                                                                                   |

A block diagram of the GIO64 memory read path is shown on the following page.

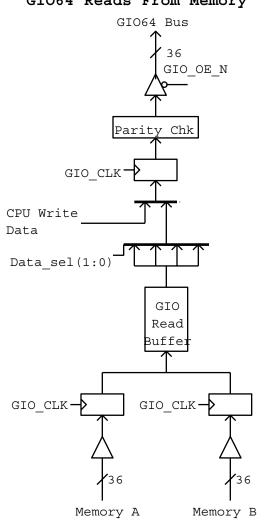

## GIO64 Reads From Memory

### GIO Read Buffer Expanded

To Data Swap Muxes

The GIO Read buffer is implemented such that the data being written does not have to be available to be read the same cycle. This is accomplished by using the by-pass muxes with the Ram\_MUX\_Sel control signal. Also, if a read address changes value, the data associated with the new address does not have to be valid until two cycles later. This is accomplished by using a triple-port RAM and "ping-ponging" the read data from one port to another. The Ram\_Mux\_Sel control signal is also used for this purpose. The additional control signal and mux are included so that 40 MHz worse case timing can be met using RAMs currently available from LSI logic in their 100k series.

### 2. MUX Pins

There are 189 signal pins on the mux chip including five signals for test which at this time are not defined. This part will be packaged in the 240 pin MQFP.

#### 2.1 Data Buses

| sysad(31:0)               | i/o | 32 bits of R4000 processor bus, made up of 4 bytes. |

|---------------------------|-----|-----------------------------------------------------|

|                           |     | SYSAD R4000 R4000                                   |

|                           |     | (31:24) is (63:56) or (55:48)                       |

|                           |     | (23:16) is (39:32) or (47:40)                       |

|                           |     | (15: 8) is (31:24) or (23:16)                       |

|                           |     | (7:0) is (7:0) or (15:8)                            |

| <pre>sysad_par(3:0)</pre> | i/o | Parity over sysad.                                  |

| gio_data(31:0)            | i/o | 32 bits of GIO64 data bus, made up of 4             |

|                           |     | bytes.                                              |

|                           |     | GIODATA GIO64 GIO64                                 |

|                           |     | (31:24) is (63:56) or (55:48)                       |

|                           |     | (23:16) is $(39:32)$ or $(47:40)$                   |

|                           |     | (15: 8) is $(31:24)$ or $(23:16)$                   |

|                           |     | (7: 0) is $(7: 0)$ or $(15: 8)$                     |

| gio_par(3:0)              | i/o | Parity over the gio_data.                           |

|                           | i/o | Memory interleave A data.                           |

|                           |     | Parity over mem_a.                                  |

| —                         | i/o | Memory interleave B data.                           |

| <pre>mem_b_par(3:0)</pre> | i/o | Parity over mem_b.                                  |

### 2.2 MUX Control Signals

Some of the control signals serve more than one function. The function is dependent on whether or not the GIO bus is involved in the operation. The giosel and cpusel signals are used to determine which function is the current function.

| giosel                   | in | Active during gio<->memory and cpu<->gio<br>transfers. Mutually exclusive with cpusel |

|--------------------------|----|---------------------------------------------------------------------------------------|

| cpusel                   | in | Active during cpu<->memory<br>transfers.Mutually exclusive with giosel                |

| cpu push                 | in | Push data onto the CPU write fifo.                                                    |

| csize64                  | in | This signal is used to indicate a full 64 bit transfer over the SYSAD bus.            |

|                          |    | 0 - Processor is a R3000<br>1 - Processor is a R4000                                  |

| cpu_mem_oe               | in | Control buffer driving memory bus A and B or sysad depending on dir.                  |

| <pre>data_sel(2:0)</pre> | in | Source of MUX data. Exact meaning depends on the operation taking place.              |

| mux_dir                  | in | Indicated source and destination of data,<br>used with aen_mem, gio_sel and cpu_sel.  |

| graphics(1:0)            | in | determines whether to use grfxdly(2:0) or slvdly.                                     |

|           |    | 0 - slvdly<br>1 - grxdly(0)<br>2 - grxdly(1)<br>3 - grxdly(2)                                                                                                                                                                 |

|-----------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| aen_mem   | in | When cpu_sel = 1 enables flop used to<br>catch data popped from the cpu write<br>buffer during write operations to memory<br>port A. when cpu_sel = 0 this is used to<br>help indicate the source and destination<br>of data. |

| ben_ctrl  | in | When cpu_sel = 1 enables flop used to<br>catch data popped from the cpu write<br>buffer during write operations to memory<br>port B. When cpu_sel = 0, is used to<br>control GIO memory fifo.                                 |

| cen_fifo  | in | When cpu_sel = 1 enables data into the<br>memory read and write flops. When cpu_sel<br>= 0 is used to control GIO memory fifo.                                                                                                |

| giostb    | in | Indicates that the GIO command which is<br>made up of some of the above signals is<br>valid and should be pushed onto the GIO<br>command fifo.                                                                                |

| par_flush | in | When cpu_sel = 1, generate bad parity on<br>memory write data. When cpu_sel = 0,<br>clean up state in MUX to complete the<br>current memory operations and set up for<br>the next memory operation.                           |

### 2.3 GIO64 Signals.

| masdly      | in | Master delay signal.                     |

|-------------|----|------------------------------------------|

| slvdly      | in | Slave delay signal.                      |

| grxdly(2:0) | in | Graphics delay signal. There are 3 of    |

|             |    | these signals.                           |

| mc_dly      | in | For GIO slave reads from memory an early |

|             |    | version of MC's delay signal. For GIO    |

|             |    | slave writes to memory a copy of MC's    |

delay signal.

### 2.3 Clock Signals.

| <pre>gio_clk gio_pll_lp1 gio_pll_lp2 gio_pl1_vdd gio_pl1_gnd cpu_clk cpu_pl1_lp1 cpu_pl1_lp2 cpu_pl1_vdd cpu_pl1_gnd pl1_reset n</pre> | in<br>out<br>in<br>in<br>in<br>out<br>in<br>in<br>in<br>in | GIO64 clock, 33 or 40 MHZ<br>PLL phase detector output<br>PLL loop filter from board<br>PLL power<br>PLL gnd<br>Processor clock, 50-65 MHZ<br>PLL phase detector output<br>PLL loop filter from board<br>PLL power<br>PLL gnd<br>PLL reset |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pll_reset_n                                                                                                                            | ın                                                         | PLL reset                                                                                                                                                                                                                                  |

## 2.4 Misc. Signals.

par\_err(3:0)

out Parity error detected on operation.

## 2.5 JTAG/ATPG Signals.

| jtdi  | in  | JTAG data in                 |

|-------|-----|------------------------------|

| jtdo  | out | JTAG data out                |

| jtms  | in  | JTAG mode select             |

| jtck  | in  | JTAG clock                   |

| tp0   | in  | JTAG tp0 mode select         |

| tp1   | in  | JTAG tp1 mode select         |

| entei | in  | ATPG tristate enable inhibit |

| Pin Number                 | Name                                                     | Туре  | In<br> | Out | Enable | Active |

|----------------------------|----------------------------------------------------------|-------|--------|-----|--------|--------|

| Pin 1 - C3                 | MC DLY                                                   | INPUT |        | 0   | 0      |        |

| Pin 2 – E5                 | GIOSTB                                                   | INPUT |        | 0   | 0      |        |

| Pin 3 – B3                 | GIOSEL                                                   | INPUT | 247    | 0   | 0      |        |

| Pin 4 - E6                 |                                                          | NC    | 0      | 0   | 0      |        |

| Pin 5 - C4                 | GIO DATA 31                                              | BIDIR | 293    | 323 | 259    | LOW    |

| Pin 6 – D6                 |                                                          | NC    | 0      | 0   | 0      |        |

| Pin 7 – D5                 | GIO DATA 30                                              | BIDIR | 292    | 322 | 259    | LOW    |

| Pin 8 – E7                 | GIO DATA 29                                              | BIDIR |        | 321 | 259    | LOW    |

| Pin 9–B4                   | VSS – –                                                  | POWER | 0      | 0   | 0      |        |

| Pin 10 - C5                | VDD                                                      | POWER | 0      | 0   | 0      |        |

|                            |                                                          | BIDIR | 289    | 320 | 259    | LOW    |

| Pin 11 - B5<br>Pin 12 - A5 | GIO DATA 27                                              | BIDIR |        | 319 | 259    | LOW    |

| Pin 13 - C6                | GIO DATA 26                                              | BIDIR |        | 318 | 259    | LOW    |

| Pin 14 - B6                | GIO DATA 25                                              | BIDIR |        | 316 |        | LOW    |

| Pin 15 – D7                |                                                          | BIDIR | 285    | 315 |        | LOW    |

| Pin 16 – A6                | VSS – –                                                  | POWER | 0      | 0   | 0      |        |

| Pin 17 – C7                | VDD                                                      | POWER | 0      | 0   | 0      |        |

| Pin 18 – E8                |                                                          | NC    | 0      | 0   | 0      |        |

| Pin 19 – B7                | PAR_FLUSH                                                | INPUT | 246    | 0   | 0      |        |

| Pin 20 - D8                | CPUSEL                                                   | INPUT | 162    | 0   | 0      |        |

| Pin 21 – A7                | GIO DATA 23                                              | BIDIR | 284    | 314 | 260    | LOW    |

| Pin 22 – E9                | GIO DATA 22                                              | BIDIR | 283    | 313 | 260    | LOW    |

| Pin 23 - C8                | GIO DATA 21                                              | BIDIR | 282    | 312 | 260    | LOW    |

| Pin 24 – D9                | GIO DATA 20                                              | BIDIR | 281    | 311 | 260    | LOW    |

| Pin 25 - B8                | GIO_DATA_21<br>GIO_DATA_20<br>GIO_DATA_19<br>GIO_DATA_18 | BIDIR | 279    |     | 260    | LOW    |

| Pin 26 - C9                | GIO DATA 18                                              | BIDIR |        |     |        | LOW    |

| Pin 27 – A8                | GIO DATA 17                                              | BIDIR | 277    |     |        | LOW    |

| Pin 28 - C10               |                                                          | BIDIR | 276    | 307 | 260    | LOW    |

| Pin 29 - B9                |                                                          | BIDIR | 275    | 305 | 261    | LOW    |

| Pin 30 - E10               | GIO_DATA_14                                              | BIDIR | 274    | 304 | 261    | LOW    |

| Pin 31 - B10               | VSS                                                      | POWER | 0      | 0   | 0      |        |

| Pin 32 - D10               | VDD                                                      | POWER | 0      | 0   | 0      |        |

| Pin 33 - B11               |                                                          | POWER | 0      | 0   | 0      |        |

| Pin 34 - D11               | GIO_DATA_13                                              | BIDIR | 273    | 303 | 261    | LOW    |

| Pin 35 – B12               |                                                          | BIDIR | 272    | 302 | 261    | LOW    |

| Pin 36 – E11               | GIO_DATA_11                                              | BIDIR |        | 301 | 261    | LOW    |

| Pin 37 – B13               | GIO_DATA_10                                              | BIDIR | 270    | 300 | 261    | LOW    |

| Pin 38 - C11               | GIO_DATA_9                                               | BIDIR | 268    | 299 | 261    | LOW    |

| Pin 39 - A14               |                                                          | BIDIR | 267    | 298 | 261    | LOW    |

| Pin 40 - C12               |                                                          | BIDIR | 266    | 297 | 262    | LOW    |

| Pin 41 - C13               |                                                          | BIDIR | 265    | 296 | 262    | LOW    |

| Pin 42 - D12               |                                                          | BIDIR | 264    | 325 | 262    | LOW    |

| Pin 43 - B14               |                                                          | BIDIR | 294    | 324 | 262    | LOW    |

| Pin 44 - E12               |                                                          | POWER | 0      | 0   | 0      |        |

| Pin 45 - A15               |                                                          | POWER | 0      | 0   | 0      |        |

| Pin 46 - D13               |                                                          | BIDIR | 291    | 317 | 262    | LOW    |

| Pin 47 - C14               |                                                          | BIDIR | 280    | 306 | 262    | LOW    |

| Pin 48 - E13               |                                                          | BIDIR | 269    | 326 | 262    | LOW    |

| Pin 49 - B15               |                                                          | NC    | 0      | 0   | 0      |        |

| Pin 50 - A16               |                                                          | POWER | 0      | 0   | 0      |        |

| Pin 51 - C15               |                                                          | BIDIR | 263    | 295 | 262    | LOW    |

| Pin 52 - B16               |                                                          | BIDIR | 330    | 334 | 258    | LOW    |

| Pin 53 - A17               |                                                          | BIDIR | 329    | 333 | 258    | LOW    |

| Pin 54 - C16               |                                                          | BIDIR | 328    | 332 | 258    | LOW    |

| Pin 55 - B17               |                                                          | BIDIR | 327    | 331 | 258    | LOW    |

| Pin 56 - D16               |                                                          | INPUT | 250    | 0   | 0      |        |

| Pin 57 - D14               |                                                          | INPUT | 249    | 0   | 0      |        |

| Pin 58 - C17               |                                                          | INPUT | 334    | 0   | 0      |        |

| Pin 59 - E14               | _                                                        | INPUT | 253    | 0   | 0      |        |

| Pin 60 - B18               | GRXDLY_0                                                 | INPUT | 251    | 0   | 0      |        |

|                            |                                                          |       |        |     |        |        |

|                                | Nororomoto Erborng   | (255 111 | 1 donag    | 00110) |        |        |

|--------------------------------|----------------------|----------|------------|--------|--------|--------|

| Pin Number                     | Name                 | Туре     | In         | Out    | Enable | Active |

|                                |                      |          |            |        |        |        |

| Pin 61 – D15                   |                      | NC       | 0          | 0      | 0      |        |

| Pin 62 – B19                   | GIO_PLL_LP1          | PLL      | 0          | 0      | 0      |        |

| Pin 63 – E15                   | VDD                  | POWER    | 0          | 0      | 0      |        |

| Pin 64 – D17                   | VSS                  | POWER    | 0          | 0      | 0      |        |

| Pin 65 - C18                   | VSS                  | POWER    | 0          | 0      | 0      |        |

| Pin 66 – E16                   | GIO PLL LP2          | PLL      | 0          | 0      | 0      |        |

| Pin 67 – C19                   | GIO CLK              | CLOCK    | 0          | 0      | 0      |        |

| Pin 68 – F16                   | —                    | NC       | 0          | 0      | 0      |        |

| Pin 69 – D18                   |                      | NC       | 0          | 0      | 0      |        |

| Pin 70 – F17                   | GIO PLL AGND         | PLL      | 0          | 0      | 0      |        |

| Pin 71 - E17                   | GIO PLL VSS          | POWER    | 0          | 0      | 0      |        |

| Pin 72 - G16                   | GIO PLL VDD          | POWER    | 0          | 0      | 0      |        |

| Pin 73 - D19                   | MEM A 31             | BIDIR    | 199        | 87     | 83     | LOW    |

| Pin 74 - E18                   |                      | חדחדח    | 198        | 88     | 83     | LOW    |

| Pin 75 - D20                   | MEM_A_30<br>MEM_A_29 | DIDIK    | 197        |        | 83     | LOW    |

|                                | MEM_A_29             |          |            | 89     |        |        |

| Pin 76 – E19                   | MEM_A_28             | BIDIR    | 196        | 90     | 83     | LOW    |

| Pin 77 – F18                   | MEM_A_27             | BIDIR    | 195        | 91     | 83     | LOW    |

| Pin 78 - E20                   | MEM_A_26             | BIDIR    | 194        | 92     | 83     | LOW    |

| Pin 79 - G17                   |                      | NC       | 0          | 0      | 0      |        |

| Pin 80 – F19                   |                      | NC       | 0          | 0      | 0      |        |

| Pin 81 – H16                   | MEM_A_25             | BIDIR    | 193        | 93     | 83     | LOW    |

| Pin 82 - G18                   | MEM_A_24             | BIDIR    | 192        | 94     | 83     | LOW    |

| Pin 83 - H17                   | MEM_A_23             | BIDIR    | 191        | 95     | 84     | LOW    |

| Pin 84 - F20                   | MEM_A_22             | BIDIR    | 190        | 96     | 84     | LOW    |

| Pin 85 – J16                   | MEM A 21             | BIDIR    | 189        | 97     | 84     | LOW    |

| Pin 86 – G19                   | MEM A 20             | BIDIR    | 188        | 98     | 84     | LOW    |

| Pin 87 – J17                   | MEM_A_19             | BIDIR    | 187        | 99     | 84     | LOW    |

| Pin 88 - H18                   | MEM A 18             | BIDIR    | 186        | 100    | 84     | LOW    |

| Pin 89 - J18                   | MEM A 17             | BIDIR    | 185        | 101    | 84     | LOW    |

| Pin 90 - G20                   | MEM_A_16             | BIDIR    | 184        | 102    | 84     | LOW    |

| Pin 91 - K18                   |                      | NC       | 0          | 0      | 0      | Lon    |

| Pin 92 - H19                   |                      | NC       | 0          | 0      | 0      |        |

| Pin 93 - K16                   |                      | NC       | 0          | 0      | 0      |        |

|                                |                      |          |            | 0      |        |        |

| Pin 94 - J19                   |                      | NC       | 0          |        | 0      |        |

| Pin 95 - K17                   |                      | NC       | 0          | 0      | 0      | T OF   |

| Pin 96 - K19                   | MEM_A_15             | BIDIR    | 183        | 103    | 85     | LOW    |

| Pin 97 – L17                   | MEM_A_14             | BIDIR    | 182        | 104    | 85     | LOW    |

| Pin 98 - L19                   | MEM_A_13             | BIDIR    | 181        | 105    | 85     | LOW    |

| Pin 99 - L16                   | MEM_A_12             | BIDIR    | 180        | 106    | 85     | LOW    |

| Pin 100 - M19                  | MEM_A_11             | BIDIR    | 179        | 107    | 85     | LOW    |

| Pin 101 - L18                  | MEM_A_10             | BIDIR    | 178        | 108    | 85     | LOW    |

| Pin 102 - N20                  | MEM_A_9              | BIDIR    | 177        | 109    | 85     | LOW    |

| Pin 103 - M18                  | MEM_A_8              | BIDIR    | 176        | 110    | 85     | LOW    |

| Pin 104 - N19                  | MEM_A_7              | BIDIR    | 175        | 111    | 86     | LOW    |

| Pin 105 - M17                  | MEM A 6              | BIDIR    | 174        | 112    | 86     | LOW    |

| Pin 106 - P20                  | PAR ERR 3            | OUTPUT   | 0          | 240    | 0      |        |

| Pin 107 - M16                  | PAR ERR 2            | OUTPUT   | 0          | 239    | 0      |        |

| Pin 108 - N18                  | PAR ERR 1            | OUTPUT   | 0          | 241    | 0      |        |

| Pin 109 - N17                  | PAR ERR 0            | OUTPUT   | 0          | 238    | 0      |        |

| Pin 110 - P19                  | VDD                  | POWER    | 0          | 0      | 0      |        |

| Pin 111 - N16                  | VSS                  | POWER    | 0          | 0      | 0      |        |

| Pin 112 - R20                  |                      | NC       | 0          | 0      | 0      |        |

| Pin 113 - P18                  | MEM A 5              | BIDIR    | 173        | 113    | 86     | LOW    |

| Pin 113 - P18<br>Pin 114 - R19 | MEM_A_5<br>MEM_A_4   |          | 173<br>172 |        |        | LOW    |

|                                |                      | BIDIR    |            | 114    | 86     |        |

| Pin 115 - T20                  | MEM_A_3              | BIDIR    | 171        | 115    | 86     | LOW    |

| Pin 116 - R18                  | MEM_A_2              | BIDIR    | 170        | 116    | 86     | LOW    |

| Pin 117 - T19                  | MEM_A_1              | BIDIR    | 169        | 117    | 86     | LOW    |

| Pin 118 - U20                  | MEM_A_0              | BIDIR    | 166        | 118    | 86     | LOW    |

| Pin 119 - T18                  | MEM_A_PAR_3          | BIDIR    | 168        | 119    | 82     | LOW    |

| Pin 120 - U19                  | MEM_A_PAR_2          | BIDIR    | 167        | 120    | 82     | LOW    |

|                                |                      |          |            |        |        |        |

| Mon 1111 CLOBB | Reference hibering |       | I achag | <i>ye come,</i> |        |        |

|----------------|--------------------|-------|---------|-----------------|--------|--------|

| Pin Number     | Name               | Туре  | In<br>  | Out             | Enable | Active |

| Pin 121 - P17  | MEM A PAR 1        | BIDIR | 201     | 121             | 82     | LOW    |

| Pin 122 - T17  | MEM A PAR 0        | BIDIR | 200     | 122             | 82     | LOW    |

| Pin 123 - P16  | TP1                | TEST  | 0       | 0               | 0      | HOW    |

| Pin 124 - U18  | TPO                | TEST  | 0       | 0               | 0      |        |

| Pin 125 - R17  | 110                | NC    | 0       | 0               | 0      |        |

| Pin 126 - V19  | JTDO               | JTAG  | 0       | 0               | 0      |        |

| Pin 120 - R16  | JTMS               | JTAG  | 0       | 0               | 0      |        |

| Pin 128 - V18  | VSS                | POWER | 0       | 0               | 0      |        |

| Pin 129 - U17  | PLL RESET N        | PLL   | 0       | 0               | 0      |        |

| Pin 130 - T16  | ENTEI              | TEST  | 0       | 0               | 0      |        |

| Pin 131 - W19  | JTDI               | JTAG  | 0       | 0               | 0      |        |

| Pin 132 - T15  | 0121               | NC    | 0       | 0               | 0      |        |

| Pin 133 - W18  | JTCK               | JTAG  | 0       | 0               | 0      |        |

| Pin 134 - U15  | CPU MEM OE         | INPUT | 163     | 0               | 0      |        |

| Pin 135 - V17  | MEM B 31           | BIDIR | 235     | 123             | 78     | LOW    |

| Pin 136 - T14  | MEM B 30           | BIDIR | 234     | 124             | 78     | LOW    |

| Pin 137 - U16  | MEM B 29           | BIDIR | 233     | 125             | 78     | LOW    |

| Pin 138 - W17  | MEM B 28           | BIDIR | 232     | 126             | 78     | LOW    |

| Pin 139 - V16  | MEM B 27           | BIDIR | 231     | 127             | 78     | LOW    |

| Pin 140 - W16  | MEM B 26           | BIDIR | 230     | 128             | 78     | LOW    |

| Pin 141 - X16  |                    | NC    | 0       | 0               | 0      | 2011   |

| Pin 142 - V15  | VDD                | POWER | 0       | 0               | 0      |        |

| Pin 143 - W15  | MEM B 25           | BIDIR | 229     | 129             | 78     | LOW    |

| Pin 144 - U14  | MEM B 24           | BIDIR | 228     | 130             | 78     | LOW    |

| Pin 145 - T13  | MEM_B_23           | BIDIR | 227     | 131             | 79     | LOW    |

| Pin 146 - X15  | MEM B 22           | BIDIR | 226     | 132             | 79     | LOW    |

| Pin 147 - U13  | MEM B 21           | BIDIR | 225     | 133             | 79     | LOW    |

| Pin 148 - V14  |                    | NC    | 0       | 0               | 0      | Lon    |

| Pin 149 - T12  | MEM B 20           | BIDIR | 224     | 134             | 79     | LOW    |

| Pin 150 - W14  | MEM B 18           | BIDIR | 222     | 136             | 79     | LOW    |

| Pin 151 - U12  | MEM B 19           | BIDIR | 223     | 135             | 79     | LOW    |

| Pin 152 - X14  | MEM B 17           | BIDIR | 221     | 137             | 79     | LOW    |

| Pin 153 - V12  | MEM B 16           | BIDIR | 220     | 138             | 79     | LOW    |

| Pin 154 - V13  | ······             | NC    | 0       | 0               | 0      | Lon    |

| Pin 155 - V11  | CEN FIFO           | INPUT | 161     | 0               | 0      |        |

| Pin 156 - W13  | BEN CTRL           | INPUT | 160     | 0               | 0      |        |

| Pin 157 - T11  |                    | NC    | 0       | 0               | 0      |        |

| Pin 158 - X13  |                    | NC    | 0       | 0               | 0      |        |

| Pin 159 - U11  | AEN MEM            | INPUT | 159     | 0               | 0      |        |

| Pin 160 - W12  | MEM B 15           | BIDIR | 219     | 139             | 80     | LOW    |

| Pin 161 - U10  | MEM B 14           | BIDIR | 218     | 140             | 80     | LOW    |

| Pin 162 - W11  | MEM B 13           | BIDIR | 217     | 141             | 80     | LOW    |

| Pin 163 - T10  | MEM B 12           | BIDIR | 216     | 142             | 80     | LOW    |

| Pin 164 - W10  | MEM B 11           | BIDIR | 215     | 143             | 80     | LOW    |

| Pin 165 - V10  | MEM B 10           | BIDIR | 214     | 162             | 80     | LOW    |

| Pin 166 - W9   | MEM B 9            | BIDIR | 213     | 145             | 80     | LOW    |

| Pin 167 - V9   | MEM B 8            | BIDIR | 212     | 146             | 80     | LOW    |

| Pin 168 - W8   | MEM B 7            | BIDIR | 211     | 147             | 81     | LOW    |

| Pin 169 - U9   | MEM_B_6            | BIDIR | 210     | 148             | 81     | LOW    |

| Pin 170 - X7   | DATA SEL 2         | INPUT | 244     | 0               | 0      |        |

| Pin 171 - T9   | DATA SEL 1         | INPUT | 245     | 0               | 0      |        |

| Pin 172 - V8   | DATA SEL 0         | INPUT | 243     | 0               | 0      |        |

| Pin 173 - U8   | READ               | INPUT | 256     | 0               | 0      |        |

| Pin 174 - W7   | VDD                | POWER | 0       | 0               | 0      |        |

| Pin 175 - T8   | VSS                | POWER | 0       | 0               | 0      |        |

| Pin 176 - X6   | MEM B 5            | BIDIR | 209     | 149             | 81     | LOW    |

| Pin 177 - V7   | MEM B 4            | BIDIR | 208     | 150             | 81     | LOW    |

| Pin 178 - W6   | MEM B 3            | BIDIR | 200     | 151             | 81     | LOW    |

| Pin 179 - X5   | MEM B 2            | BIDIR | 206     | 152             | 81     | LOW    |

| Pin 180 - V6   | MEM B 1            | BIDIR | 205     | 153             | 81     | LOW    |

|                |                    |       | 200     |                 | ~ -    |        |

| Pin         181         - WS         NC         0         0           Pin         182         - VS         VDD         POMER         0         0           Pin         184         - W4         VSS         POMER         0         0         0           Pin         185         US         VDD         POMER         0         0         0           Pin         185         US         VDS         BIDIR         203         156         82         LOM           Pin         186         - US         MEM_B_PAR_2         BIDIR         236         158         82         LOM           Pin         180         - V4         MEM_B_PAR_0         BIDIR         236         158         82         LOM           Pin         191         - V4         MEM_B_PAR_0         BIDIR         236         154         82         LOM           Pin         193         VV         VSS         POMER         0         0         0         161         161         161         161         161         161         161         161         161         161         161         161         161         161         161         161                                                                                                  | Pin Number    | Name           | Туре  | In<br> | Out | Enable | Active |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|-------|--------|-----|--------|--------|

| Pin         182         X4         MEM, B_0         BIDIR         202         154         81         LOW           Pin         185         V5         VDD         POWER         0         0         0           Pin         185         T         MEM, B_PAR_2         BIDIR         204         155         82         LOW           Pin         187         T         MEM, B_PAR_2         BIDIR         237         157         82         LOW           Pin         187         T         MEM, B_PAR_2         BIDIR         237         157         82         LOW           Pin         189         T         MEM, B_PAR_2         BIDIR         236         158         82         LOW           Pin         181         T         WEM, B_PAR_2         BIDIR         236         158         82         LOW           Pin         191         T         WEM, B_PAR_2         BIDIR         236         158         82         LOW           Pin         191         S         WEM         NC         0         0         0         179         159         159         158         82         LOW         159         169         179 <td>Pin 181 - W5</td> <td></td> <td></td> <td></td> <td></td> <td>0</td> <td></td> | Pin 181 - W5  |                |       |        |     | 0      |        |

| Pin         183         - V5         VDD         POWER         0         0           Pin         185         UT         MEM_B_PAR_3         BIDIR         204         155         82         LOW           Pin         186         UT         MEM_B_PAR_1         BIDIR         203         156         82         LOW           Pin         187         T         MEM_B_PAR_1         BIDIR         236         158         82         LOW           Pin         189         U         MEM_B_PAR_0         BIDIR         236         158         82         LOW           Pin         191         T         VJD         POWER         0         0         1           Pin         192         VJ         VSS         POWER         0         0         0           Pin         193         CUPULLVSD         POWER         0         0         0         0         1         191         195         100         0         0         0         1         191         191         101         101         101         101         101         101         101         101         11         101         101         101         101                                                                                             |               | MEM B 0        | BIDIR |        |     |        | LOW    |

| Pin         185         UVES         POWER         0         0         0           Pin         185         UT         MEM_B_PAR_2         BIDIR         203         156         82         LOW           Pin         185         T         MEM_B_PAR_2         BIDIR         237         157         82         LOW           Pin         187         T         MEM_B_PAR_0         BIDIR         236         158         82         LOW           Pin         189         UK         MEM_B_PAR_0         BIDIR         236         158         82         LOW           Pin         191         T         CO         0         0         0         0           Pin         193         UX         CPU_PLL_VDD         POWER         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                   |               |                |       |        |     |        |        |

| Pin         1185         US         MEM_B_PAR_3         BIDIR         204         155         82         LOW           Pin         1187         - T7         MEM_B_PAR_1         BIDIR         237         157         82         LOW           Pin         1187         - T7         MEM_B_PAR_1         BIDIR         237         157         82         LOW           Pin         139         - U6         NC         0         0         0           Pin         132         - Y4         MEM_B_PAR_3         BIDIR         236         158         82         LOW           Pin         132         - V4         MEM_B_PAR_3         DEDIR         0         0         0         0           Pin         137         V3         VSS         POMER         0         0         0           Pin         156         - R2         CPU_PLL         NC         0         0         0           Pin         156         - R2         CPU_PLL_LP1         PLL         0         0         0         0           Pin         137         VSS         POMER         0         0         0         0         0         0         0 </td <td></td> <td></td> <td></td> <td>0</td> <td>0</td> <td>0</td> <td></td>                      |               |                |       | 0      | 0   | 0      |        |

| Pin         186         US         MEM_B_PAR_2         BIDIR         203         156         82         LOW           Pin         188         -V4         MEM_B_PAR_0         BIDIR         236         158         82         LOW           Pin         189         -V4         MEM_B_PAR_0         BIDIR         236         158         82         LOW           Pin         191         -V3         RESET_N         INPUT         242         0         0           Pin         191         -V3         VSS         POWER         0         0         0           Pin         193         -U4         CPU_PLL_VSS         POWER         0         0         0           Pin         195         -W2         CC         0         0         0         0           Pin         196         R5         NC         0         0         0         0           Pin         198         -W2         CPU_PLL_LP2         PLL         0         0         0         0           Pin 203         -T3         VSS         POWER         0         0         0         0         0         0         0         0         0 <td>Pin 185 - U7</td> <td>MEM B PAR 3</td> <td>BIDIR</td> <td></td> <td></td> <td></td> <td>LOW</td>          | Pin 185 - U7  | MEM B PAR 3    | BIDIR |        |     |        | LOW    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pin 186 - U5  | MEM B PAR 2    |       |        |     |        |        |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pin 187 - T7  | MEM B PAR 1    |       | 237    |     |        |        |

| Pin         189         UC         NC         0         0           Pin         130         W3         REST N         INPUT         242         0         0           Pin         131         T5         VDD         POMER         0         0         0           Pin         133         U4         CPU_PLL_VDD         POWER         0         0         0           Pin         135         V2         CPU_PLL_VSS         POWER         0         0         0           Pin         135         R         K4         CDC         0         0         0           Pin         135         R         K4         CPU_PLL_LP2         PLL         0         0         0           Pin         130         CPU_PLL_AGND         PLL         0         0         0         0           Pin 201         T4 <mux dtr<="" td="">         INPUT         164         0         0         0         0         0           Pin 202         T2         SYSAD_30         BIDIR         26         57         76         LOW           Pin 203         T3         VSSAD_28         BIDIR         26         58         76         LO</mux>                                                                                                  | Pin 188 - V4  | MEM B PAR 0    | BIDIR |        |     |        |        |

| Pin         190         WSS         POWER         0         0           Pin         191         192         V3         VSS         POWER         0         0           Pin         193         U4         CPU_PLL_VDD         POWER         0         0         0           Pin         194         TS         CPU_PLL_VSS         POWER         0         0         0           Pin         196         R5         NC         0         0         0         0           Pin         198         R4         CPU_PLL_PS         PLL         0         0         0           Pin         198         R4         CPU_PLL_AGND         PLL         0         0         0           Pin<201                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |                |       |        |     |        |        |

| Pin         191         - T6         VDD         POWER         0         0           Pin         192         - V3         VSS         POWER         0         0           Pin         194         - T5         CPU_PLL_VDD         POWER         0         0           Pin         195         - W2         CPU_CLK         CLOCK         0         0           Pin         197         V2         NC         0         0         0           Pin         197         V2         NC         0         0         0           Pin         198         - R4         CPU_PLL_LP1         PLL         0         0         0           Pin         200         - P5         CPU_PLL_AOND         PLL         0         0         0           Pin 201         - T4         MUX_DIR         INPUT         164         0         0           Pin 202         - U2         CS         SYSAD_30         BIDIR         28         61         76         LOW           Pin 203         - T3         SYSAD_28         BIDIR         24         56         76         LOW           Pin 204         POWER         0         0<                                                                                                                  |               | RESET N        | TNDIT | 212    |     |        |        |

| Pin         193         V4         CPU PLL_VDD         POWER         0         0         0           Pin         193         TS         CPU PLL_VSS         POWER         0         0           Pin         195         W2         CPU_CLK         CLOCK         0         0           Pin         195         W2         CPU_CLK         CLOCK         0         0           Pin         197         V2         NC         0         0         0           Pin         198         R4         CPU_PLL_LP1         PLL         0         0         0           Pin         203         T3         CPU_PLL_ARID         PLL         0         0         0           Pin         203         T3         VSS         POWER         0         0         0           Pin         205         T2         SYSAD_31         BIDIR         29         61         76         LOW           Pin         205         T3         SYSAD_28         BIDIR         26         57         76         LOW           Pin         207         T1         SYSAD_28         BIDIR         23         55         76         LOW <td>Pin 191 - T6</td> <td>VDD</td> <td>POWER</td> <td>0</td> <td></td> <td></td> <td></td>                              | Pin 191 - T6  | VDD            | POWER | 0      |     |        |        |