# GIO BUS SPECIFICATION

version 1.1 (draft) 7April 1992

# Copyright January 1992 Silicon Graphics, Inc. All Rights Reserved

This document contains proprietary and confidential information of Silicon Graphics, Inc., and is protected by Federal copyright law.

The contents of this document may not be copied nor duplicated in any form, in whole or in part, without the express written consent of Silicon Graphics, Inc.

## U.S. Government Limited Rights

Use, duplication, or disclosure of the technical data contained in this document is subject to restrictions as set forth by the Government in subdivision (b)(2) of the Rights in Technical Data and Computer Software clause at 52.227-7013.

Contractor/manufacturer is Silicon Graphics, Inc., 2011 North Shoreline Road, Mountain View, CA 94039-7311.

# **Table of Contents**

# Chapter One: Overview

| 1.1  | Introduction                                             | 1-1   |

|------|----------------------------------------------------------|-------|

| 1.2  | Conventions Used in this Document: Signal Names          | 1-1   |

| Ch   | apter Two: GIO32 Specification                           |       |

| 2.1  | Introduction                                             | 2-1   |

| 2.2  | Conventions Used in this Chapter                         | 2-1   |

| 2.3  | GIO32 Transfer Size and Preemption                       | 2-2   |

| 2.4  | GIO32 Bus Signals                                        | 2-2   |

| 2.5  | GIO32 Bus Transfers                                      | 2-3   |

|      | 2.5.1 GIO32 Write Transactions                           | . 2-5 |

|      | 2.5.2 GIO32 Read Transactions                            | . 2-7 |

| 2.6  | GIO32 Bus Arbitration                                    | 2-8   |

|      | 2.6.1 Arbitration Handshake                              | . 2-9 |

|      | 2.6.2 GIO32 Bus Preemption                               | . 2-9 |

| 2.7  | GIO32 Bus Time-outs                                      | 2-11  |

| 2.8  | Issues for Slave-only GIO32 Devices                      | 2-11  |

| 2.9  | Interrupts                                               | 2-12  |

| 2.10 | ) Identifying GIO Devices                                | 2-12  |

|      | 2.10.0.1 Product Identification Word                     | 2-12  |

|      | 2.10.0.2 Product ID Code                                 | 2-13  |

| 2.11 | 1 GIO32 Option Slot Issues                               | 2-13  |

|      | 2.11.1 Address Ranges                                    | 2-13  |

|      | 2.11.2 Configuration Registers                           | 2-13  |

|      | 2.11.3 Special Registers within the Device Address Range | 2-14  |

|      | 2.11.4 Device Interface and Configuration                | 2-14  |

| 2.12 | 2 INDIGO-specific Information                            | 2-15  |

|      | 2.12.1 Indigo GIO32 Bus Arbiter                          | 2-15  |

|      | 2.12.2 Indigo Memory Timing                              | 2-16  |

| 2.13 | 3 GIO32 Option Card Requirements                         | 2-16  |

|      | 2.13.1 Mechanical Details                                | 2-16  |

|      | 2.13.2 GIO32 Electrical Details                          | 2-17  |

| 2.14 | 4 GIO32 Slot Pinout                                      | 2-18  |

# Chapter Three: GIO32-bis Specification

| 3.1 Introduction                                            | 3-1  |

|-------------------------------------------------------------|------|

| 3.2 Pin for Differentiating GIO32 from GIO32-bis            | 3-1  |

| 3.3 GIO32-bis Bus Transfers                                 | 3-1  |

| 3.3.1 GIO32-bis Bus Writes                                  | 3-1  |

| 3.3.2 GIO32-bis Bus Reads                                   | 3-3  |

| 3.3.3 GIO32-bis Preemption                                  | 3-4  |

| Chapter Four: GIO64 Specification                           |      |

| 4.1 Introduction                                            | 4-1  |

| 4.2 Conventions Used in this Chapter                        | 4-1  |

| 4.2.1 Byte Addressing                                       | 4-1  |

| 4.2.2 Waveform Conventions                                  | 4-3  |

| 4.3 GIO64 Bus Signals                                       | 4-3  |

| 4.3.1 Non-pipelined Bus Signals                             | 4-3  |

| 4.3.2 Pipelined GIO64 Bus Signals                           | 4-4  |

| 4.4 GIO64 Bus Transfers                                     | 4-6  |

| 4.4.1 Nonpipelined GIO64 Bus Transfers                      | 4-9  |

| 4.4.1.1 Non-pipelined GIO64 Bus Writes                      | 4-9  |

| 4.4.1.2 Non-pipelined GIO64 Bus Reads                       | 4-11 |

| 4.4.1.3 Non-pipelined GIO64 Preemption                      | 4-12 |

| 4.4.2 Pipelined GIO64 Transfers                             | 4-13 |

| 4.4.2.1 Pipelined GIO64 Writes                              | 4-14 |

| 4.4.2.2 Pipelined GIO64 Reads                               | 4-15 |

| 4.4.2.3 Pipelined GIO64 Preemption                          |      |

| 4.4.3 GIO64 Transfer Size                                   | 4-20 |

| 4.4.4 GIO64 Bus Time-outs                                   | 4-20 |

| 4.4.5 GIO64 Bus Tristate Turnover Cycles                    | 4-20 |

| 4.4.6 GIO64 Bus Request And Preemption                      | 4-21 |

| 4.5 GIO64 Bus Arbitration                                   | 4-22 |

| 4.5.1 Three Kinds of Bus Requests                           | 4-22 |

| 4.5.2 Arbitration Handshake                                 | 4-22 |

| 4.5.3 GIO64 Preemption                                      | 4-22 |

| 4.6 GIO Compatibility Issues                                | 4-23 |

| 4.7 Clocking                                                | 4-23 |

| 4.8 GIO64 Interrupts                                        | 4-23 |

| 4.9 Pipelined GIO64 Slot Pinout                             | 4-23 |

| 4.10 GIO64 Timing: Nonpipelined and Pipelined               | 4-24 |

| 4.11 Pipelined GIO64 Mechanicals                            | 4-28 |

| 4.12 Device Identification, Serial Number and ROM Registers | 4-28 |

| 4.13 Miscellaneous Timing Diagrams                          | 4-28 |

# **List of Figures**

| Figure 2-1  | Traditional SGI: big endian byte numbering / little endian bit numbering | 2-1  |

|-------------|--------------------------------------------------------------------------|------|

| Figure 2-2  | Little endian byte numbering / little endian bit numbering               | 2-2  |

| Figure 2-3  | A Read Cycle: Slave's Placement of Data on Bus for Data Aligned in       |      |

|             | Slave Memory differently than in Master Memory                           | 2-5  |

| Figure 2-4  | Back-to-Back Simple GIO32 Writes                                         |      |

| Figure 2-5  | GIO32 Write, Slave Stalls                                                | 2-6  |

| Figure 2-6  | GIO32 Write, Master Stalls                                               | 2-6  |

| Figure 2-7  | Simple GIO32 Reads                                                       | 2-7  |

| Figure 2-8  | GIO32 Read, Slave Delay                                                  | 2-7  |

| Figure 2-9  | GIO32 Read, Master Delay                                                 | 2-8  |

| Figure 2-10 | Preempted GIO32 Write, Slave Stall                                       | 2-10 |

| Figure 2-11 | Preempted GIO32 Write, Master Stall                                      | 2-10 |

| Figure 2-12 | Preempted GIO32 Read, Slave Stall                                        | 2-11 |

| Figure 2-13 | Preempted GIO32 Read, Master Stall                                       | 2-11 |

| Figure 2-14 | Product Identification Word                                              | 2-13 |

| Figure 2-15 | Slot Configuration Register Format                                       | 2-14 |

| Figure 2-16 | Option Slots for Indigo.                                                 | 2-16 |

| Figure 3-1  | Back-to-Back Simple GIO32-bis Writes                                     | 3-2  |

| Figure 3-2  | GIO32-bis Write, Slave Stall                                             | 3-2  |

| Figure 3-3  | GIO32-bis Write, Master Stalls                                           |      |

| Figure 3-4  | Simple GIO32-bis Read                                                    | 3-3  |

| Figure 3-5  | GIO32-bis Read, Slave Delay                                              | 3-4  |

| Figure 3-6  | GIO32-bis Read, Master Delay                                             | 3-4  |

| Figure 3-7  | Preempted GIO32-bis Write, Slave Stall                                   | 3-4  |

| Figure 3-8  | Preempted GIO32-bis Write, Master Stall                                  | 3-5  |

| Figure 3-9  | Preempted GIO32-bis Reads, Slave Stall                                   | 3-5  |

| Figure 3-10 | Preempted GIO32-bis Reads, Mater Stall                                   | 3-5  |

| Figure 4-1  | Byte Order for Big and Little Endian Transfers                           | 4-10 |

| Figure 4-2  | Back-to-Back Simple GIO64 Writes                                         | 4-10 |

| Figure 4-3  | GIO64 Write, Slave Stall                                                 | 4-10 |

| Figure 4-4  | GIO64 Write, Master Stalls                                               |      |

| Figure 4-5  | Simple GIO64 Read                                                        | 4-11 |

| Figure 4-6  | GIO64 Read, Slave Delay                                                  | 4-12 |

| Figure 4-7  | GIO64 Read, Master Delay                                                 |      |

| Figure 4-8  | Preempted GIO64 Write, Slave Stall                                       |      |

| Figure 4-9  | Preempted GIO64 Write, Master Stall                                      | 4-13 |

| Figure 4-10 | Preempted GIO64 Reads, Slave Stall                                       | 4-13 |

| Figure 4-11 | Preempted GIO64 Reads, Mater Stall                                       | 4-13 |

| Figure 4-12 | Pipelined GIO64 Writes, Memory Master                                    | 4-14 |

| Figure 4-13 | Pipelined GIO64 Writes, Pipelined Device Master                          | 4-15 |

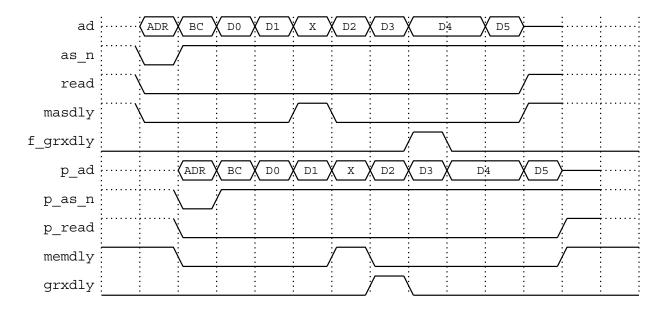

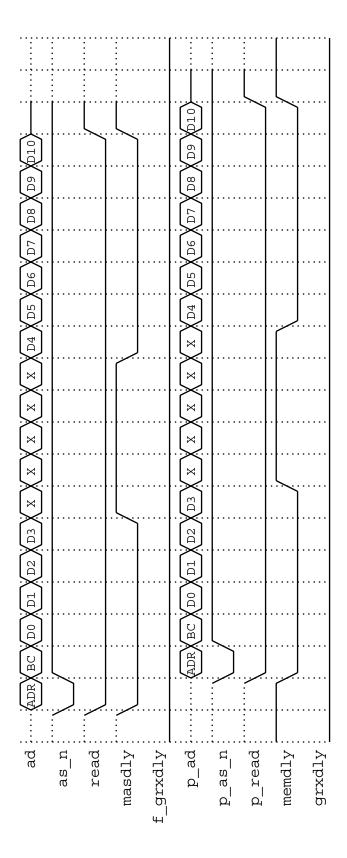

| Figure 4-14 | Pipelined GIO64 Reads, Memory Master                                     |      |

| Figure 4-15 | Pipelined GIO64 Reads, Memory Master                                     | 4-16 |

|             |                                                                          |      |

# CONFIDENTIAL

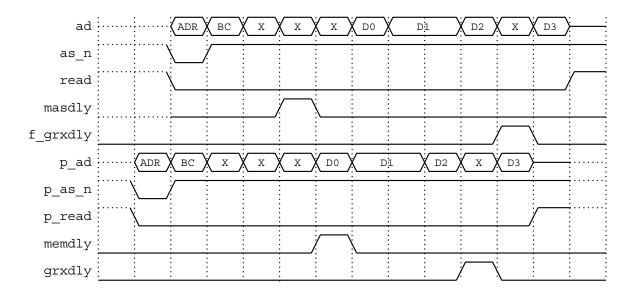

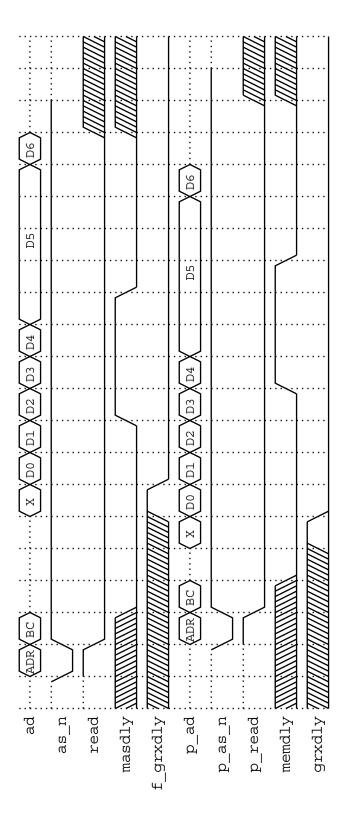

| Figure 4-16 | Pipelined GIO64 Reads, Pipelined Device Master                     | 4-17 |

|-------------|--------------------------------------------------------------------|------|

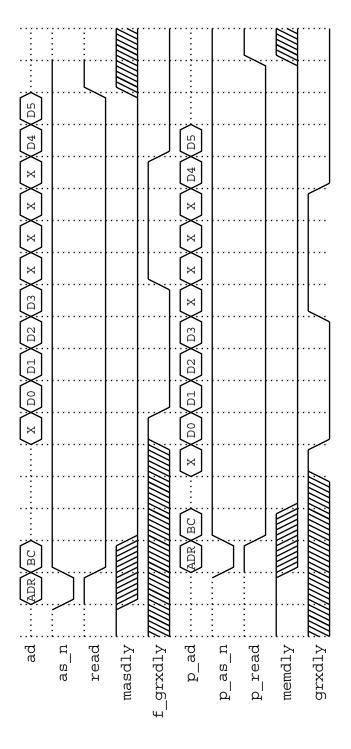

| Figure 4-17 | Preempted, Pipelined GIO64 Write, Memory Master                    | 4-18 |

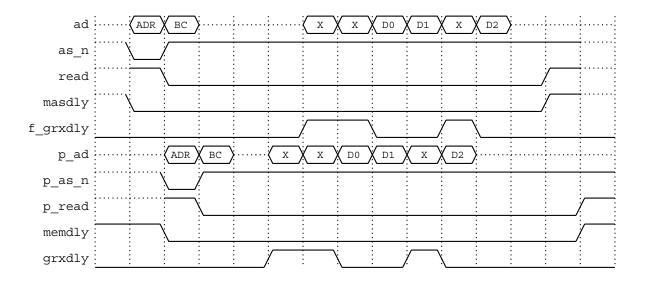

| Figure 4-18 | Preempted, Pipelined GIO64 Read, Memory Master                     |      |

| Figure 4-19 | Preempted, Pipelined GIO64 Read, Memory Master                     | 4-19 |

| Figure 4-20 | Preempted GIO64 Write, Pipelined Device Master                     |      |

| Figure 4-21 | Preempted GIO64 Read, Pipelined Device Master                      |      |

| Figure 4-22 | Preempted GIO64 32-bit Write                                       | 4-21 |

| Figure 4-23 | Preempted GIO64 32-bit Read                                        | 4-21 |

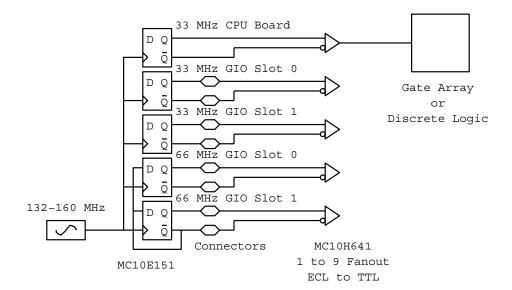

| Figure 4-24 | GIO64 Clock Distribution.                                          |      |

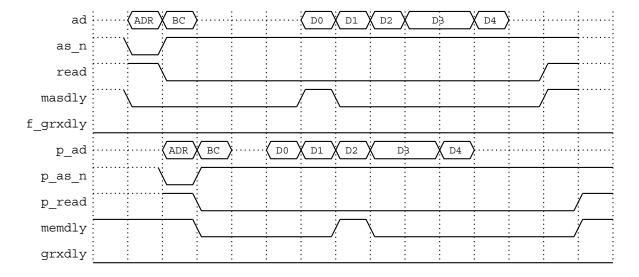

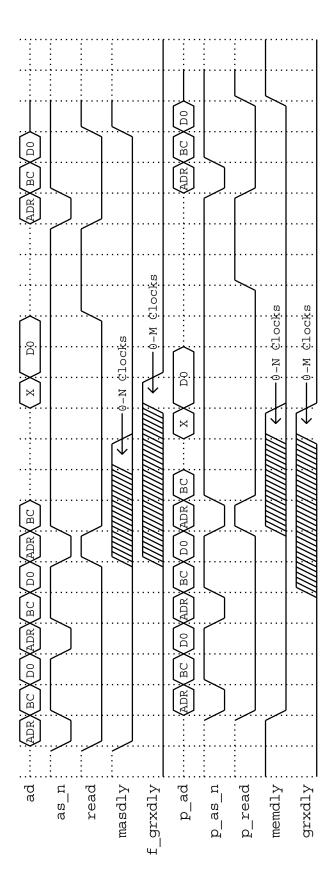

| Figure 4-25 | Two Writes, a single Read, followed by a Write for Pipelined GIO64 | 4-29 |

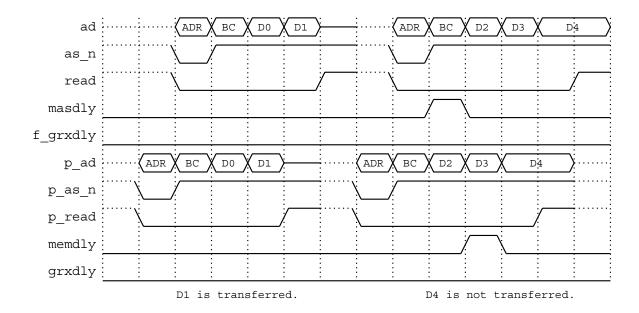

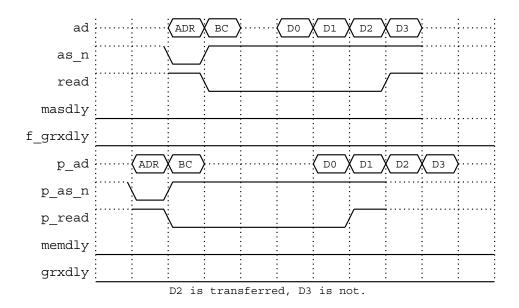

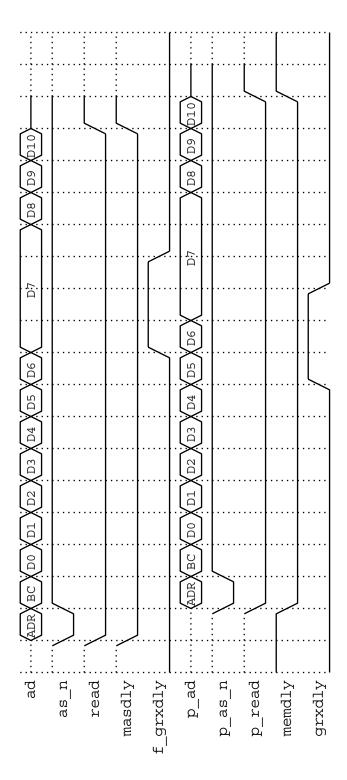

| Figure 4-26 | GRXDLY Asserted During a long Write to a Pipelined GIO64 Device    |      |

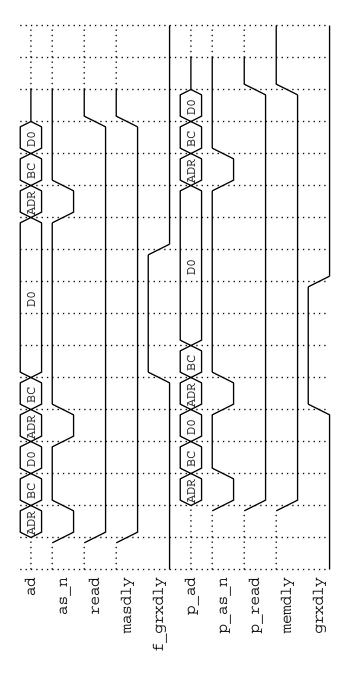

| Figure 4-27 | Single Write to a Pipelined GIO64 Device and GRXDLY                | 4-31 |

| Figure 4-28 | A Pipelined GIO64 Write and MEMDLY                                 | 4-32 |

| Figure 4-29 | Read from a Pipelined GIO64 Device and MEMDLY                      | 4-33 |

| Figure 4-30 | Read from a Pipelined GIO64 Device and GRXDLY                      | 4-34 |

List of Figures

# **GIO Bus Overview**

#### 1.1 Introduction

The GIO Bus is a family of synchronous, multiplexed address-data busses for connecting high-speed devices to main memory and CPU for entry-level SGI systems. The GIO Bus has three varieties: GIO32, GIO32-bis, and GIO64. Each variety is described in a separate chapter: GIO32 is in Chapter 2, GIO32-bis is in Chapter 3, and GIO64 is in Chapter 4.

- The GIO32 is a 32-bit, synchronous, multiplexed address-data bus that runs at speeds from 25 to 33 MHz.

- The GIO32-bis is a 32-bit version of the non-pipelined GIO64 bus.

- The GIO64 bus is a 64-bit, synchronous, multiplexed address-data bus that can run at speeds up to 40 MHz. It supports both 32- and 64-bit GIO64 devices. GIO64 has two slightly different varieties: non-pipelined for internal system memory and GIO32-bis slot devices, and pipelined for graphics and pipelined GIO64 slot devices.

The members of the GIO Bus Family are all very similar, however the GIO32 and GIO64 are not compatible. A GIO32 device does not work in a GIO64 slot. However, a GIO32-bis device can function in either a GIO32 or GIO64 option slot, as long as the appropriate connector/socket is available.

|                         | GIO32 Slot         |                    | 4 Slot           |

|-------------------------|--------------------|--------------------|------------------|

|                         | 32-pin connector   | 32-pin connector   | 64-pin connector |

| Bus Protocol supported: | GIO32<br>GIO32-bis | GIO64<br>GIO32-bis | GIO64            |

# 1.2 Conventions Used in this Document: Signal Names

Signal names that are overscored ( $\overline{EXAMPLE}$ ) denote signals that are active low signals. All other signals are active high. Signals that are one-per-device are denoted by the letter 'n' in parentheses, following the signal name: SIGNAL(n).

This page has been left blank intentionally.

# **GIO32 Specification**

## 2.1 Introduction

The GIO32 bus is a 32-bit, synchronous, multiplexed address-data bus that runs at speeds from 25 to 33 MHz. The bus connects high speed devices to memory and to the CPU.

The GIO32 bus supports two types of devices: 1.the CPU and other long-burst devices that do long-burst transfers between themselves and system memory, and 2. real-time I/O devices that require guaranteed maximum bus latency.

A bus arbiter, implemented by the Processor Interface Controller (PIC) in the Indigo system, arbitrates between competing bus masters in the system. The PIC also acts as master in transactions between the Indigo CPU and other GIO32 devices.

Maximum performance of the 33 MHz GIO32 bus is as follows:

long-burst read/write 132 MBytes/second back-to-back 32-bit word writes 44 MBytes/second back-to-back 32-bit word reads from memory 16 MBytes/second back-to-back 32-bit word reads (theoretical) 26 MBytes/second

# 2.2 Conventions Used in this Chapter

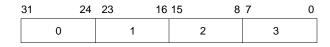

The GIO32 bus uses a 32-bit byte address. The byte numbering scheme is big endian; the bit numbering scheme is little endian. (See Figure 2-1.) Thus, byte 0 is bits <31:24>, byte 1 is bits <23:16>, byte 2 is bits <15:8>, and byte 3 is bits <7:0>.

The following figure shows the byte and bit numbering schemes.

Figure 2-1. Traditional SGI: big endian byte numbering / little endian bit numbering

[Due to the Indigo's ability to run either as a traditionally big-endian system or as a little-endian system, the GIO32 bus supports both little- and big-endian byte numbering schemes. The endian selection is made at power-up time based on the endianness of the software found on the hard disk. GIO32 option cards need to be capable of running in big- and little-endian mode. How they detect the endianness of the system at power-up time is TBD.]

<sup>1.</sup> Due to the specific implementation on the Indigo, back-to-back 32-bit word reads from the Indigo CPU are about 8.8 MBytes/second.

| 31 | 24 | 23 | 16 | 15 | 8 | 7 | 0 |

|----|----|----|----|----|---|---|---|

| 3  |    |    | 2  | 1  |   | 0 |   |

Figure 2-2. Little endian byte numbering / little endian bit numbering

# 2.3 GIO32 Transfer Size and Preemption

GIO32 bus transfers can be one byte to 4K bytes long. A byte count field specifies the length of a transaction. The transfer cannot cross a 4K processor virtual page boundary; i.e., the data must originate from or be destined for a single page of main memory. A bus request by a real-time I/O device preempts an ongoing long-burst transaction. The interrupted transaction can be resumed as a new transaction when the bus is free.

# 2.4 GIO32 Bus Signals

The GIO32 bus has 32 address/data signals; control lines that include address strobe, read/write select, master delay, and slave delay; arbitration signals that include bus request, bus grant, and bus preempt; and CPU interrupt and reset signals. The table below lists the GIO32 signals.

| TABLE 1 | GIO Bus Signals. |

|---------|------------------|

|---------|------------------|

| SIGNAL    | Description               |  |

|-----------|---------------------------|--|

| AD<31:0>  | 32 address/data signals   |  |

| ĀS        | address strobe            |  |

| READ      | read/write select         |  |

| MASDLY    | master delay              |  |

| SLVDLY    | slave delay               |  |

| BREQ(n)   | bus request, 1 per master |  |

| BGNT(n)   | bus grant, 1 per master   |  |

| BPRE      | bus preempt               |  |

| ĪNT<2:0>  | interrupts                |  |

| CLK clock |                           |  |

| RESET     | reset                     |  |

AD<31:0>: The address/data signals are the multiplexed address and data lines. During a slave address cycle, they contain the slave address for the bus transaction. The next cycle in a transaction, the byte count cycle, uses AD<12:0> to indicate the number of bytes to transfer and AD<31:30> to indicate the master starting byte address. The master starting byte address defines the byte where the data starts (byte 0, 1, 2, or 3) when placed on or taken off the bus. Master devices use this field to define the bus alignment that slave devices must follow (i.e., obey). There is one major exception: option slot devices exchanging data with CPU or memory. Master option slot devices cannot use the master starting byte field to modify the alignment of data on the bus when interacting with CPU or memory, because CPU and memory require all bus

SGI CONFIDENTIAL GIO32 Bus Transfers

data to be aligned to the workstation's main memory. Below is a summary for option slot device usage of the master starting byte address:

- as slave, the master's starting byte address (AD<31:30>) must be obeyed since all data must be aligned with main memory or CPU, and

- as master, anything can be written to AD<31:30>, however it will not be interpreted by the CPU or memory. All data on the bus will be and must be aligned to main memory or CPU.

AS: Address strobe signals the start of a new bus transaction. The device that is currently the bus master asserts address strobe and places a slave address on the bus. All other devices on the bus should latch the address to determine if they are the device being addressed. Address strobe is only asserted for one cycle. The byte count cycle follows the address cycle.

READ: The READ signal serves two purposes. During the slave address cycle the master asserts READ for a read (master receives data) or deasserts READ for a write (master supplies data) transaction. After the slave address cycle, the bus master drives READ low to indicate that a bus transaction is taking place. The master holds READ low until the bus transaction ends naturally or through preemption.

MASDLY: The master asserts the master delay signal to throttle the data transfer rate. The signal has different meanings for read and write transactions. For a read transaction, the master asserts MASDLY when it is not ready to receive data in the current bus cycle. For a write, MASDLY indicates that the data currently on the bus is invalid. MASDLY is ignored during address and byte count cycles.

SLVDLY: The slave device asserts SLVDLY to throttle the data transfer rate. Like MASDLY, this signal has different meanings for read and write transactions. When the slave asserts SLVDLY during a bus read, the data on the bus is invalid. During a bus write, SLVDLY indicates that the slave cannot accept data in the current bus cycle. SLVDLY is pulled high on the CPU board so that it is asserted during the byte count cycle. The slave must drive SLVDLY high at the end of a bus transaction before tristating it because the pullup on the CPU board is not strong enough to pull SLVDLY high in one cycle.

$\overline{BREQ}(n)$ : Every bus master in the system has its own bus request signal. To request the bus, a device asserts its bus request signal. The device must hold its  $\overline{BREQ}(n)$  signal asserted until the bus arbiter grants it the bus, even if the device decides it does not need the bus. The bus master holds  $\overline{BREQ}(n)$  asserted until the end of the bus transaction. When the bus arbiter preempts the bus, the master device must deassert its bus request signal to indicate that it is off the bus. A preempted device cannot reassert its bus request signal until the bus arbiter deasserts the preemption signal. In order to avoid bus time-outs, a bus master must still accept requests from other bus masters even if it is requesting the bus.

$\overline{BGNT}(n)$ : Every bus master in the system has its own bus grant signal, which indicates to a master device that it owns the bus. The bus arbiter asserts a device's matching bus grant signal for as long as the bus master asserts its bus request signal. When the bus arbiter preempts a master device, the arbiter does not deassert the bus grant signal until the bus master deasserts its  $\overline{BREQ}(n)$  signal.

$\overline{BPRE}$ : The GIO arbiter asserts the bus preempt signal to preempt the current bus transaction. The bus master must respond to  $\overline{BPRE}$  within {missing information: number of clock cycles is somewhere between four and nine} GIO32 clock cycles by deasserting its  $\overline{BREQ}(n)$  signal and asserting READ. Real-time devices are not preemptable and can ignore  $\overline{BPRE}$ .

$\overline{\text{INT}}$ <2:0>: The GIO32 bus has three interrupt/status signals,  $\overline{\text{INT}}$ <2:0>, which are shared by all devices: the two GIO32 bus option slots and the graphics board(s).  $\overline{\text{INT}}$ <0> and  $\overline{\text{INT}}$ <1> are low priority interrupts.  $\overline{\text{INT}}$ <2> is a high priority interrupt. These signals can generate CPU interrupts and be read by the CPU.

CLK: The GIO32 clock runs at 25, 30, or 33 MHz. Data is valid at the rising edge of CLK.

RESET: An asynchronous signal for resetting/restarting all devices on the bus.

# 2.5 GIO32 Bus Transfers

The GIO32 bus supports three kinds of cycles during a bus transaction. The first cycle of every transaction is a slave address cycle. The second cycle is the byte count cycle. Subsequent cycles are one or more data cycles. After the final data cycle of a transaction, AD < 31:0>, READ,  $\overline{AS}$ , MASDLY, and SLVDLY must be tristated.

In the slave address cycle, the bus master sends the slave address out on AD<31:0> and asserts  $\overline{AS}$ . For a read transaction, the master asserts READ; for a write the master deasserts READ.

In the byte count cycle that follows, the master sends the transfer byte count on AD<12:0>. In this second cycle, the meaning of the READ signal changes to mean that a bus transaction is taking place on the bus. To this end, the master deasserts READ and holds it deasserted until the end of the bus transaction. The address strobe signal is not active in this cycle. The master also writes the address (offset) for the master starting address onto AD<31:30> during this cycle. All slave devices must obey these bits to place data onto or take data off of the bus so that the data on the bus is always aligned for the master device. Devices talking to the CPU or memory (regardless of whether they are slave or master) must always use the alignment described in Figure 2-1 or Figure 2-2 of this specification so that the data is properly aligned for main memory. Note that option slot master devices cannot use the "master starting byte address" feature with CPU and memory since the CPU and memory only support their own alignment.

#### IMPLEMENTATION RESTRICTION:

Due to implementation details of the bus arbiter, the maximum byte count for a master is 1023 for any single transaction.

The byte count and 32-bit slave address determine alignment (in slave memory) of the slave start and end addresses. The master starting byte and the byte count determine the alignment in master memory. The master starting byte field consists of the two least significant bits of the master's byte address. For transfers where the slave and master addresses are aligned, the least significant bits (AD<31:30>) match on the first and second cycle: the slave address sent in the first cycle of the transaction and the master starting byte of the second. If the transfer is unaligned, the bits do not match. A slave GIO device must deal with the data (either place data on the bus during a read or rearrange data taken from the bus on a write) in the master's alignment (according to these bits). Note that CPU and memory, as slave devices, do not support this feature; they do not rearrange data. CPU and memory always place data on the bus as it is aligned in memory and they assume that data taken from the bus is already aligned to main memory.

#### CAUTION:

Master option slot devices must not expect CPU or memory to obey the settings of AD<31:30> during the byte count cycle (i.e., the master starting byte address). CPU and memory only deal with data that is aligned to main memory.

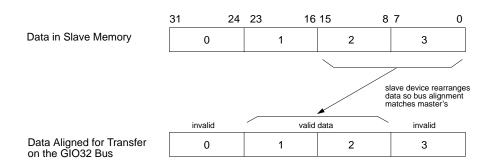

For example, for a read, if the slave address is 0x2, the byte count is 0x2, and the master starting byte address is 0x1, the slave would read its own memory from byte addresses 0x2-0x3 and drive that data on the bus with the byte from slave address 0x2 placed at address 0x1 (i.e., onto AD<23:16>), packing the other byte in the same word. Figure 2-3 illustrates this case.

2-4 6 May 1992 GIO32 Specification

SGI CONFIDENTIAL GIO32 Bus Transfers

Figure 2-3. A Read Cycle: Slave's Placement of Data on Bus for Data Aligned in Slave Memory differently than in Master Memory.

Following the slave address and byte count cycles are a variable number of data cycles. The number depends on the byte count, bus preemption, and the flow control signals MASDLY and SLVDLY. The master drives MASDLY and the slave drives SLVDLY. These signals throttle the data transfer rate.

#### 2.5.1 GIO32 Write Transactions

GIO32 bus write transactions take a minimum of three bus clock cycles. The transaction begins with the slave address and byte count cycles. In the slave address cycle, the master does the following:

- asserts  $\overline{AS}$

- drives a 32-bit slave address on AD<31:0>

- deasserts READ to indicate that this is a write cycle.

In the byte count cycle, the master does the following:

- deasserts READ and holds it low until the end of the transaction

- drives a byte count on AD<12:0>

- drives the master starting byte address on AD<31:30>.

After the byte count cycle, the master can begin data transfer. During a write, the bus master drives data out onto the AD signals and deasserts MASDLY to indicate that valid data is on the bus. The master looks at SLVDLY at the end of the clock cycle to determine whether the slave is ready to accept the data. If the slave deasserts SLVDLY by the end of the cycle, the master knows that the slave will pick up the data at the rising clock edge, and that the master can put a new data word on the bus in the next cycle. Otherwise, if the slave does not deassert SLVDLY by the end of the cycle, the master must continue to drive the current word of data for additional bus clock cycles until it sees SLVDLY go low. The bus master can transfer a word of new data during every bus cycle that the slave is deasserting SLVDLY. The master can throttle the transfer rate by asserting MASDLY during a cycle when it is not ready to send a new word of data on the bus.

The bus master continues to transfer data until the byte count is satisfied or until the bus arbiter asserts the BPRE signal. The bus slave also keeps track of the number of bytes that have been transferred so that it can handle the last data word correctly if it is a partial word transfer.

At the end of the transaction, the master asserts MASDLY. The slave asserts SLVDLY within one cycle after the last data word and then tristates the signal. The bus master, if it does not wish to start another transaction, asserts READ, then tristates  $\overline{AS}$ , AD<31:0>, READ, and MASDLY. If the master has another transaction to do, it immediately begins the transaction by executing a slave address cycle.

If the bus arbiter preempts a bus transaction, the byte count will not be zero when the bus master asserts READ in response to the preemption. The slave needs to monitor READ so that it can detect a preemption and assert SLVDLY within one cycle. The bus master must keep all of the information -- remaining byte count and updated slave address -- necessary to restart the transaction where it was interrupted.

GIO32 Bus Transfers

Figure 2-4, Figure 2-5, and Figure 2-6 illustrate sample GIO32 write transactions:

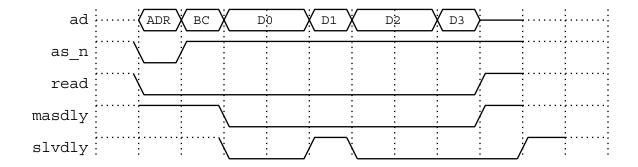

Figure 2-4. Back-to-Back Simple GIO32 Writes

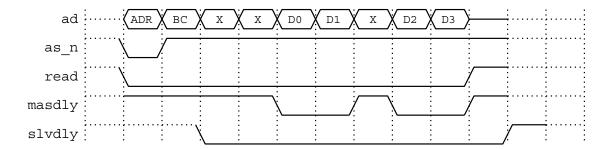

Figure 2-5. GIO32 Write, Slave Stalls

Figure 2-6. GIO32 Write, Master Stalls

SGI CONFIDENTIAL GIO32 Bus Transfers

#### 2.5.2 GIO32 Read Transactions

GIO32 bus read transactions are very similar to write transactions except that the bus slave, not the bus master, drives the data on the bus.

The GIO32 bus requires one dead cycle on the bus when the device driving the bus changes. Thus a read transaction has a dead cycle between the master driving the byte count cycle and the slave driving the first data cycle, as well as between the final data cycle of a transaction and a subsequent address strobe that starts a new transaction. This requirement makes the minimum length of back-to-back read transactions four bus cycles.

The READ signal, asserted by the bus master during the slave address cycle to indicate a read transaction, is held deasserted from the byte count cycle onward to indicate that a bus transaction is taking place. During data cycles, the slave deasserts SLVDLY when it is driving valid data on the AD signals. The master deasserts MASDLY during cycles when is ready to take data off the bus.

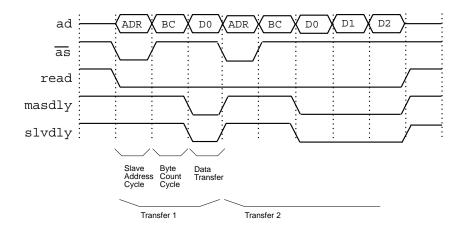

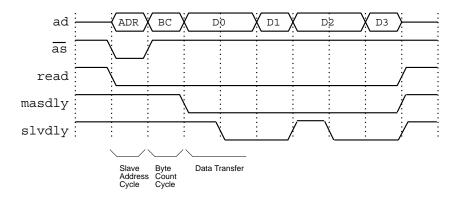

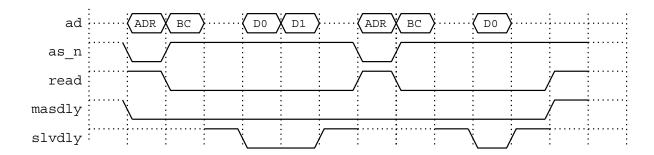

Examples of GIO32 bus read transactions are shown in Figure 2-7, Figure 2-8, and Figure 2-9.

Figure 2-7. Simple GIO32 Reads

Figure 2-8. GIO32 Read, Slave Delay

GIO32 Bus Arbitration SGI CONFIDENTIAL

Figure 2-9. GIO32 Read, Master Delay

# 2.6 GIO32 Bus Arbitration

The GIO32 bus arbitration scheme supports three requirements:

- The CPU must run at a minimum, guaranteed rate in the most highly loaded system to allow for acceptable interrupt response times.

- Long-burst DMAs for devices such as the graphics subsystem must be allowed to use the bus for long stretches of time to move large amounts of data.

- Real-time I/O devices such as network connections (e.g., Ethernet, FDDI) and audio must be guaranteed access to the bus within a predefined maximum delay.

These three requirements -- to support the CPU, long burst, and real-time I/O devices -- result in the following rules of bus behavior.

- Long-burst devices have low priority as well as limits on the time they can be master of the bus. A long-burst

device can perform multiple transactions once it becomes bus master. The bus arbiter preempts a long-burst

device master to service a real-time I/O device or because the long-burst device has used up its time slot on the

bus.

- The CPU is a long-burst device, but differs in two ways from all other long-burst devices. First, the bus arbiter will only preempt CPU bus mastership between bus transactions. Second, the CPU becomes bus master after every grant to some other long-burst bus master.

- Real-time I/O devices have high priority. They can use the bus for no more than a fixed unit of time -- 5 microseconds -- per acquisition and can only request the bus at a predefined frequency.

The GIO32 bus arbiter has two time slot registers--DELAY and BURST--that limit the time a bus master can hold the bus. The DELAY register limits the CPU's time on the bus. The BURST register limits the time on the bus for all other long-burst devices. The operating system chooses the time values to load into these registers when a device becomes bus master. For example, the CPU time limit might be set to 2 microseconds, while the time limit for all other long-burst devices might be 38 microseconds. If a bus master is still asserting its  $\overline{BREQ}(n)$  signal when its time limit expires, the bus arbiter preempts the bus. If the CPU receives and services an interrupt during a bus transaction, the CPU resets the time value in the BURST register to zero and the DELAY register to its maximum value so that the CPU can immediately become bus master.

Real-time I/O devices preempt long-burst devices immediately. The Indigo Peripheral Controller chip (HPC), which manages Ethernet and SCSI access, is the highest priority real-time I/O device in the system, followed by option slot 0 and then option slot 1. A preempted long-burst device regains the GIO Bus after the preempting transaction completes. When no other device requests the bus, the CPU becomes bus master.

2-8 6 May 1992 GIO32 Specification

SGI CONFIDENTIAL GIO32 Bus Arbitration

#### IMPLEMENTATION RESTRICTION:

Due to implementation details of the bus arbiter, non-CPU, long burst masters must not simply drive  $\overline{BREQ}(n)$  inactive when they wish to relinquish the bus. They must wait for  $\overline{BPRE}$  to be asserted and then deassert  $\overline{BREQ}(n)$ .

#### 2.6.1 Arbitration Handshake

#### Connecting:

Each bus master on the GIO32 bus connects to the bus arbiter with a pair of  $\overline{BREQ}(n)$  and  $\overline{BGNT}(n)$  signals. A device requests the bus by asserting its  $\overline{BREQ}(n)$  signal. The arbiter grants the bus to the requesting device by asserting the matching  $\overline{BGNT}(n)$  signal. Once a device asserts its  $\overline{BREQ}(n)$  signal, it must hold the signal asserted until the arbiter has granted the bus.

#### IMPLEMENTATION RESTRICTION:

Due to implementation details of the bus arbiter, it is possible that the arbiter may assert  $\overline{BGNT}(n)$  for one cycle and then deassert it, without actually granting the bus. Therefore, bus masters must not conclude that they have been granted the bus until  $\overline{BGNT}(n)$  has been asserted for two consecutive cycles. Once asserted,  $\overline{BREQ}(n)$  must not be deasserted until the bus has been granted.

#### Doing the transaction:

A bus master must keep its  $\overline{BREQ}(n)$  signal asserted until the bus transaction is complete.

#### Terminating

When the bus transaction is complete, the bus master deasserts its  $\overline{BREQ}(n)$  signal and the arbiter then deasserts the  $\overline{BGNT}(n)$ .

### 2.6.2 GIO32 Bus Preemption

The GIO32 bus arbiter preempts a long-burst bus master when a real-time I/O device needs the bus or when the bus master uses up its time slot on the bus. The arbiter asserts  $\overline{BPRE}$ . In response, the current bus master asserts READ within {missing information: four to nine} bus cycles to indicate end of transaction. If a write transaction was underway, the master stops driving AD and MASDLY in the same cycle as the deassertion of READ. In the case of a preempted read transaction, the slave may continue driving data as the master is deasserting READ; however, the data driven will not be accepted by the bus master. The bus master must keep track of the slave address and remaining byte count in order to resume the transfer later.

A bus master can preempt its own bus transaction before the byte count has been satisfied and never resume the transaction. This type of preemption is useful for devices that may not know the byte count at the start of the transaction. The master can drive a maximum byte count during the byte count cycle and then preempt the transaction by asserting the

GIO32 Specification 6 May 1992 2-9

<sup>2.</sup> Note the implementation restriction (on page 2-9) associated with deasserting BREQ(n).

GIO32 Bus Arbitration SGI CONFIDENTIAL

READ signal when it has received the desired bytes. Note that this technique requires the last transfer to be aligned to the bus because the byte count cannot indicate how many bytes to transfer on the last cycle.

#### IMPLEMENTATION RESTRICTION:

Due to implementation details of the bus arbiter, the selfpreemption with unfinished transaction feature will not work and must not be used. Bus masters *must* provide an accurate and exact byte count.

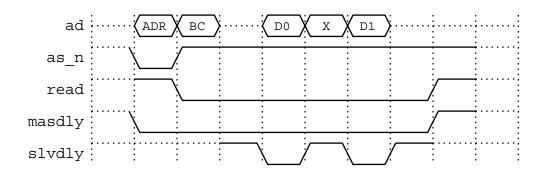

Preemption examples are presented in Figure 2-10 to Figure 2-13.

Figure 2-10. Preempted GIO32 Write, Slave Stall

Figure 2-11. Preempted GIO32 Write, Master Stall

2-10 6 May 1992 GIO32 Specification

SGI CONFIDENTIAL GIO32 Bus Time-outs

Figure 2-12. Preempted GIO32 Read, Slave Stall

Figure 2-13. Preempted GIO32 Read, Master Stall

#### 2.7 GIO32 Bus Time-outs

A GIO32 bus transaction times out if a slave does not deassert SLVDLY in reply to an address strobe within 25 microseconds after the byte count cycle. This time-out prevents accesses to non-existent locations on the GIO32 bus from hanging the bus. When a time-out occurs, the bus arbiter deasserts SLVDLY until the transaction completes. Then the arbiter generates a bus error interrupt to the CPU. The device that was transferring data does not know that a time-out occurred. Software can use this time-out mechanism to determine whether a device exists in a GIO32 slot. The guaranteed bus acquisition time of five microseconds for real time devices may be violated when the GIO32 bus times out.

# 2.8 Issues for Slave-only GIO32 Devices

GIO32 devices that will not perform as master devices, can simplify their design in the following manner:

- preemption will never occur and so is not an issue,

- all transfers will include only one data cycle,

- AD<12:0> (the byte count) in the byte count cycle can be ignored, and

- three signals are not used: BREQ, BGNT, and BPRE.

Interrupts SGI CONFIDENTIAL

# 2.9 Interrupts

Each interrupt from a GIO device will cause every device driver associated with the interrupt line to be called. For example, if two device drivers are associated with  $\overline{\text{INT0}}$ , whenever an interrupt occurs on this line each driver is called in turn, thus giving each the opportunity to process any interrupt generated by it's device (at that level). Since interrupt levels may be shared, each device (or the protocol between the device and the host) must provide a reliable mechanism for allowing a device driver to determine whether a given interrupt call was caused by the associated device or not. All device drivers must, at all times, be able to gracefully handle spurious interrupts.<sup>3</sup>

CAUTION:

GIO Interrupts 2 and 0 ( $\overline{\text{INT}}$ 2 and  $\overline{\text{INT}}$ 0) are reserved for use by graphics boards only. Option slot devices must use  $\overline{\text{INT}}$ 1.

**Note:** Each device must provide a register

# 2.10 Identifying GIO Devices

#### 2.10.1 Product Identification Word

During the configuration procedure, the CPU does a slave (host) word read of the Product Identification Word associated with each potential GIO device. The read must be done as a word read. (This ensures endian independence.) These reads establish the presence and identity of all the GIO devices that are present. (GIO devices do not use the "address probe" scheme used in VME-based devices.) For slot devices, the Product Identification Word is read by accessing the first (base) address within the slot's address range. During the slave cycle following any read of the slot's base address, the Product Identification Word information is driven onto AD<31:0>.

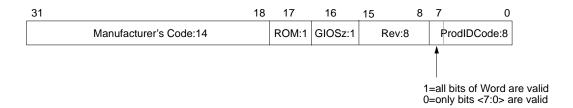

The Product Identification Word contains five pieces of information as listed below and illustrated in Figure 2-14.

| - | Bits :0 :     | Product ID Code     | unique ID assigned by SGI (see section "Product ID Code" for more detail)                                                                                                                                                                                                                        |

|---|---------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - | Bits <15:8>:  | Product Revision    | product revision value assigned by the manufacturer                                                                                                                                                                                                                                              |

| - | Bit <16>:     | GIO Interface size  | 0=32bits, 1=64bits For GIO32 and GIO32-bis, must be zero. For GIO64, may be 0 or 1.                                                                                                                                                                                                              |

| - | Bit <17>:     | ROM Present         | 0=no ROM, 1=ROM present When set to one, indicates that the next three words of the device's address space are dedicated to special registers, as explained in the section "Special Registers". When set to zero, the device's address space contains no reserved areas except the base address. |

| - | Bits <31:18>: | Manufacturer's Code | value and purpose assigned by the manufacturer.                                                                                                                                                                                                                                                  |

2-12 6 May 1992 GIO32 Specification

<sup>3.</sup> How to handle the linking of a device driver into one or more interrupt chains is TBD. One technique is a table of routine addresses with an entry per slot per level. All entries would be initialized to a stub routine address before calling the boot-time autoconfig which would overwrite any used entry with the actual driver entry point(s). In this way, the interrupt dispatch code would not need any conditional tests.

SGI CONFIDENTIAL GIO32 Option Slot Issues

Figure 2-14. Product Identification Word

#### 2.10.2 Product ID Code

The lowest byte of the Product Identification Word contains a unique, 8-bit Product ID Code that is hardwired into each GIO device. During the slave cycle following any read of the slot's base address, this 8-bit Product ID Code is driven onto the lower bits (bits 7:0) of AD (at the same time as all the other Product Identification Word).

Product ID Codes are unique across all GIO devices and must be registered with Silicon Graphics.<sup>4</sup>

When the assigned Product ID Code has bit 7 equal to zero, the device does not provide meaningful (neither correct nor repeatable) data on AD<31:8> during the slave cycle following a read of a slot's base address. Such boards must be recognized based on AD<7:0> and the other fields must be treated by software as if they contained the following values:

- Bits <7:0>: Product ID Code unique ID assigned by SGI where bit 7=0

- Bits <15:8>: Product Revision

Bit <16>: GIO Interface size 0 (i.e., =32bits)

Bit <17>: ROM present 0 (i.e., =no ROM)

- Bits <31:18>: Board Manufacturer not defined (i.e., manufacturer must be deduced from Product/

Board Identification code).

# 2.11 GIO32 Option Slot Issues

## 2.11.1 Address Ranges

Each option slot has a 2 MByte address range:

- slot 0 = 0x1f400000 to 0x1f5fffff,

- slot 1 = 0x1f600000 to 0x1f7fffff.

Note: addresses 0x1f800000 to 0x1f9fffff are reserved for future definition by Silicon Graphics.

# 2.11.2 Configuration Registers

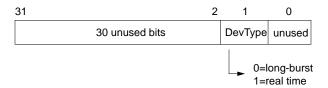

GIO32 option cards configure themselves by writing into their Configuration Register. Each slot has its own register in the format shown in Figure 2-15. Slot 0's is located at 0x1FA20000. Slot 1's is at 0x1FA20004.

**GIO32 Specification** 6 May 1992 **2-13**

<sup>4.</sup> The procedure and contact point for doing this are TBD. The numbers will be recorded in an appropriate header file in the kernel source tree.

GIO32 Option Slot Issues SGI CONFIDENTIAL

The setting of bit 1 communicates the device type:1 indicates real-time I/O and 0 indicates long-burst. Bits <31:2> and bit 0 are not used.

Figure 2-15. Slot Configuration Register Format

# 2.11.3 Special Registers within the Device Address Range

When an option slot device has ROM, it indicates the ROM's presence to the CPU by setting to one the ROM Present bit in the Product Identification Word. Whenever this bit is set, the three words following the base address of the device address range are reserved as three special 32-bit registers, as explained below.

- The word at base address + 0x4 is the optional Board Serial Number register. This serial number is assigned by the manufacturer.

- 2. The word at base address + 0x8 is the ROM Index register. This register is written to zero by the CPU to initiate reading of the ROM. Subsequent reads of the ROM Read register cause this register to automatically increment by 4, indicating the currently available word in the ROM Read register.

- 3. The word at base address + 0xc is the ROM Read register. This register contains the contents of one word from the ROM. It always contains the word from the address indicated in the ROM Index register.

# 2.11.4 Device Interface and Configuration

GIO32 option slot device drivers configure themselves by calling setgiovector, setgioconfig, and the apporpriate splgio#. These calls and their parameters are listed below:

```

setgiovector(INT_LEVEL, GIO_SLOT, GIO_FUNC, GIO_ARG);

setgioconfig(GIO_SLOT, GIO_ARB);

splgio0();

splgio1();

splgio2();

```

setgiovector(INT LEVEL, GIO SLOT, GIO FUNC, GIO ARG)

A device driver registers its interrupt service function with the kernel's interrupt dispatcher by calling setgiovecotor. The call requires four parameters explained below.

- 1. The *level* parameter is an integer specifying which one of the three possible GIO bus interrupts is used by the device. This parameter must be one of the following:

- 0 = GIO\_INTERRUPT\_0 ,

1 = GIO\_INTERRUPT\_1 , or

2 = GIO\_INTERRUPT\_2 .

#### CAUTION:

Due to limitations in the graphics subsystem, GIO Interrupts 2 and 0 ( $\overline{INT2}$  and  $\overline{INT0}$ ) are reserved for use by graphics boards only. Option slot devices must use  $\overline{INT1}$ .

2-14 6 May 1992 GIO32 Specification

- 2. The *slot* parameter is an integer and specifies the physical slot occupied by the GIO bus board. This parameter must be one of the following:

- $0 = GIO_SLOT_0$ ,

- $1 = GIO_SLOT_1$ , or

- 2 = GIO SLOT GFX.

- 3. The *function* parameter is a pointer to the interrupt service routine that will be called when the associated interrupt occurs.

Note that because interrupts are shared among devices, func [i.e., void (\*func) (int);] may be called when there is no pending interrupt from the particular slot specified, in which case func should simply return. The interrupt handler therefore needs to be able to determine when its device is actually interrupting, and when it is not, in a non-destructive manner.

4. The *argument* parameter is an integer that is passed to the interrupt service routine whenever the interrupt routine is called; *arg* may contain any value. The interrupt service routine will be called with the processor interrupt mask set to disable further interrupts from the device.

```

setgioconfig(GIO SLOT, GIO ARB)

```

Device drivers call setgioconfig to set up the GIO bus arbitration mode for the GIO slot specified by the *slot* parameter. The call requires two parameters explained below.

- 1. The *slot* parameter is an integer and specifies the physical slot occupied by the GIO bus board. This parameter must be one of the following:

- 0 =GIO\_SLOT\_0,

- $1 = GIO_SLOT_1$ , or

- 2 = GIO SLOT GFX.

- 2. The *arbitration* mode is specified as a bit-wise OR of the following two flags:

- GIO\_CONFIG\_LONG

- where 0=real-time device and 1=long-burst device,

- GIO\_CONFIG\_SLAVE where 0=device is both master and slave, and 1=device is slave only.

```

splgio0(), splgio1(), or splgio2()

```

The splgio0(), splgio1(), and splgio2() functions set the processor interrupt mask to block GIO bus interrupts. splgio0 sets the mask for  $\overline{INT}0$ , splgio1 sets the mask for  $\overline{INT}1$ , etc..

# 2.12 INDIGO-specific Information

#### 2.12.1 Indigo GIO32 Bus Arbiter

The Processor Interface Controller chip (PIC) is the GIO32 arbiter in the Indigo system. The PIC acts as master device for transactions between the CPU and GIO32 devices. These transactions are one to four bytes in length. PIC timing and synchronization with the CPU, which runs at a different speed than the GIO32 bus, requires about fifteen bus clock cycles to complete a single-word GIO32 bus read transaction.

# 2.12.2 Indigo Memory Timing

When a GIO32 bus device initiates a long-burst read transfer from main memory, the Indigo memory subsystem requires seven cycles for RAS and CAS before it drives the first data word on the GIO32 bus. Subsequent data words are driven at the full bus speed of one 32-bit word per bus cycle unless throttled by the bus master device or by the memory controller.

# 2.13 GIO32 Option Card Requirements

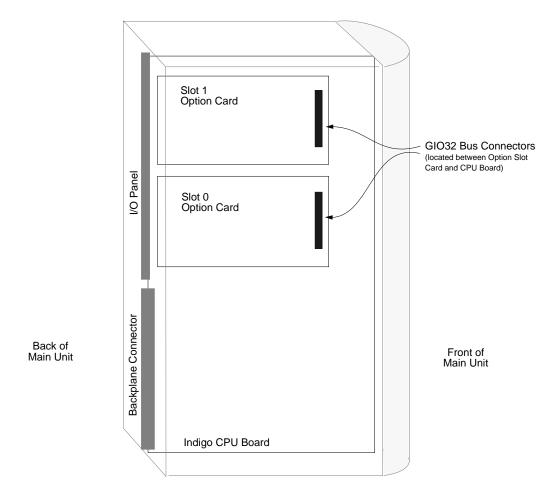

#### 2.13.1 Mechanical Details

The Indigo CPU board has two 96-pin, high density, GIO32 bus connectors on its top side. The connector is a Fujitsu 230-series straight header with post. An option card plugs into a GIO32 bus connector, pops onto stabilizing card standoffs on the CPU board, and presents its I/O connections (if any) out an I/O panel on the back of the Indigo system box. Each option card has its own I/O connector area, which is 2.84 inches long and 0.80 inches wide.

Option cards are 6.44 inches long by 3.375 inches wide. Components may be placed on both sides of the card, with a top side component height limit of 0.65 inches and a bottom side limit of 0.10 inches.

Figure 2-16 shows two option cards mounted on the Indigo CPU board:

Figure 2-16. Option Slots for Indigo.

# 2.13.2 GIO32 Electrical Details

A GIO32 option card must meet the following electrical specifications:

- 13.6 watts maximum power consumption

- +5 volts @ 2 amps

- +12 volts @ 0.15 amps

- -12 volts @ 0.15 amps

- TTL-compatible signals with CMOS compatible input currents

- 50 pF AC loading for clock and reset signals

- 15 pF AC loading for all other bus signals

- 74FCT652AT or similar bus transceivers for AD<31:0>

- FCC Class B with 6 dB margin

GIO32 Slot Pinout SGI CONFIDENTIAL

# 2.14 GIO32 Slot Pinout

# TABLE 2 GIO32 Pinout.

| SIGNAL       | PIN# | SLAVE | MASTER |

|--------------|------|-------|--------|

| RESERVED N/C | 01   | -     | -      |

| RESERVED N/C | 02   | -     | -      |

| RESERVED N/C | 03   | -     | -      |

| RESERVED N/C | 04   | -     | -      |

| GND          | 05   | -     | -      |

| RESERVED N/C | 06   | -     | -      |

| RESERVED N/C | 07   | -     | -      |

| RESERVED N/C | 08   | -     | -      |

| RESERVED N/C | 09   | -     | -      |

| GND          | 10   | -     | -      |

| RESERVED N/C | 11   | -     | -      |

| GIO.RESET    | 12   | I     | I      |

| +12V         | 13   | -     | -      |

| GIO.ĪNT0     | 14   | 0     | 0      |

| GIO.BREQ(n)  | 15   | -     | 0      |

| GND          | 16   | -     | -      |

| GIO.READ     | 17   | I     | 0      |

| GIO.ĀS       | 18   | I     | 0      |

| VCC          | 19   | -     | -      |

| GIO.MASDLY   | 20   | I     | 0      |

| GND          | 21   | -     | -      |

| GIO.AD00     | 22   | I/O   | I/O    |

| GIO.AD02     | 23   | I/O   | I/O    |

| GND          | 24   | -     | -      |

| GIO.AD04     | 25   | I/O   | I/O    |

| GIO.AD06     | 26   | I/O   | I/O    |

| GND          | 27   | -     | -      |

| GIO.AD08     | 28   | I/O   | I/O    |

| GIO.AD10     | 29   | I/O   | I/O    |

| GND          | 30   | -     | -      |

| GIO.AD12     | 31   | I/O   | I/O    |

SGI CONFIDENTIAL GIO32 Slot Pinout

| SIGNAL           | PIN# | SLAVE | MASTER |

|------------------|------|-------|--------|

| GIO.AD14         | 32   | I/O   | I/O    |

| SLOTID           | 33   | -     | -      |

| GND              | 34   | -     | -      |

| GIO.AD16         | 35   | I/O   | I/O    |

| VCC              | 36   | -     | -      |

| GIO.AD18         | 37   | I/O   | I/O    |

| GND              | 38   | -     | -      |

| GIO.AD20         | 39   | I/O   | I/O    |

| GIO.AD22         | 40   | I/O   | I/O    |

| GND              | 41   | -     | -      |

| GIO.AD24         | 42   | I/O   | I/O    |

| GND              | 43   | -     | -      |

| GIO.AD26         | 44   | I/O   | I/O    |

| GND              | 45   | -     | -      |

| GIO.AD28         | 46   | I/O   | I/O    |

| GIO.AD30         | 47   | I/O   | I/O    |

| -12V             | 48   | -     | -      |

| RESERVED N/C     | 49   | -     | -      |

| GND              | 50   | -     | -      |

| RESERVED N/C     | 51   | -     | -      |

| RESERVED N/C     | 52   | -     | -      |

| RESERVED N/C     | 53   | -     | -      |

| GND              | 54   | -     | -      |

| RESERVED N/C     | 55   | -     | -      |

| RESERVED N/C     | 56   | -     | -      |

| RESERVED N/C     | 57   | -     | -      |

| RESERVED N/C     | 58   | -     | -      |

| GND <sup>a</sup> | 59   | -     | -      |

| GIO.BGNT(n)      | 60   | -     | I      |

| GIO.BPRE         | 61   | -     | I      |

| GND              | 62   | -     | -      |

| GIO.ĪNT01        | 63   | 0     | 0      |

| GIO.ĪNT02        | 64   | 0     | 0      |

| GND              | 65   | -     | -      |

| GIO.SLVDLY       | 66   | 0     | I      |

| GND              | 67   | -     | -      |

| SIGNAL   | PIN# | SLAVE | MASTER |

|----------|------|-------|--------|

| GIO.CLK  | 68   | I     | I      |

| GND      | 69   | -     | -      |

| GIO.AD01 | 70   | I/O   | I/O    |

| VCC      | 71   | -     | -      |

| GIO.AD03 | 72   | I/O   | I/O    |

| GND      | 73   | -     | -      |

| GIO.AD05 | 74   | I/O   | I/O    |

| GIO.AD07 | 75   | I/O   | I/O    |

| GND      | 76   | -     | -      |

| GIO.AD09 | 77   | I/O   | I/O    |

| GND      | 78   | -     | -      |

| GIO.AD11 | 79   | I/O   | I/O    |

| VCC      | 80   | -     | -      |

| GIO.AD13 | 81   | I/O   | I/O    |

| GND      | 82   | -     | -      |

| GIO.AD15 | 83   | I/O   | I/O    |

| GND      | 84   | -     | -      |

| GIO.AD17 | 85   | I/O   | I/O    |

| GIO.AD19 | 86   | I/O   | I/O    |

| GND      | 87   | -     | -      |

| GIO.AD21 | 88   | I/O   | I/O    |

| GND      | 89   | -     | -      |

| GIO.AD23 | 90   | I/O   | I/O    |

| GIO.AD25 | 91   | I/O   | I/O    |

| VCC      | 92   | -     | -      |

| GIO.AD27 | 93   | I/O   | I/O    |

| GND      | 94   | -     | -      |

| GIO.AD29 | 95   | I/O   | I/O    |

| GIO.AD31 | 96   | I/O   | I/O    |

a. This pin is used for differentiating btween GIO32 and GIO32-bis boards.

SGI CONFIDENTIAL Introduction

# Chapter 3

# **GIO32-bis Specification**

#### 3.1 Introduction

The GIO32-bis bus is a 32-bit version of the GIO64 Bus. It obeys the timing specifications of the GIO64 with the GIO32 pinout. In general, GIO32-bis is correctly described by Chapter 2 except for those items specified below. Two items differentiate GIO32 from GIO32-bis:

- one of the GIO32 pins is redefined for differentiating GIO32 and GIO32-bis devices, and

- the timing protocols for master and slave delay signals.

# 3.2 Pin for Differentiating GIO32 from GIO32-bis

The grounded pin labeled GND #59 in the GIO32 Specification, is tied high on GIO32-bis slots. This makes it possible for GIO devices to tell whether they are plugged into a GIO32 or a GIO32-bis slot.

#### 3.3 GIO32-bis Bus Transfers

This timing described in this section is identical to that in the GIO64 section "Nonpipelined GIO64 Bus Transfers." The use of MASDLY and SLVDLY is slightly different from (and incompatible with) the section "GIO32 Bus Transfers" in the GIO32 Specification. The device *driving* data onto the bus asserts its delay signal (MASDLY for memory writes or SLVDLY for memory reads) synchronously with the data, as in GIO32. However, in GIO32-bis, the device *receiving* data from the bus must assert its delay line (MASDLY for memory reads, SLVDLY for memory writes) one clock earlier than in GIO32.

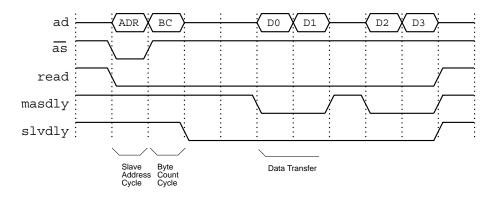

#### 3.3.1 GIO32-bis Bus Writes

GIO32-bis bus writes start with a slave address and byte count cycle. The READ signal will be deasserted in the slave address cycle to indicate that this is a write cycle. After the slave address cycle, the READ signal is used to indicate that a bus cycle is in progress and will remain low for the rest of the transfer.

After the third cycle, data can be transferred. During a write, the bus master will drive data out onto the bus and drive MASDLY low to indicate that valid data is on the bus. The master looks at the SLVDLY signal that was sent the cycle before to determine if the slave can accept the data. If the SLVDLY signal was not low in the previous cycle, the master must continue driving the current data until SLVDLY is low in the previous cycle. This is a change from the GIO32 bus in that the SLVDLY signal is flopped and used in the next cycles instead of being used in the cycle it is on the bus. This change is necessary so that the SLVDLY signal can be directly registered before any gating takes place. This provides one whole cycle for the signal propagation between chips and one whole cycle for on-chip gating. The GIO32 bus scheme

GIO32-bis Bus Transfers SGI CONFIDENTIAL

works at 33 MHz, but at higher speeds it becomes very difficult to get the timing to work. The bus master can continue to transfer new data every cycle that SLVDLY from the previous cycle is low. If SLVDLY was not low then the current data must be driven until SLVDLY is deasserted in the previous cycle. The master can throttle the transfer by driving MASDLY high during a cycle that it does not have new data to transfer. Note that this remains the same as GIO32 and is not sent one cycle early like SLVDLY.

Since SLVDLY is being sent for the next cycle, it will take an extra cycle for all complete transfers, (not one cycle per word). A one word write will take at least four cycles. This is one more cycle then it took with the GIO32 bus.

The bus master continues to transfer data until the byte count is satisfied. The bus slave also keeps track of the number of bytes that have been transferred so that the last write will be handled correctly if it is a partial word transfer. At the end of the transfer the master drives READ high. Two cycles after the slave receives the last piece of data it drives SLVDLY high and in the following cycle tristates the SLVDLY signal. The bus master will tristate the AD, READ, AS, and MASDLY signals two cycles after the last piece of data is transferred if it does not have another transfer to execute. The master does not have to drive the MASDLY and READ signals high before tristating them. If it does have another transfer it can drive the address in the cycle immediately following the last piece of data.

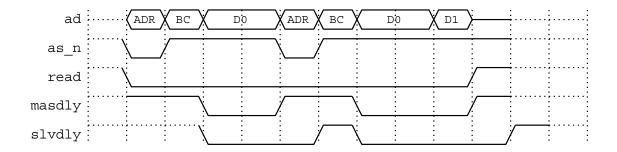

If a transfer is preempted, the byte count will not be zero when the READ signal is driven high by the bus master. The slave needs to monitor the READ signal and not just the remaining byte count, so that it can tell if a transfer has been preempted. The bus master must keep all of the information that is necessary to restart the transfer where it left off. This includes the slave data address. Below are some examples of GIO32-bis writes.

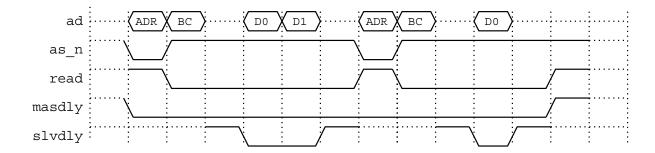

Figure 3-1. Back-to-Back Simple GIO32-bis Writes

Figure 3-2. GIO32-bis Write, Slave Stall

3-2 6 May 1992 GIO32-bis Specification

SGI CONFIDENTIAL GIO32-bis Bus Transfers

Figure 3-3. GIO32-bis Write, Master Stalls

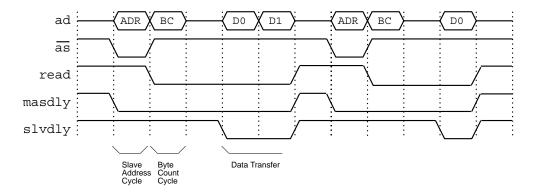

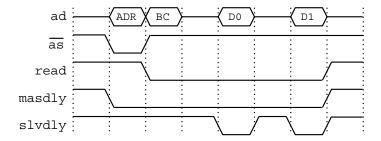

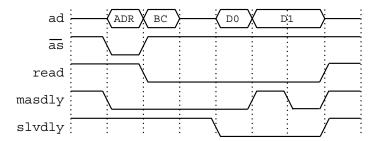

#### 3.3.2 GIO32-bis Bus Reads

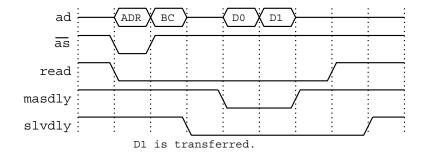

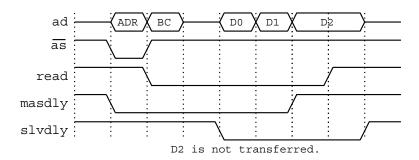

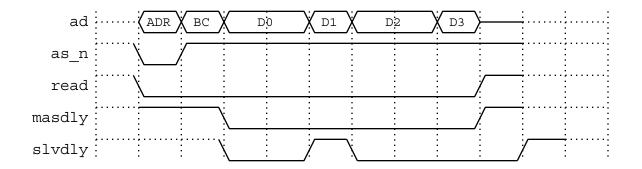

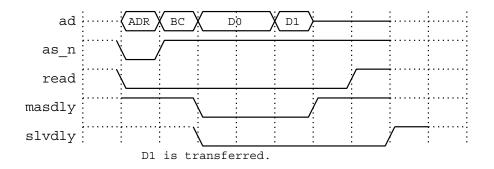

GIO32-bis bus reads are a lot like GIO32-bis bus writes except that the slave is sending the data over the bus instead of the master. Notice that the READ signal is used to indicate that a bus cycle is in progress after the slave address cycle, by being deasserted for the rest of the transfer. Since the slave is sending the data, the SLVDLY signal is used to indicate that there is valid data on the bus and the MASDLY signal is used to indicate to the slave that the master can accept data in the next cycle. Note that this is different from the GIO32 bus in that MASDLY is sent one cycle earlier. The slave must tristate the AD bus signals in the cycle after the last piece of data is transferred. The slave must drive the SLVDLY signal high in the cycle after the last piece of data is transferred and then tristate it in the following cycle. The master will tristate the  $\overline{AS}$ , READ, and MASDLY signals three cycles after the last piece of data has been transferred if it does not have another transfer to execute. If it does have another transfer to do it can drive the address two cycles after the last piece of data has been transferred. Some examples of GIO64 reads are shown below.

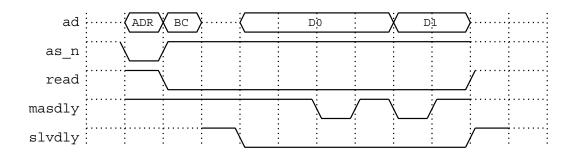

It is important that the slave does not wait for MASDLY to be deasserted before it drives the read data and deasserts SLVDLY, or that once the slave has deasserted SLVDLY and driven the read data, that it does not stop driving it, even if it asserted SLVDLY until the cycle after the master deasserts MASDLY. Figure 3-6 shows this condition.

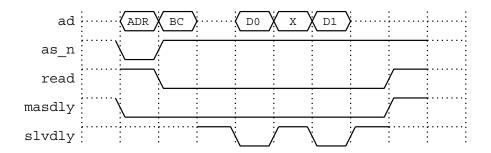

Figure 3-4. Simple GIO32-bis Read

GIO32-bis Bus Transfers

Figure 3-5. GIO32-bis Read, Slave Delay

Figure 3-6. GIO32-bis Read, Master Delay

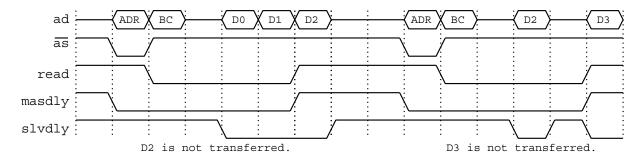

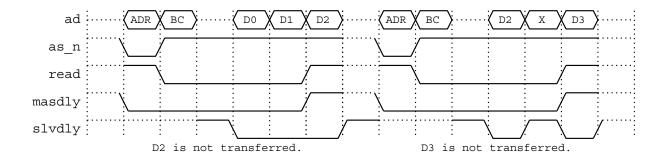

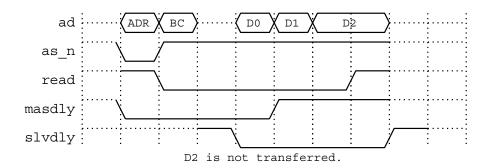

# 3.3.3 GIO32-bis Preemption

When a GIO32-bis device gets preempted, the master drives the READ signal high to indicate an end of the transfer. For GIO32-bis writes, the bus master also stops driving data and MASDLY in the same cycle as it stops driving READ. GIO32-bis reads are preempted in basically the same way, except that the slave may continue driving data in the cycle that the master drives the READ and MASDLY signals high. The data that the slave sends in the cycle that READ is driven high is not accepted. The bus master must tristate all of the signals it is driving in the cycle after READ is driven high. The slave must drive SLVDLY high in the cycle after READ is driven high and tristate it in the following cycle. Different preemption cases are shown below.

Figure 3-7. Preempted GIO32-bis Write, Slave Stall

3-4 6 May 1992 GIO32-bis Specification

SGI CONFIDENTIAL GIO32-bis Bus Transfers

Figure 3-8. Preempted GIO32-bis Write, Master Stall

Figure 3-9. Preempted GIO32-bis Reads, Slave Stall

Figure 3-10. Preempted GIO32-bis Reads, Mater Stall

GIO32-bis Bus Transfers SGI CONFIDENTIAL

This page has been left blank intentionally.

#### 4.1 Introduction

The GIO64 bus is a 64-bit, synchronous, multiplexed address-data bus that can run at speeds up to 40 MHz. The bus supports both 32- and 64-bit GIO64 devices. This bus is used to connect high speed devices to main memory. It is also possible for the CPU to issue reads and writes to GIO64 devices.

The maximum bandwidth of this bus is 320 MBytes/second for burst transfers running at 40 MHz.

There are two different forms of the GIO64 bus. The first form is the bus that is local to system memory. This form will just be referred to as the GIO64 bus or the nonpipelined GIO64 bus. The second form of the bus is a pipelined version of the GIO64 bus. This form of the bus is used by devices that plug into GIO64 slots, like graphics. There is a bidirectional pipeline register between the GIO64 bus that connects to main memory and the devices in the GIO64 slots. This second form of GIO64 will always be referred to as pipelined GIO64 bus. The two forms of the bus are basically the same except that the handshaking signals are different on the two different forms of the bus.

# 4.2 Conventions Used in this Chapter

## 4.2.1 Byte Addressing

The GIO64 bus uses a 32 bit byte address. This can be a big or little endian address. One of the control bits indicates the endianess of the bus. The bus itself does not do anything different for big or little endian transfers, but the devices that are on the bus need to know if the data is big or little endian data so that they can interpret the address and byte count correctly.

For devices that cannot switch between big and little endian mode the software will be responsible for fixing the data if it is necessary. Transfers that are not word aligned between 32 bit devices will not work if the two devices are running in a different endian modes. The same is true for 64 bit devices that are transferring data that is not double word aligned. In both cases the wrong data is written since the address of the bytes are different.

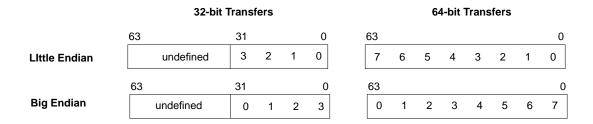

For a big endian 32 bit transfer, byte 0 is bits (31:24), byte 1 is bits (23:16), byte 2 is bits (15:8), and byte 3 is bits (7:0). For a big endian 64 bit transfer, byte 0 is bits (63:56), byte 1 is bits (55:48), byte 2 is bits (47:40), byte 3 is bits (39:32), byte 4 is bits (31:24), byte 5 is bits (23:16), byte 6 is bits (15:8), and byte 7 is bits (7:0). Little-endian is just the opposite so for a 32 bit transfer, byte 0 is bits (7:0), byte 1 is bits (15:8), byte 2 is bits (23:16), and byte 3 is bits (31:24). For a 64 bit little endian transfer, byte 0 is bits (7:0), byte 1 is bits (15:8), byte 2 is bits (23:16), byte 3 is bits (31:24), byte 4 is bits (39:32), byte 5 is bits (47:40), byte 6 is bits(55:48), and byte 7 is bits (63:56).

The bit numbering scheme is always little-endian, so that bit zero is always the least significant bit and bit 63 is the most significant bit.

The following tables show byte addressing for the big and little endian modes.

TABLE 3 Big Endian Words: addresses of bytes.

| BITS         | 3124 | 2316 | 158 | 70 |  |

|--------------|------|------|-----|----|--|

| Word Address |      |      |     |    |  |

| 8            | 8    | 9    | 10  | 11 |  |

| 4            | 4    | 5    | 6   | 7  |  |

| 0            | 0    | 1    | 2   | 3  |  |

TABLE 4 Big Endian Double Words: addresses of bytes.

| BITS         | 6356 | 5548 | 4740 | 3932 | 3124 | 2316 | 158 | 70 |

|--------------|------|------|------|------|------|------|-----|----|

| Word Address |      |      |      |      |      |      |     |    |

| 16           | 16   | 17   | 18   | 19   | 20   | 21   | 22  | 23 |

| 8            | 8    | 9    | 10   | 11   | 12   | 13   | 14  | 15 |

| 0            | 0    | 1    | 2    | 3    | 4    | 5    | 6   | 7  |

TABLE 5 Little Endian Words: addresses of bytes.

| BITS         | 3124 | 2316 | 158 | 70 |

|--------------|------|------|-----|----|

| Word Address |      |      |     |    |

| 8            | 11   | 10   | 9   | 8  |

| 4            | 7    | 6    | 5   | 4  |

| 0            | 3    | 2    | 1   | 0  |

TABLE 6 Little Endian Double Words: addresses of bytes.

| BITS         | 6356 | 5548 | 4740 | 3932 | 3124 | 2316 | 158 | 70 |

|--------------|------|------|------|------|------|------|-----|----|

| Word Address |      |      |      |      |      |      |     |    |

| 18           | 23   | 22   | 21   | 20   | 19   | 18   | 17  | 16 |

| 8            | 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8  |

| 0            | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0  |

SGI CONFIDENTIAL GIO64 Bus Signals

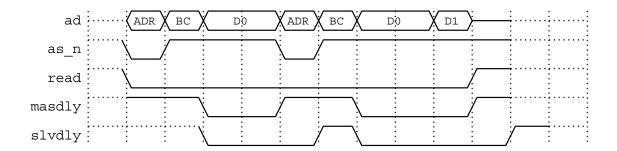

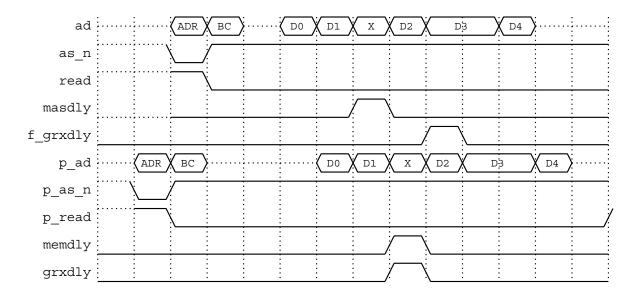

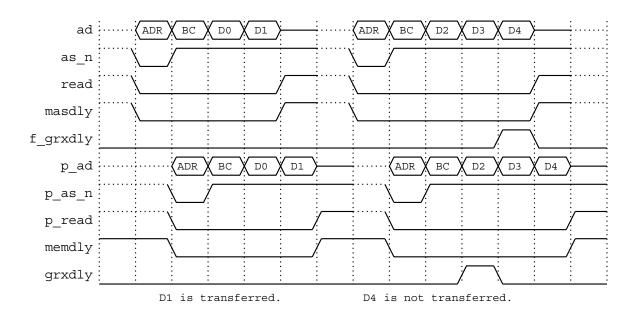

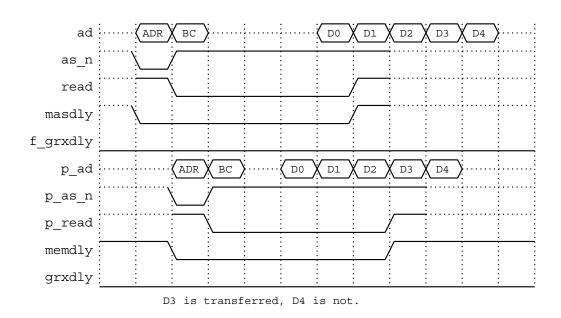

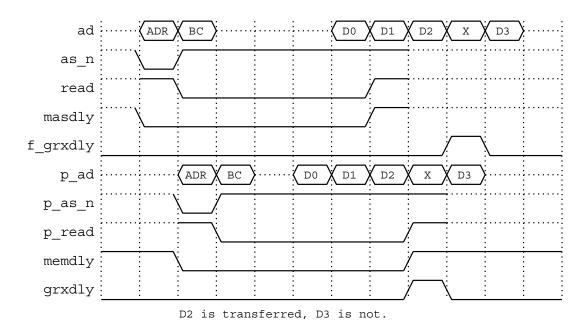

#### 4.2.2 Waveform Conventions

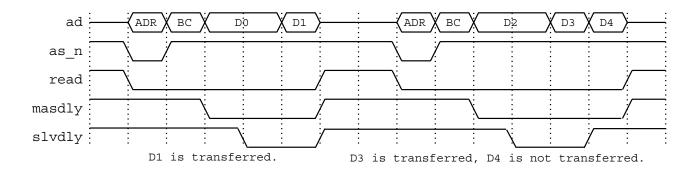

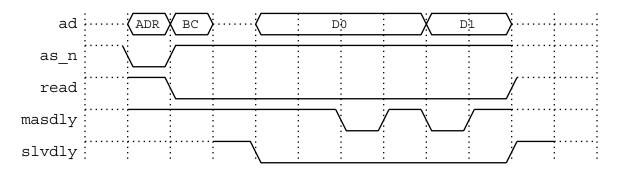

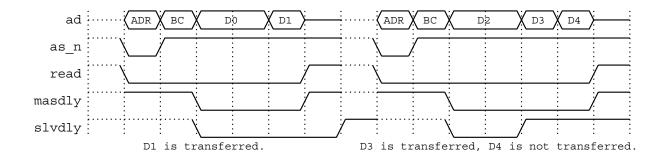

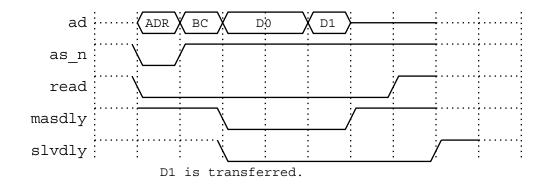

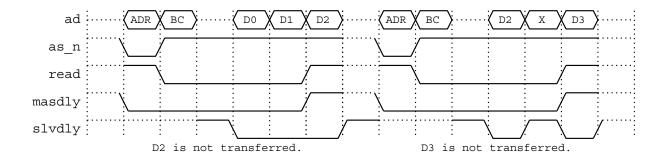

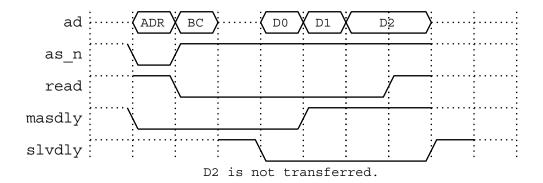

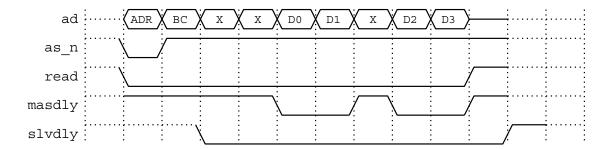

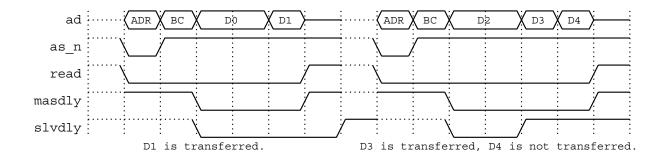

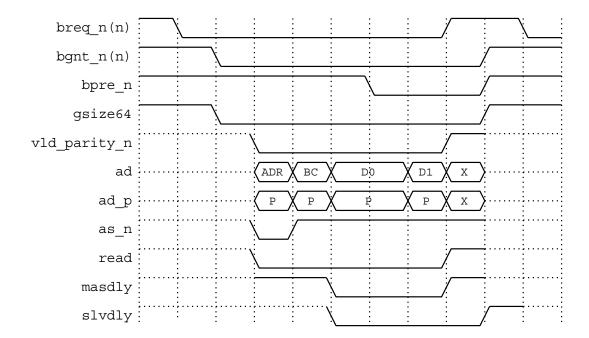

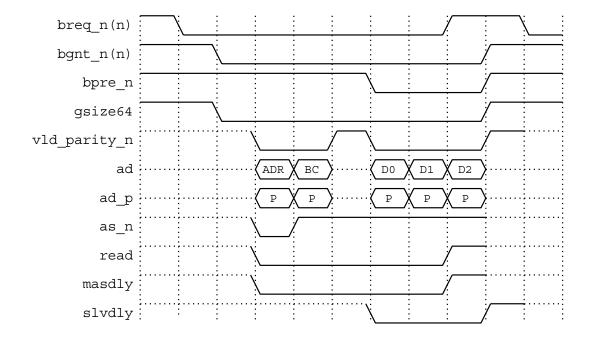

There are many waveform diagrams in this document so it is important to interpret them correctly. The dotted lines represent a signal that has been tristated. A box with "ADR" in it is an address, "BC" is byte count, "D0", "D1" ..., is a data element, and "X" represents invalid data, but not tristate.

# 4.3 GIO64 Bus Signals

# 4.3.1 Non-pipelined Bus Signals

The GIO64 bus has 64 address/data signals AD<63:0>, 8 byte parity signals ADP<7:0>, a valid parity signal  $\overline{\text{VLD\_PARITY}}$ , and four basic control lines. These control lines include address strobe  $\overline{\text{AS}}$ , read READ, master delay MASDLY, and slave delay SLVDLY. In addition to the above, there are bus request  $\overline{\text{BREQ}}(n)$  and bus grant  $\overline{\text{BGNT}}(n)$  signals for each bus master. For long burst devices there is a preempt signal called  $\overline{\text{BPRE}}$ . Sixty-four bit bus slaves also need to get a signal called GSIZE64, which indicates the size of the current bus master.

AD<63:0>: These signals are the multiplexed slave address and data lines. During slave address cycles AD(31:0) will contain the slave address for the bus transaction. The next cycle in a transaction, the byte count cycle, uses AD(31:0) to indicate the number of bytes to transfer, the endian mode of the transfer, the device id of the device being accessed, DMA count direction (for decrementing DMA), subblock ordering (CPU cache misses), and the starting byte address. During slave address and byte count cycles parity should be checked across AD(31:0) if VLD\_PARITY is asserted. The top 32 bits of the address/data bus are never used during slave address and byte count cycles so parity should not be checked across these bits even if VLD\_PARITY is asserted. During data cycles parity should be checked across AD(31:0) for 32 bit transfers and AD(63:0) for 64 bit transfers if VLD\_PARITY is asserted. For a 32 bit device all 4 bytes of the bus should be driven with correct parity if VLD\_PARITY is asserted even for single byte transfers. Likewise, for 64 bit transfers, all 8 bytes should be driven with correct parity if VLD\_PARITY is asserted.

ADP(7:0): Even byte parity is used across the address/data bus. Parity should be checked if VLD\_PARITY is asserted with the data on the bus. ADP(0) is the parity bit for AD(7:0), ADP(1) covers AD(15:8), etc. These signals can be driven by the bus master during slave address, byte count, and write data cycles. They can be driven by the addressed bus slave during read cycles. During slave address cycles, byte count cycles and 32 bit transfers, ADP(7:4) are unused. If VLD PARITY is not asserted then ADP(7:0) are undefined.

VLD\_PARITY: This signal indicates that valid parity is being driven on the bus. This signal will be asserted in the same cycle as there is data on the bus. Devices that are receiving addresses or data should check parity if VLD\_PARITY is asserted. This signal is pulled up on the board so if a device does not generate parity it does not have to drive the VLD\_PARITY signal. This signal is driven by the bus master during slave address, byte count, and write data cycles. It is driven by the addressed bus slave during read cycles. It is strongly encouraged that all GIO64 devices should generate and check parity. Parity should not be checked on data from bus cycles where no data was transferred, as determined by the state of MASDLY or SLVDLY. The slave or master that is driving this signal must drive it high before they tristate it in the cycle after they are finished driving the AD signals.

$\overline{\text{AS}}$ : The address strobe is asserted whenever there is a slave address cycle on the bus. All devices on the bus should flop the address that is being driven on the bus to determine if they are the device that is being addressed. The byte count cycle is always the next cycle after the slave address cycle. The address strobe is only asserted during the slave address cycle. This signal should only be driven by a bus master that owns the GIO64 bus.

READ: The READ signal serves two purposes. During the slave address cycle the READ signal is used as its name implies to indicate that this is a read transaction, (the bus master will be receiving data). After the slave address cycle, the READ signal is driven low to indicate that a active bus cycle is taking place. When a transaction is preempted the READ signal is driven high to indicate to the slave that the transaction has been preempted. This signal should only be driven by a bus master that owns the GIO64 bus.

MASDLY: The master delay signal, MASDLY, is used by the bus master to throttle the data transfer rate. The state of the MASDLY signal does not affect the slave address or byte count cycles. This signal has two different meanings for read and write transactions. For a read transaction, when MASDLY is asserted it indicates that the bus master cannot receive

GIO64 Bus Signals SGI CONFIDENTIAL

data in the next cycle. During write transactions, when the MASDLY signal is asserted it indicates that the data currently on the bus is invalid. Only a bus master that owns the GIO64 bus should drive the MASDLY signal.

SLVDLY: The slave delay signal, SLVDLY, is used by the addressed bus slave to throttle the data transfer rate. This signal has no effect on the address or byte count cycles. Like MASDLY, this signal has different meanings for reads and writes. When SLVDLY is asserted during a bus reads, it indicates that the data on the bus is invalid. For bus writes, this signal is asserted when the slave cannot accept data in the next cycle. This signal is pulled high on the board so that during the byte count cycle it will be asserted, but it must be driven high by the slave when a transfer is finished, before the slave can tristates this signal. Only the addressed slave device should drive this signal.

BREQ(n): There is a unique bus request for every bus master in the system. To request the bus the bus master asserts its bus request signal. The bus master must keeps its bus request signal asserted until it is finished using the bus. Once a bus master has asserted its bus request signal it is not allowed to take it away until it has been granted the bus, even it the device decides it does not need the bus. When a devices that owns the bus has been preempted, it must deassert its bus request signal to indicate that it is off the bus. A preempted device cannot assert its bus request signal until the preemption signal has been deasserted. A bus master must still accept requests from other bus masters even if it is requesting the bus. If it does not do this, transfers to the device that is requesting the bus will time-out and will not be completed.

BGNT(n): There is a unique bus grant signal for each bus master on the GIO64 bus. The bus grant signal is used to indicate to a GIO64 master that it owns the bus. The grant signal will be asserted as long as the device asserts its bus request signal, BREQ(n), indicating that it owns the GIO64 bus. When a device is preempted the bus grant signal will not be deasserted until the device deasserts its bus request signal. This signal is driven by the GIO64 arbiter.

BPRE: The bus preempt signal is asserted by the GIO64 arbiter to preempt the current bus transaction. Once the preempt signal is asserted, a device must get off the bus within 4 GIO64 clock cycles, and deassert its BREQ(n) signal. This signal is driven by the GIO64 arbiter.

GSIZE64: The GSIZE64 signal is driven by the GIO64 arbiter to indicate to 64 bit GIO64 slaves the size of the bus master. A 64 bit GIO64 slave must be able to accept transactions from 32 or 64 bit bus masters. It is the responsibility of 64 bit GIO64 bus masters to know if the slave they are addressing is a 32 or 64 bit slave. If it is a 32 bit slave then obviously a 32 bit transfer will take place. This should not be a problem since most bus masters will only have to know if the memory interface is 32 or 64 bits.

# 4.3.2 Pipelined GIO64 Bus Signals