# **MIPS**

# R8000 MICROPROCESSOR CHIP SET

# **USERS MANUAL**

Revision 3.0 July, 1994

**Steve Rhodes**

Silicon Graphics Computer Systems MIPS Technologies, Incorporated 2011 N. Shoreline Blvd. Mountain View, CA. 94039 The information in this document is subject to change without notice.

Silicon Graphics, Inc. (SGI) reserves the right to change any portion of the product described herein to improve function or design. SGI does not assume liability arising out of the application or use of any product or circuit described herein. No part of this document may be copied by any means without written permission of Silicon Graphics, Inc.

| 1 | INTR | ODUCT                                                                                                                                                | TON TO THE R8000 MICROPROCESSOR CHIP SET                                                                                                                                                                                                                                                    | 1-1                                                                        |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|   | 1.1  | R8000                                                                                                                                                | MICROPROCESSOR CHIP SET FEATURES                                                                                                                                                                                                                                                            | 1-2                                                                        |

|   | 1.2  | ARCI                                                                                                                                                 | HITECTURAL INNOVATIONS                                                                                                                                                                                                                                                                      | 1-3                                                                        |

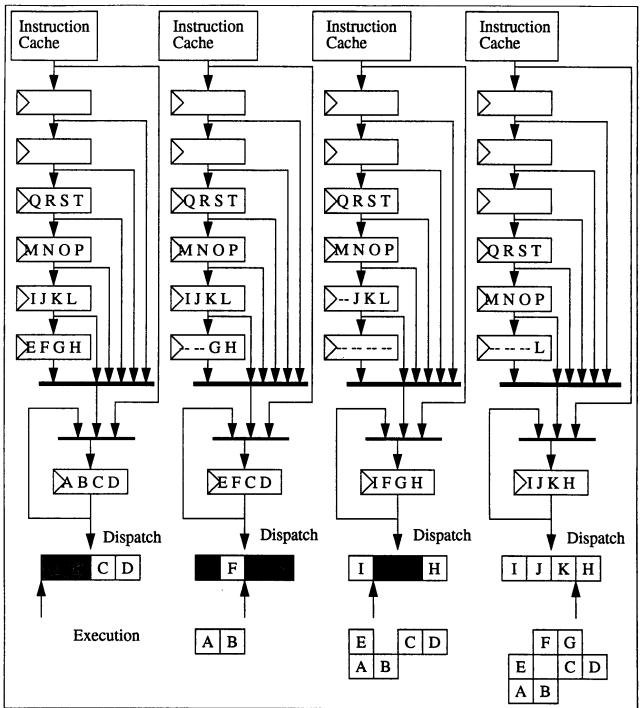

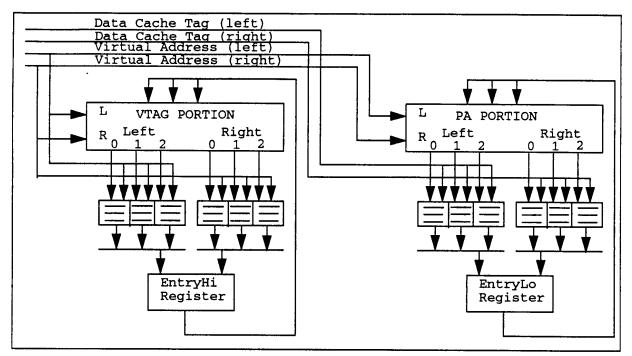

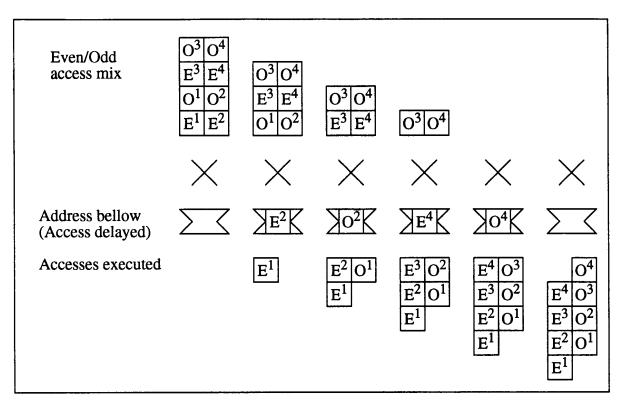

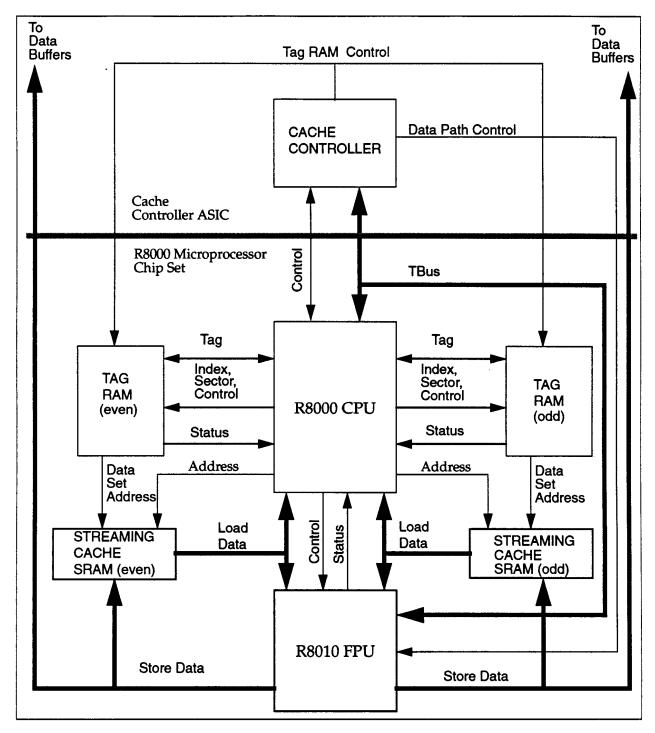

|   |      | 1.2.1<br>1.2.2<br>1.2.3<br>1.2.4<br>1.2.5<br>1.2.6<br>1.2.7<br>1.2.8<br>1.2.9<br>1.2.10<br>1.2.11                                                    | Five Stage Pipeline Superscalar Dispatch Unit Large Set Associative TLB Data Cache Invalidation Split Level Cache Address Bellow Register Integer Multiply Floating Point Multiply-Add Floating Point Queues Prefetch Support Conditional Moves                                             | 1-5<br>1-8<br>1-10<br>1-10<br>1-13<br>1-13<br>1-13                         |

|   | 1.3  | ARCI                                                                                                                                                 | HITECTURAL OVERVIEW                                                                                                                                                                                                                                                                         |                                                                            |

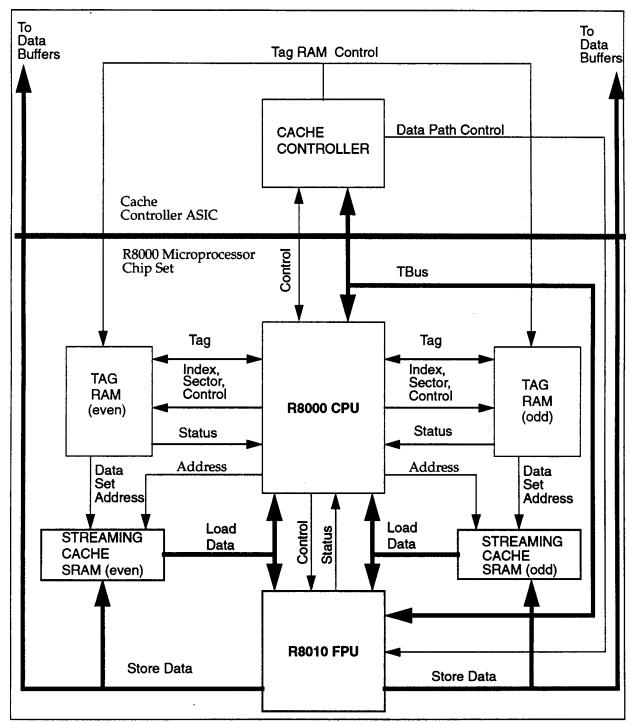

|   |      | 1.3.1                                                                                                                                                | R8000 Microprocessor.                                                                                                                                                                                                                                                                       | 1-17                                                                       |

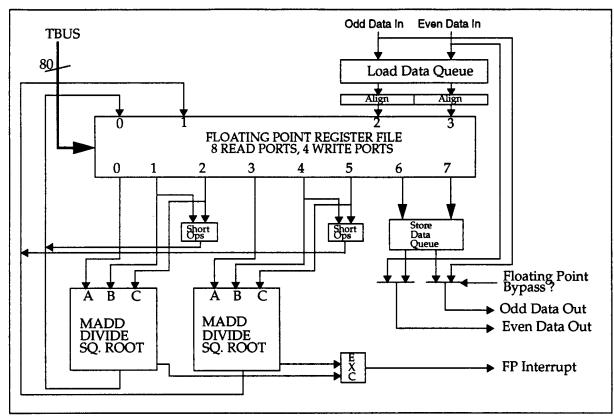

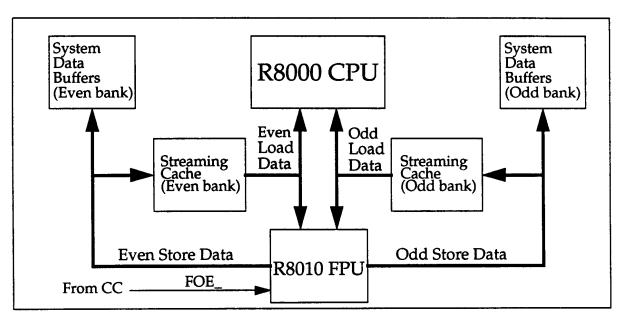

|   |      | 1.3.2                                                                                                                                                | R8010 Floating Point Unit                                                                                                                                                                                                                                                                   | 1-20                                                                       |

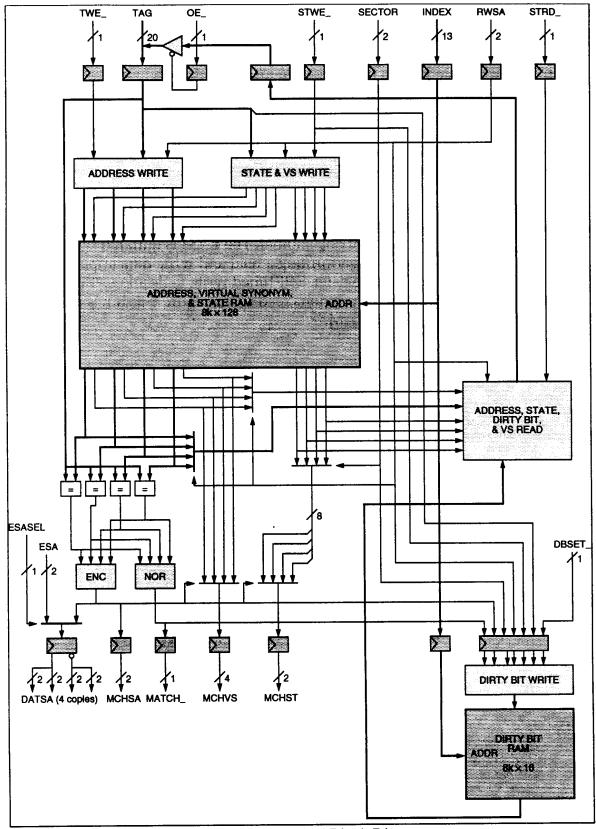

|   |      | 1.3.3                                                                                                                                                | Tag RAM                                                                                                                                                                                                                                                                                     |                                                                            |

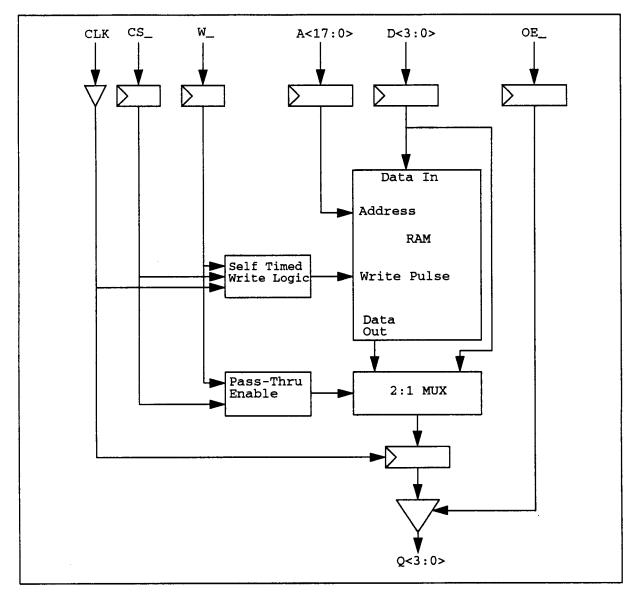

|   |      | 1.3.4                                                                                                                                                | Streaming Cache Data RAM's                                                                                                                                                                                                                                                                  | 1-24                                                                       |

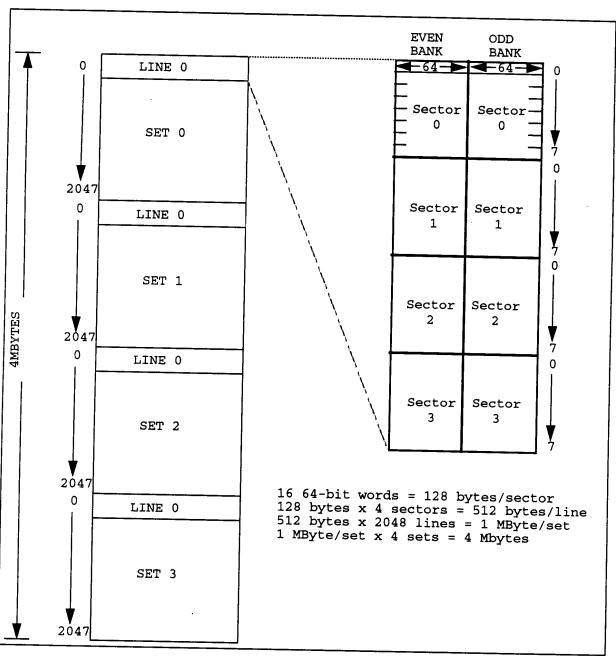

|   |      | 1.3.5                                                                                                                                                | Streaming Cache Memory Architecture                                                                                                                                                                                                                                                         | 1-25                                                                       |

| 2 |      |                                                                                                                                                      |                                                                                                                                                                                                                                                                                             |                                                                            |

|   | 2.1  | COPF                                                                                                                                                 | ROCESSOR 0 REGISTER SET                                                                                                                                                                                                                                                                     |                                                                            |

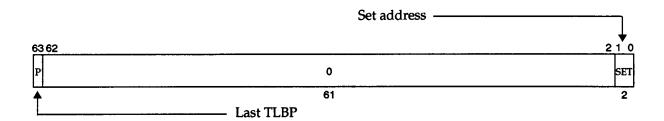

|   |      |                                                                                                                                                      | TLBSet (r0)                                                                                                                                                                                                                                                                                 | 2-3                                                                        |

|   |      | 2.1.1                                                                                                                                                |                                                                                                                                                                                                                                                                                             |                                                                            |

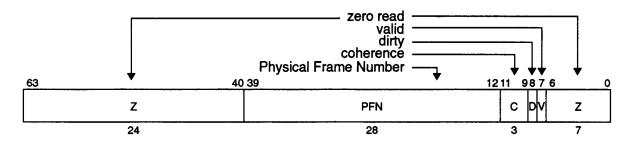

|   |      | 2.1.1<br>2.1.2                                                                                                                                       | EntryLo (r2)                                                                                                                                                                                                                                                                                | 2-4                                                                        |

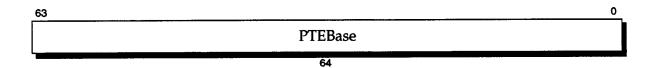

|   |      |                                                                                                                                                      | EntryLo (r2)UBase (r4)                                                                                                                                                                                                                                                                      | 2-4<br>2-5                                                                 |

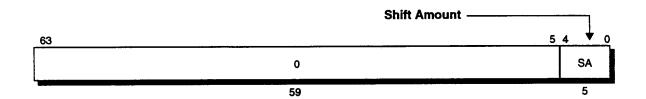

|   |      | 2.1.2                                                                                                                                                | EntryLo (r2)                                                                                                                                                                                                                                                                                | 2-4<br>2-5<br>2-6                                                          |

|   |      | 2.1.2<br>2.1.3                                                                                                                                       | EntryLo (r2)                                                                                                                                                                                                                                                                                | 2-4<br>2-5<br>2-6<br>2-7                                                   |

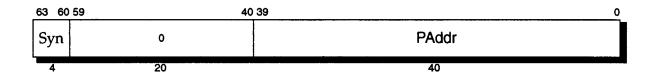

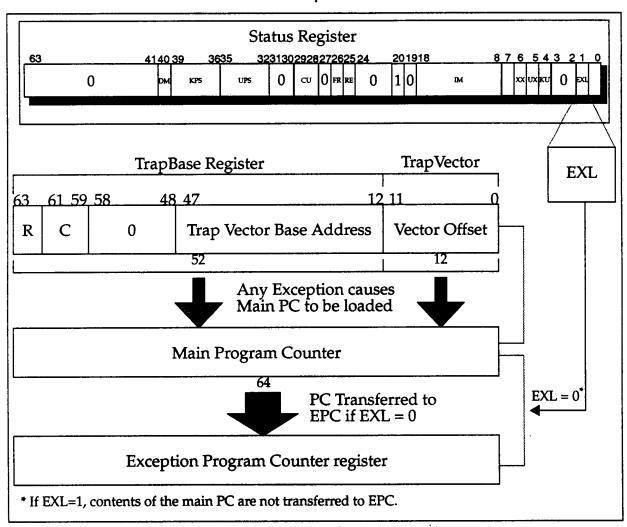

|   |      | 2.1.2<br>2.1.3<br>2.1.4                                                                                                                              | EntryLo (r2)  UBase (r4)  ShiftAmt (r5)  TrapBase (r6)  BadPAddr (r7)                                                                                                                                                                                                                       | 2-4<br>2-5<br>2-6<br>2-7<br>2-8                                            |

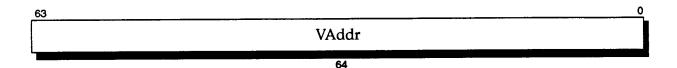

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5                                                                                                                     | EntryLo (r2) UBase (r4) ShiftAmt (r5) TrapBase (r6) BadPAddr (r7) VAddr (r8)                                                                                                                                                                                                                | 2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9                                     |

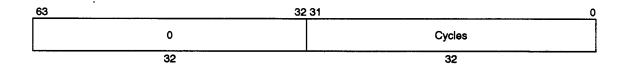

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6                                                                                                            | EntryLo (r2)  UBase (r4)  ShiftAmt (r5)  TrapBase (r6)  BadPAddr (r7)  VAddr (r8)  Counts (r9)                                                                                                                                                                                              | 2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9                                     |

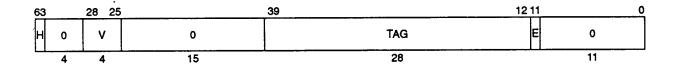

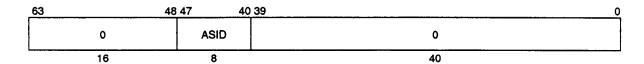

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7                                                                                                   | EntryLo (r2)  UBase (r4)  ShiftAmt (r5)  TrapBase (r6)  BadPAddr (r7)  VAddr (r8)  Counts (r9)  EntryHi (r10)                                                                                                                                                                               | 2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11                     |

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8                                                                                          | EntryLo (r2)  UBase (r4)  ShiftAmt (r5)  TrapBase (r6)  BadPAddr (r7)  VAddr (r8)  Counts (r9)  EntryHi (r10)  Status (r12)                                                                                                                                                                 | 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11                                          |

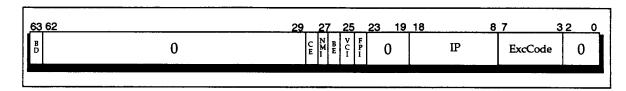

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9                                                                                 | EntryLo (r2)  UBase (r4)  ShiftAmt (r5)  TrapBase (r6)  BadPAddr (r7)  VAddr (r8)  Counts (r9)  EntryHi (r10)  Status (r12)  Cause (r13)                                                                                                                                                    | 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12                                     |

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9<br>2.1.10                                                                       | EntryLo (r2)  UBase (r4)  ShiftAmt (r5)  TrapBase (r6)  BadPAddr (r7)  VAddr (r8)  Counts (r9)  EntryHi (r10)  Status (r12)  Cause (r13)  Exception Program Counter (r14)                                                                                                                   | 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12 2-14                                |

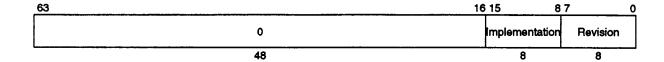

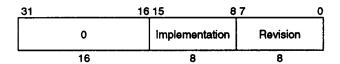

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9<br>2.1.10<br>2.1.11                                                             | EntryLo (r2)  UBase (r4)  ShiftAmt (r5)  TrapBase (r6)  BadPAddr (r7)  VAddr (r8)  Counts (r9)  EntryHi (r10)  Status (r12)  Cause (r13)  Exception Program Counter (r14)  Process Revision Identifier (r15)                                                                                | 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12 2-14 2-16 2-17                      |

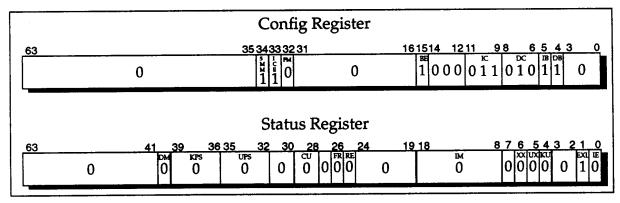

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9<br>2.1.10<br>2.1.11<br>2.1.12                                                   | EntryLo (r2)  UBase (r4)  ShiftAmt (r5)  TrapBase (r6)  BadPAddr (r7)  VAddr (r8)  Counts (r9)  EntryHi (r10)  Status (r12)  Cause (r13)  Exception Program Counter (r14)  Process Revision Identifier (r15)  Config (r16)                                                                  | 2-4 2-5 2-6 2-7 2-8 2-10 2-11 2-12 2-14 2-16 2-17 2-18                     |

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9<br>2.1.10<br>2.1.11<br>2.1.12<br>2.1.13                                         | EntryLo (r2) UBase (r4) ShiftAmt (r5) TrapBase (r6) BadPAddr (r7) VAddr (r8) Counts (r9) EntryHi (r10) Status (r12) Cause (r13) Exception Program Counter (r14) Process Revision Identifier (r15) Config (r16) Work0 (r18), Work1 (r19)                                                     | 2-4 2-5 2-6 2-7 2-8 2-10 2-11 2-12 2-14 2-16 2-18 2-19                     |

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9<br>2.1.10<br>2.1.11<br>2.1.12<br>2.1.13<br>2.1.14                               | EntryLo (r2)  UBase (r4)  ShiftAmt (r5)  TrapBase (r6)  BadPAddr (r7)  VAddr (r8)  Counts (r9)  EntryHi (r10)  Status (r12)  Cause (r13)  Exception Program Counter (r14)  Process Revision Identifier (r15)  Config (r16)  Work0 (r18), Work1 (r19)  PBase (r20)                           | 2-4 2-5 2-6 2-7 2-8 2-10 2-11 2-12 2-14 2-16 2-17 2-18 2-19                |

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9<br>2.1.10<br>2.1.11<br>2.1.12<br>2.1.13<br>2.1.14<br>2.1.15                     | EntryLo (r2)  UBase (r4)  ShiftAmt (r5)  TrapBase (r6)  BadPAddr (r7)  VAddr (r8)  Counts (r9)  EntryHi (r10)  Status (r12)  Cause (r13)  Exception Program Counter (r14)  Process Revision Identifier (r15)  Config (r16)  Work0 (r18), Work1 (r19)  PBase (r20)  GBase (r21)              | 2-4 2-5 2-6 2-7 2-8 2-10 2-11 2-12 2-14 2-16 2-17 2-18 2-19 2-20 2-21      |

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9<br>2.1.10<br>2.1.11<br>2.1.12<br>2.1.13<br>2.1.14<br>2.1.15<br>2.1.16           | EntryLo (r2)  UBase (r4)  ShiftAmt (r5)  TrapBase (r6)  BadPAddr (r7)  VAddr (r8)  Counts (r9)  EntryHi (r10)  Status (r12)  Cause (r13)  Exception Program Counter (r14)  Process Revision Identifier (r15)  Config (r16)  Work0 (r18), Work1 (r19)  PBase (r20)  GBase (r21)  Wired (r24) | 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 2-12 2-14 2-16 2-17 2-18 2-19 2-20 2-21  |

|   |      | 2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9<br>2.1.10<br>2.1.11<br>2.1.12<br>2.1.13<br>2.1.14<br>2.1.15<br>2.1.16<br>2.1.17 | EntryLo (r2)  UBase (r4)  ShiftAmt (r5)  TrapBase (r6)  BadPAddr (r7)  VAddr (r8)  Counts (r9)  EntryHi (r10)  Status (r12)  Cause (r13)  Exception Program Counter (r14)  Process Revision Identifier (r15)  Config (r16)  Work0 (r18), Work1 (r19)  PBase (r20)  GBase (r21)              | 2-4 2-5 2-6 2-7 2-8 2-10 2-11 2-12 2-14 2-16 2-17 2-18 2-19 2-20 2-21 2-22 |

|   | 2.2  | COPI                                                                          | ROCESSOR 1 REGISTER SET2-25                                                                                                                                                                                                                                  |

|---|------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 2.2.1<br>2.2.2                                                                | FConfig (f0)                                                                                                                                                                                                                                                 |

| 3 | MIPS | IV INS                                                                        | TRUCTION SET SUMMARY                                                                                                                                                                                                                                         |

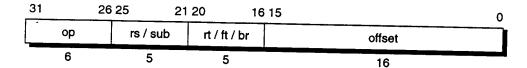

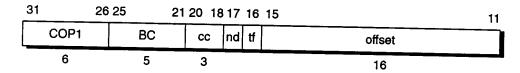

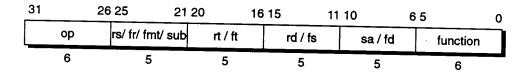

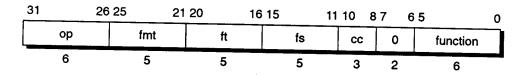

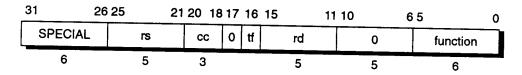

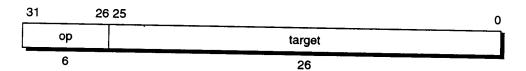

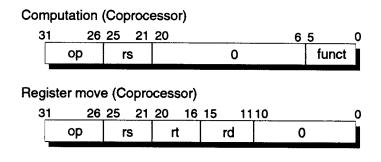

|   | 3.1  | INST                                                                          | RUCTION FORMATS                                                                                                                                                                                                                                              |

|   | 3.2  | LOAI                                                                          | O AND STORE INSTRUCTIONS                                                                                                                                                                                                                                     |

|   |      | 3.2.1<br>3.2.2                                                                | Scheduling a Load Delay Slot                                                                                                                                                                                                                                 |

|   | 3.3  | COM                                                                           | PUTATIONAL INSTRUCTIONS                                                                                                                                                                                                                                      |

|   | 3.4  | JUMI                                                                          | AND BRANCH INSTRUCTIONS 3-7                                                                                                                                                                                                                                  |

|   |      | 3.4.1<br>3.4.2                                                                | Overview of Jump Instructions                                                                                                                                                                                                                                |

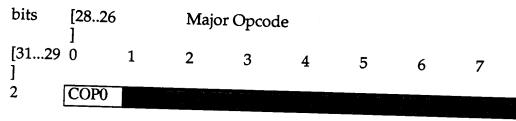

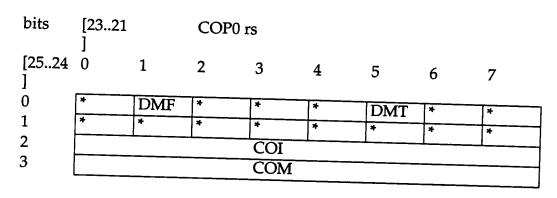

|   | 3.5  | COPI                                                                          | ROCESSOR INSTRUCTIONS3-9                                                                                                                                                                                                                                     |

|   | 3.6  | SUM                                                                           | MARY OF INSTRUCTION SET ADDITIONS3-9                                                                                                                                                                                                                         |

|   |      | 3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>3.6.6<br>3.6.7<br>3.6.8<br>3.6.9 | Indexed Floating Point Load3-9Indexed Floating Point Store3-10Prefetch3-10Branch on Floating Point Coprocessor3-12Integer Conditional Moves3-12Floating Point Multiply-Add3-12Floating Point Compare3-13Floating Point Conditional Moves3-13Reciprocal's3-14 |

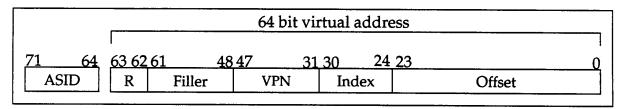

| 4 | MEM  | ORY M                                                                         | ANAGEMENT4-1                                                                                                                                                                                                                                                 |

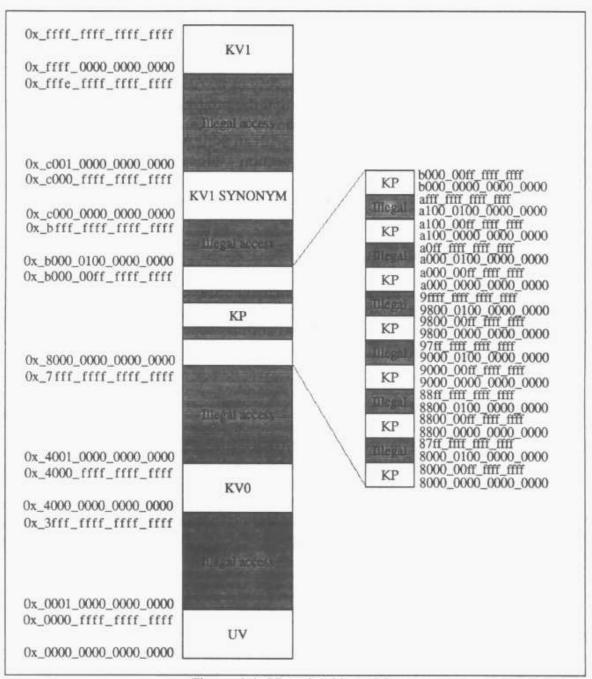

|   | 4.1  | ADD                                                                           | RESS SPACE 4-2                                                                                                                                                                                                                                               |

|   |      | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5                                     | User Virtual (UV) Space 4-4 Kernel Virtual 0 (KV0) Space 4-4 Kernel Virtual 1 (KV1) Space 4-4 Kernel Virtual 1 (KV1) Synonyms 4-4 Kernel Physical Space 4-4                                                                                                  |

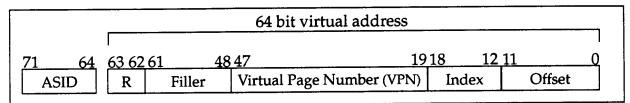

|   | 4.2  | ADD                                                                           | RESS SPACE IDENTIFIERS4-6                                                                                                                                                                                                                                    |

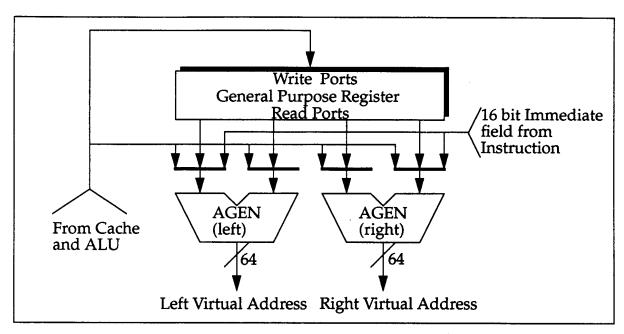

|   | 4.3  | REGI                                                                          | STER ADDRESSING MODES4-6                                                                                                                                                                                                                                     |

|   |      | 4.3.1<br>4.3.2<br>4.3.3                                                       | Register + Register Addressing                                                                                                                                                                                                                               |

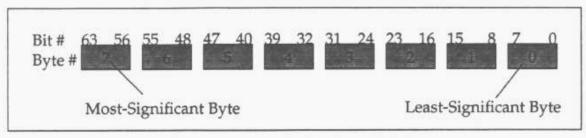

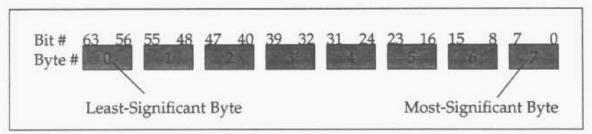

|   | 4.4  | DAT                                                                           | A FORMATS 4-8                                                                                                                                                                                                                                                |

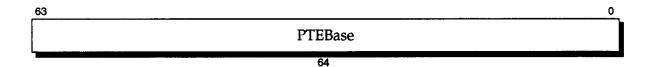

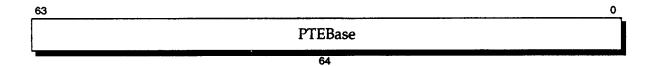

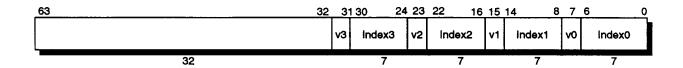

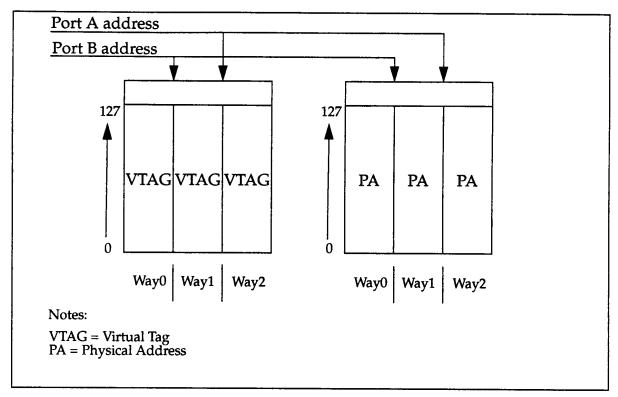

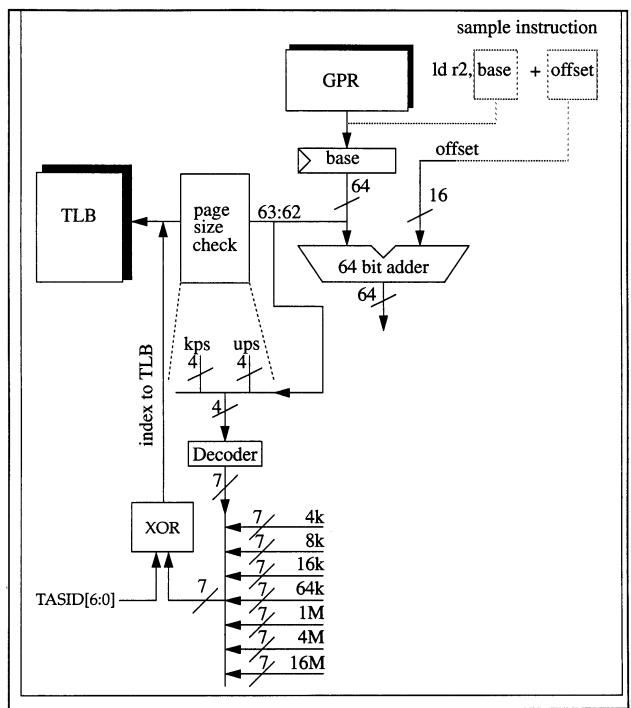

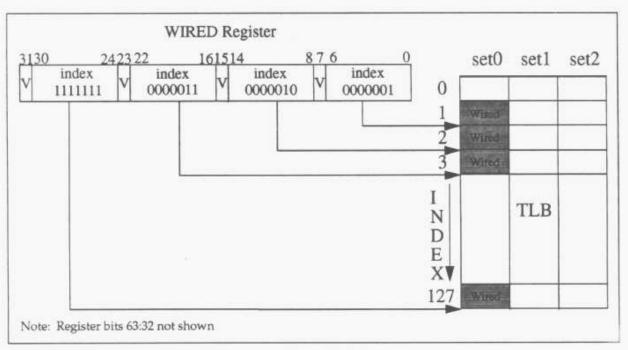

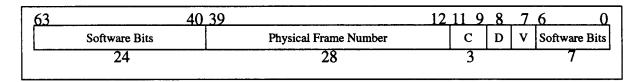

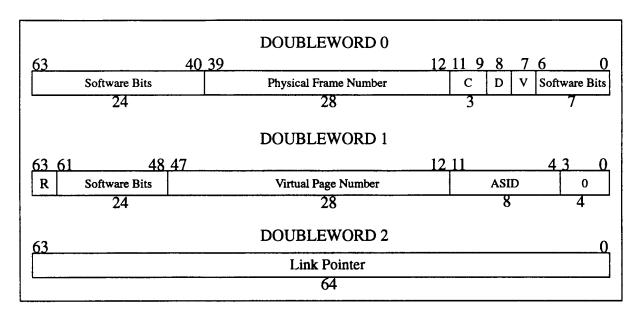

|   | 4.5  | ADD                                                                           | RESS TRANSLATION4-10                                                                                                                                                                                                                                         |

|      | 4.5.1<br>4.5.2                                                                          | Indexing the TLB TLB Writes                                                                                                                                                                                                                                                             | 4-14                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.6  | FORV                                                                                    | •                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.7  |                                                                                         |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 4.7.1                                                                                   | TLB Refill                                                                                                                                                                                                                                                                              | 4-20<br>4-22                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 4.7.3                                                                                   | TLB Modified                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.8  | DAT.                                                                                    | 'A AND CONTROL REGISTERS                                                                                                                                                                                                                                                                | 4-26                                                                                                                                                                                                                                                                                                                                                                                                  |

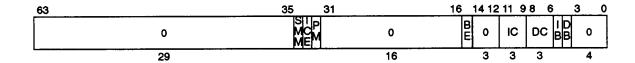

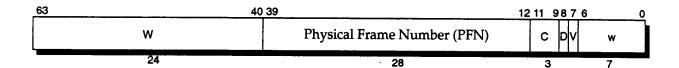

|      | 4.8.1<br>4.8.2<br>4.8.3<br>4.8.4<br>4.8.5<br>4.8.6<br>4.8.7<br>4.8.8<br>4.8.9<br>4.8.10 | TLBSet EntryLo EntryHi UBase PBase ShiftAmt Wired VAddr BadPAddr                                                                                                                                                                                                                        | 4-28<br>4-39<br>4-31<br>4-32<br>4-33<br>4-34<br>4-35                                                                                                                                                                                                                                                                                                                                                  |

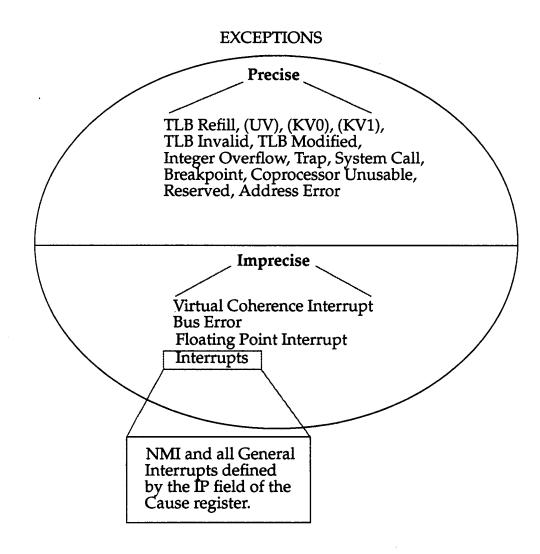

| INTE | RRUPT                                                                                   | S AND EXCEPTIONS                                                                                                                                                                                                                                                                        | 5-1                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |                                                                                         |                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1  | EXC                                                                                     | EPTIONS                                                                                                                                                                                                                                                                                 | 5-2                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1  | EXCI<br>5.1.1                                                                           | Hard Reset                                                                                                                                                                                                                                                                              | 5-3                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1  | 5.1.1<br>5.1.2                                                                          | Hard Reset Non-Maskable Interrupt                                                                                                                                                                                                                                                       | 5-3                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1  | 5.1.1                                                                                   | Hard Reset  Non-Maskable Interrupt  General Exceptions                                                                                                                                                                                                                                  | 5-3<br>5-4                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.1  | 5.1.1<br>5.1.2                                                                          | Hard Reset  Non-Maskable Interrupt  General Exceptions  5.1.3.1 Address Error Exception                                                                                                                                                                                                 | 5-3<br>5-4<br>5-4<br>5-8                                                                                                                                                                                                                                                                                                                                                                              |

| 5.1  | 5.1.1<br>5.1.2                                                                          | Hard Reset  Non-Maskable Interrupt  General Exceptions  5.1.3.1 Address Error Exception  5.1.3.2 System Call Exception                                                                                                                                                                  | 5-3<br>5-4<br>5-4<br>5-8                                                                                                                                                                                                                                                                                                                                                                              |

| 5.1  | 5.1.1<br>5.1.2                                                                          | Hard Reset  Non-Maskable Interrupt  General Exceptions  5.1.3.1 Address Error Exception  5.1.3.2 System Call Exception  5.1.3.3 Breakpoint Exception                                                                                                                                    | 5-3<br>5-4<br>5-8<br>5-8<br>5-8                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1  | 5.1.1<br>5.1.2                                                                          | Hard Reset  Non-Maskable Interrupt  General Exceptions  5.1.3.1 Address Error Exception  5.1.3.2 System Call Exception  5.1.3.3 Breakpoint Exception  5.1.3.4 Reserved Instruction Exception                                                                                            | 5-35-45-85-85-8                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1  | 5.1.1<br>5.1.2                                                                          | Hard Reset  Non-Maskable Interrupt  General Exceptions  5.1.3.1 Address Error Exception  5.1.3.2 System Call Exception  5.1.3.3 Breakpoint Exception  5.1.3.4 Reserved Instruction Exception  5.1.3.5 Coprocessor Unusable Exception                                                    | 5-35-45-85-85-9                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1  | 5.1.1<br>5.1.2                                                                          | Hard Reset Non-Maskable Interrupt General Exceptions 5.1.3.1 Address Error Exception 5.1.3.2 System Call Exception 5.1.3.3 Breakpoint Exception 5.1.3.4 Reserved Instruction Exception 5.1.3.5 Coprocessor Unusable Exception 5.1.3.6 Integer Overflow Exception 5.1.3.7 Trap Exception |                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1  | 5.1.1<br>5.1.2<br>5.1.3                                                                 | Hard Reset                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1  | 5.1.1<br>5.1.2<br>5.1.3                                                                 | Hard Reset Non-Maskable Interrupt                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.1.1<br>5.1.2<br>5.1.3                                                                 | Hard Reset Non-Maskable Interrupt                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                       |

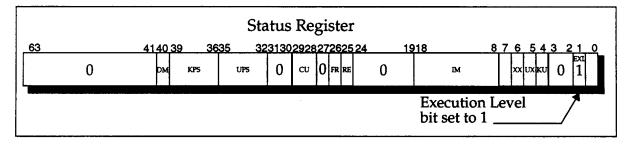

| 5.2  | 5.1.1<br>5.1.2<br>5.1.3                                                                 | Hard Reset Non-Maskable Interrupt                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>INTE<br>INTE<br>5.3.1<br>5.3.2                               | Hard Reset Non-Maskable Interrupt                                                                                                                                                                                                                                                       | 5-35-45-85-85-95-95-105-105-115-11                                                                                                                                                                                                                                                                                                                                                                    |

| 5.2  | 5.1.1<br>5.1.2<br>5.1.3<br>INTE<br>INTE<br>5.3.1                                        | Hard Reset Non-Maskable Interrupt                                                                                                                                                                                                                                                       | 5-35-45-85-85-95-95-105-115-115-12                                                                                                                                                                                                                                                                                                                                                                    |

|      | 4.8                                                                                     | 4.6 FOR<br>4.7 TLB<br>4.7.1<br>4.7.2<br>4.7.3<br>4.8 DAT<br>4.8.1<br>4.8.2<br>4.8.3<br>4.8.4<br>4.8.5<br>4.8.6<br>4.8.7<br>4.8.8<br>4.8.9<br>4.8.10                                                                                                                                     | 4.5.2 TLB Writes  4.5.2.1 Wiring Down TLB Entries  4.6 FORWARD AND REVERSE MAPPING  4.7 TLB EXCEPTIONS  4.7.1 TLB Refill  4.7.1.1 TLB Refill: Forward Mapping Table  4.7.1.2 TLB Refill: Reverse Mapping Table  4.7.2 TLB Invalid  4.7.3 TLB Modified  4.8 DATA AND CONTROL REGISTERS  4.8.1 TLBSet  4.8.2 EntryLo  4.8.3 EntryHi  4.8.4 UBase  4.8.5 PBase  4.8.6 GBase  4.8.7 ShiftAmt  4.8.8 Wired |

|   | INITI   | ALIZATION INTERFACE6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

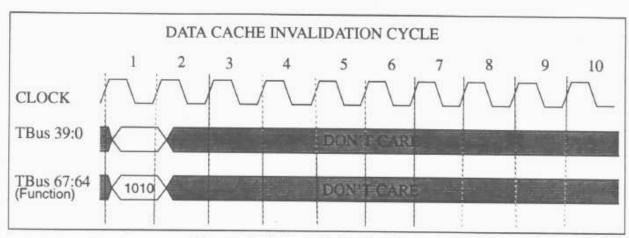

|   | 6.1     | Instruction and Data Cache Invalidation 6-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 6.2     | Flushing the Store Address Queue6-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 6.3     | Tag RAM State Invalidation 6-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 6.4     | Initializing the TLB6-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 6.5     | R8000 Microprocessor Functional Characteristics 6-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 6.6     | Initialization Code Examples6-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7 | CLO     | CK INTERFACES7-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

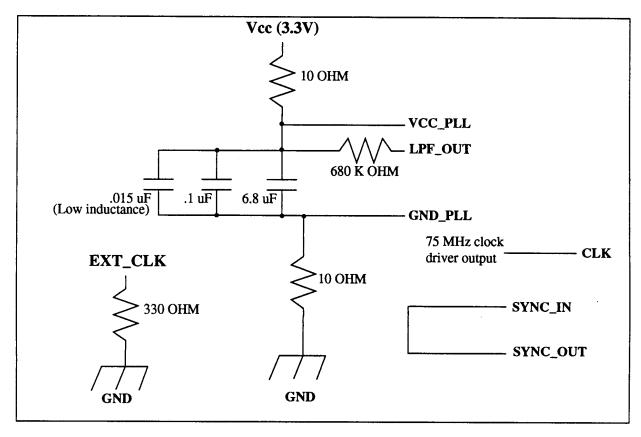

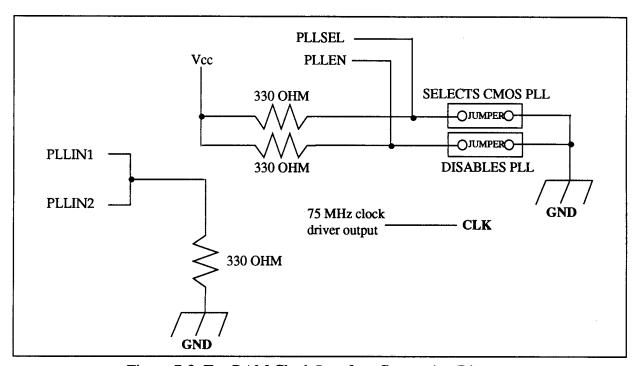

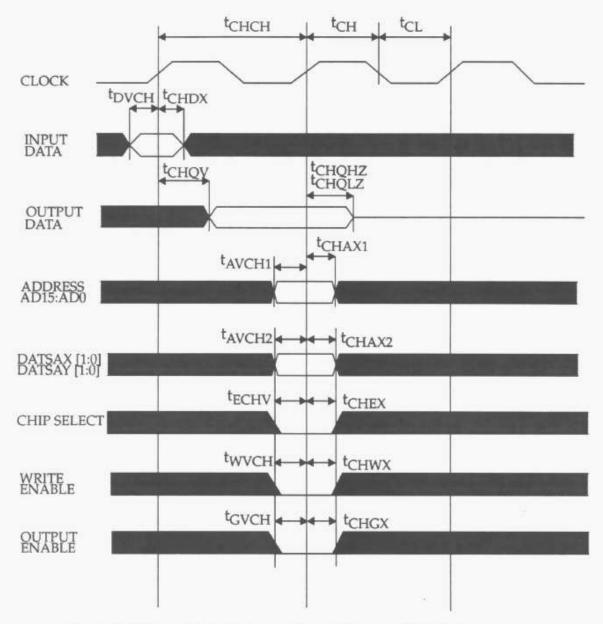

|   | 7.1     | R8000/R8010 CLOCK INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 7.2     | TAG RAM CLOCK INTERFACE7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

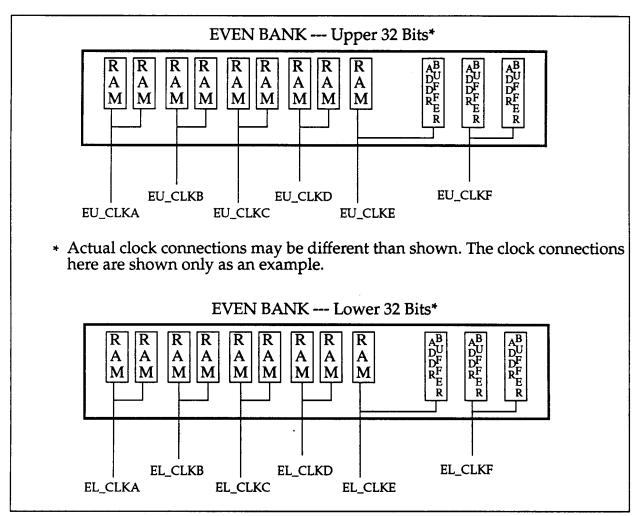

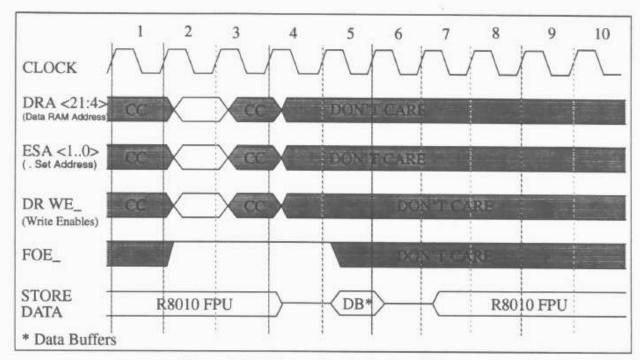

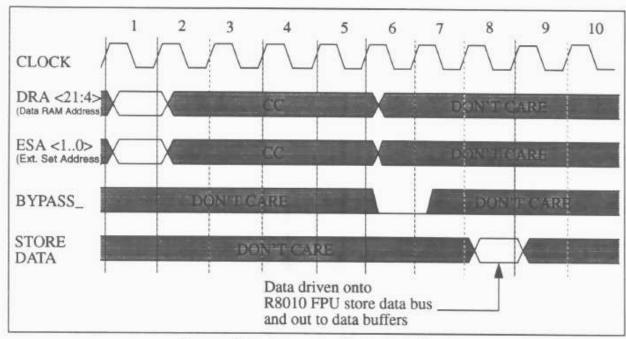

|   | 7.3     | STREAMING CACHE CLOCK INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

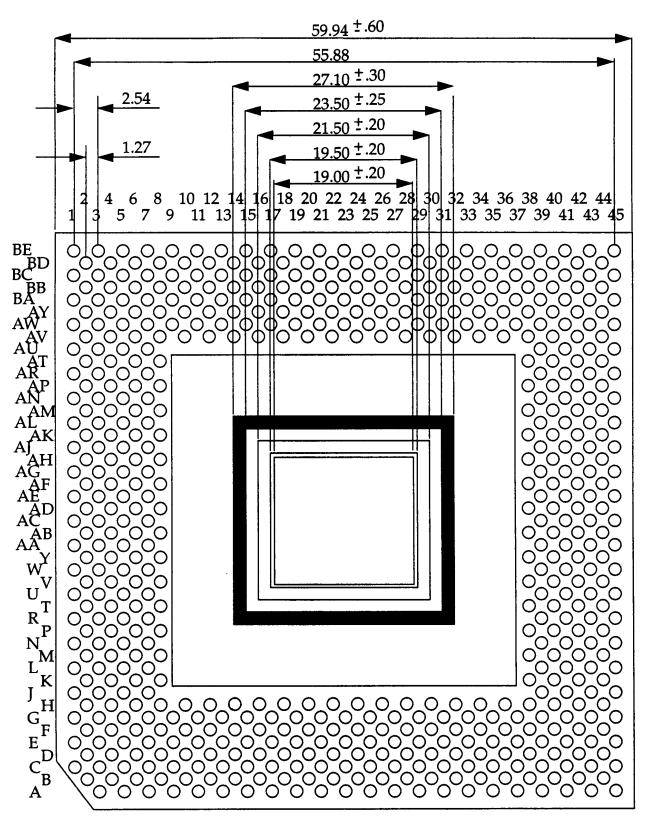

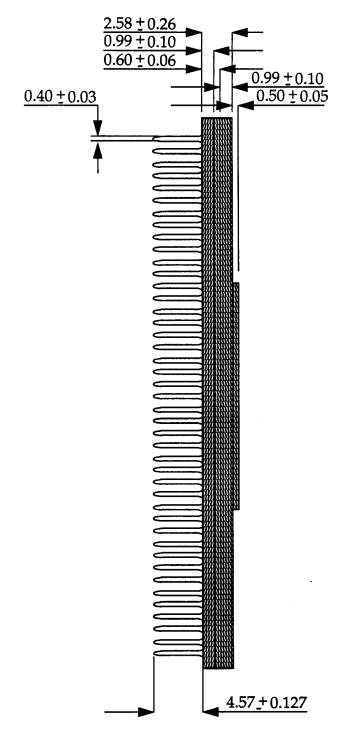

| 8 | ELEC    | TRICAL SPECIFICATIONS AND MECHANICAL DATA8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 8.1     | ELECTRICAL SPECIFICATIONS8-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |         | 8.1.1 R8000 Microprocessor/R8010 FPU 8-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |         | 8.1.2 TAG RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

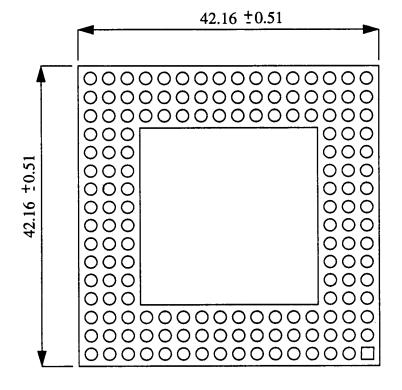

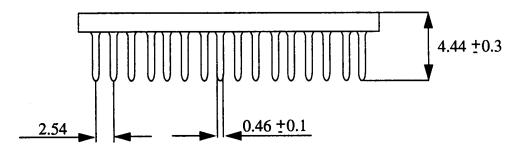

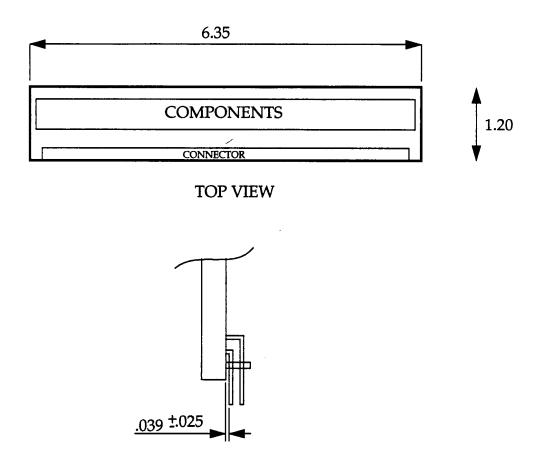

|   | 8.2     | MECHANICAL DATA8-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| _ |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9 | HAR     | DWARE INTERFACE9-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9 | HAR 9.1 | DWARE INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

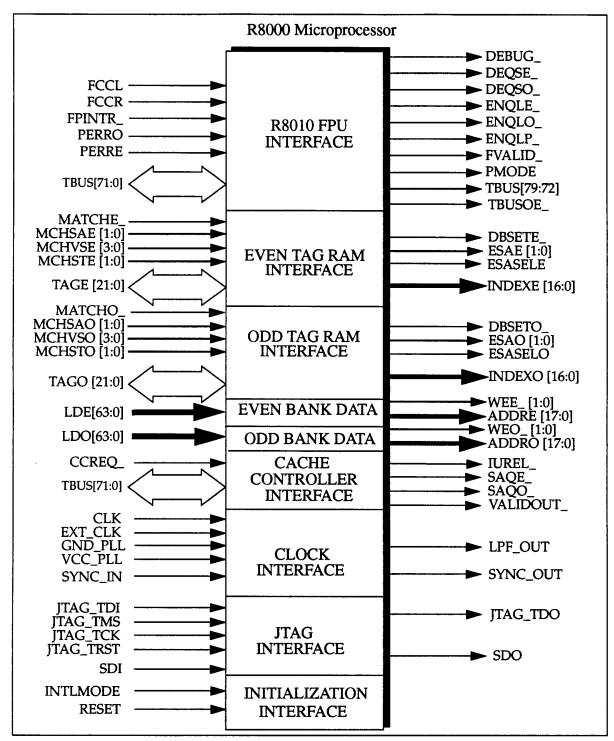

| 9 |         | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

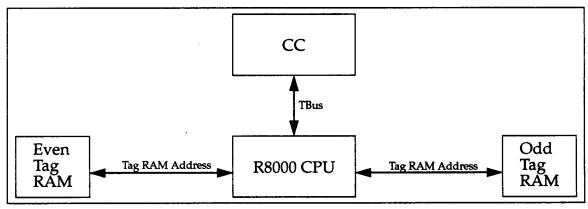

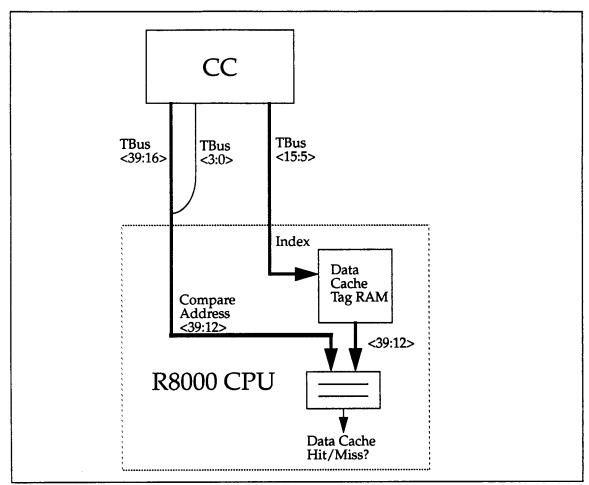

| 9 |         | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS9-3 9.1.1 R8000 Microprocessor to R8010 FPU Interface9-6 9.1.2 R8000 Microprocessor to Even Tag RAM9-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9 |         | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

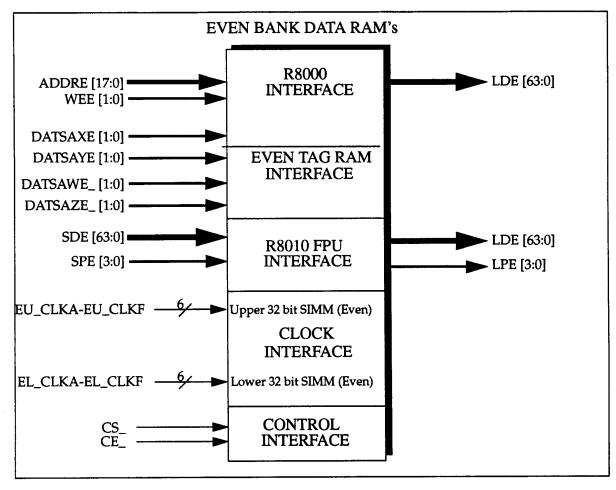

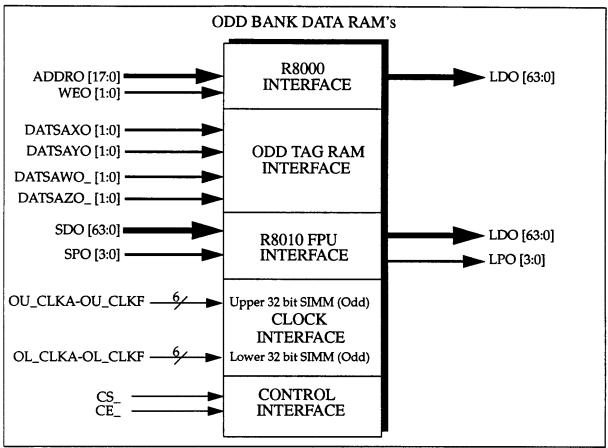

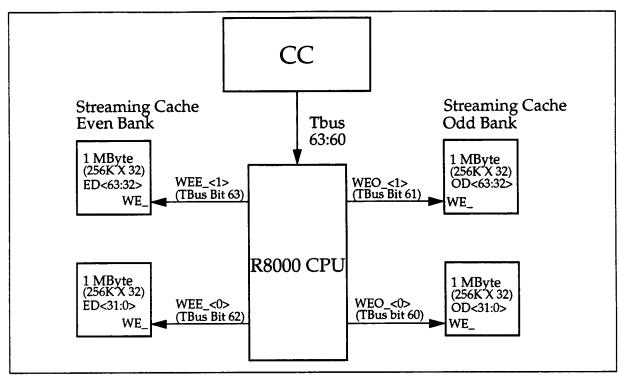

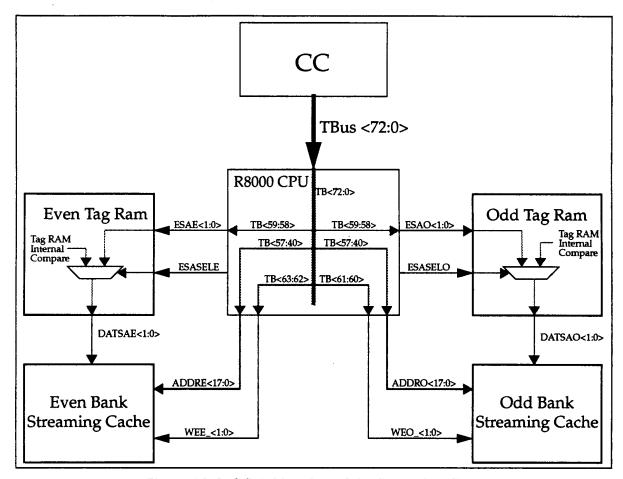

| 9 |         | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS9-3  9.1.1 R8000 Microprocessor to R8010 FPU Interface9-6  9.1.2 R8000 Microprocessor to Even Tag RAM9-9  9.1.3 R8000 Microprocessor to Odd Tag RAM9-12  9.1.4 R8000 Microprocessor to Even Bank Streaming Cache9-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9 |         | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9 |         | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS9-3  9.1.1 R8000 Microprocessor to R8010 FPU Interface9-6  9.1.2 R8000 Microprocessor to Even Tag RAM9-9  9.1.3 R8000 Microprocessor to Odd Tag RAM9-12  9.1.4 R8000 Microprocessor to Even Bank Streaming Cache9-15  9.1.5 R8000 Microprocessor to Odd Bank Streaming Cache9-15  9.1.6 R8000 Microprocessor to Cache Controller9-16  9.1.7 Clock Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9 |         | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9 |         | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9 |         | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9 | 9.1     | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9 | 9.1     | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

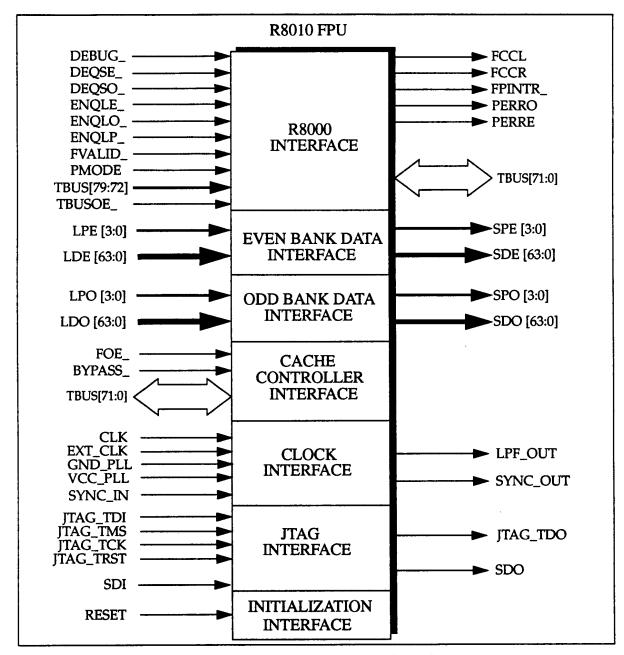

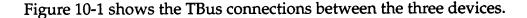

| 9 | 9.1     | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS       9-3         9.1.1 R8000 Microprocessor to R8010 FPU Interface       9-6         9.1.2 R8000 Microprocessor to Even Tag RAM       9-9         9.1.3 R8000 Microprocessor to Odd Tag RAM       9-12         9.1.4 R8000 Microprocessor to Even Bank Streaming Cache       9-15         9.1.5 R8000 Microprocessor to Odd Bank Streaming Cache       9-15         9.1.6 R8000 Microprocessor to Cache Controller       9-16         9.1.7 Clock Interface Signals       9-18         9.1.8 JTAG Interface Signals       9-19         9.1.9 Initialization Interface       9-21         R8010 FPU SIGNAL DESCRIPTIONS       9-22         9.2.1 R8010 FPU to R8000 Microprocessor       9-25         9.2.2 R8010 FPU to Even Bank Streaming Cache       9-28         9.2.3 R8010 FPU to Odd Bank Streaming Cache       9-29                                                        |

| 9 | 9.1     | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS       9-3         9.1.1 R8000 Microprocessor to R8010 FPU Interface       9-6         9.1.2 R8000 Microprocessor to Even Tag RAM       9-9         9.1.3 R8000 Microprocessor to Odd Tag RAM       9-12         9.1.4 R8000 Microprocessor to Even Bank Streaming Cache       9-15         9.1.5 R8000 Microprocessor to Odd Bank Streaming Cache       9-15         9.1.6 R8000 Microprocessor to Cache Controller       9-16         9.1.7 Clock Interface Signals       9-18         9.1.8 JTAG Interface Signals       9-19         9.1.9 Initialization Interface       9-21         R8010 FPU SIGNAL DESCRIPTIONS       9-22         9.2.1 R8010 FPU to R8000 Microprocessor       9-25         9.2.2 R8010 FPU to Even Bank Streaming Cache       9-28         9.2.3 R8010 FPU to Odd Bank Streaming Cache       9-29         9.2.4 R8010 FPU to Cache Controller       9-31 |

| 9 | 9.1     | R8000 MICROPROCESSOR SIGNAL DESCRIPTIONS       9-3         9.1.1 R8000 Microprocessor to R8010 FPU Interface       9-6         9.1.2 R8000 Microprocessor to Even Tag RAM       9-9         9.1.3 R8000 Microprocessor to Odd Tag RAM       9-12         9.1.4 R8000 Microprocessor to Even Bank Streaming Cache       9-15         9.1.5 R8000 Microprocessor to Odd Bank Streaming Cache       9-15         9.1.6 R8000 Microprocessor to Cache Controller       9-16         9.1.7 Clock Interface Signals       9-18         9.1.8 JTAG Interface Signals       9-19         9.1.9 Initialization Interface       9-21         R8010 FPU SIGNAL DESCRIPTIONS       9-22         9.2.1 R8010 FPU to R8000 Microprocessor       9-25         9.2.2 R8010 FPU to Even Bank Streaming Cache       9-28         9.2.3 R8010 FPU to Odd Bank Streaming Cache       9-29                                                        |

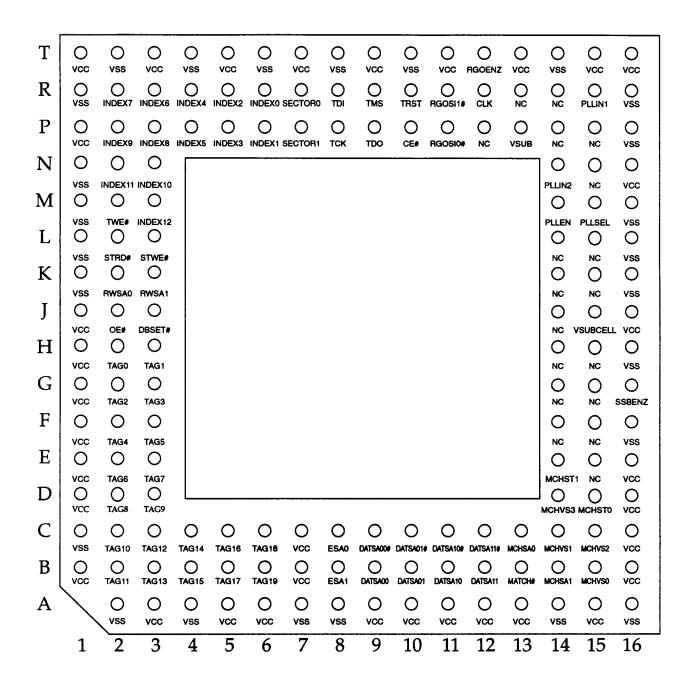

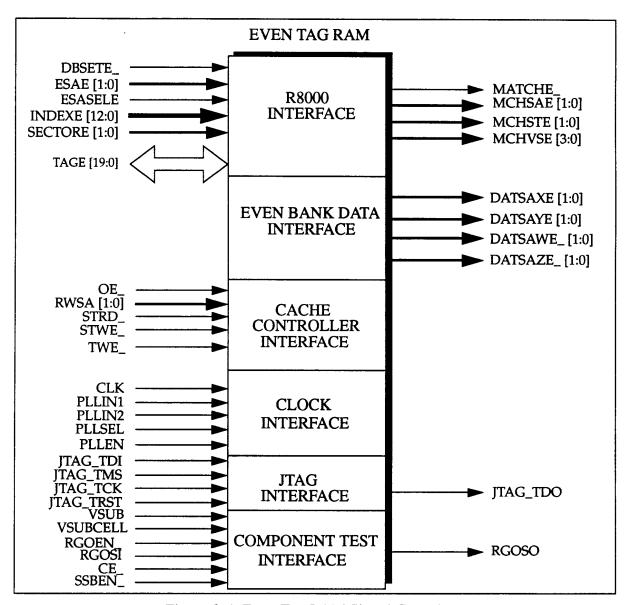

| 9.3     | EVEN                                                                                   | N TAG RAM UNIT SIGNAL DESCRIPTIONS                                                                                                                                                                                  | 9-33                                           |

|---------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

|         | 9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6                                     | Even Tag RAM to R8000 Microprocessor  Even Tag RAM to Even Bank Streaming Cache  Tag RAM to Cache Controller  Tag RAM Clock Interface  JTAG Interface  Component Test Interface                                     | 9-37<br>9-38<br>9-39<br>9-40                   |

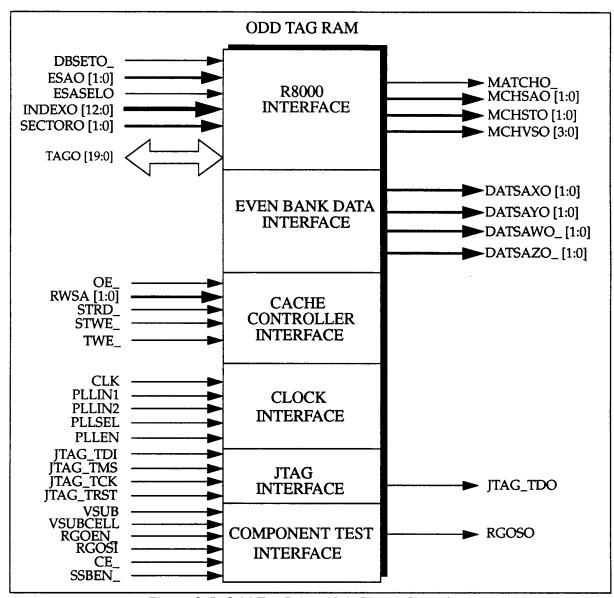

| 9.4     | ODD                                                                                    | TAG RAM UNIT SIGNAL DESCRIPTIONS                                                                                                                                                                                    | 9-41                                           |

|         | 9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.6                                     | Odd Tag RAM to R8000 Microprocessor                                                                                                                                                                                 | 9-45<br>9-46<br>9-46<br>9-47                   |