This section covers the control registers of the Coherency Manager

# **Global Configuration Registers**

#### Global Configuration Registers (GCR)

- A set of memory-mapped controller registers that are used to configure and control various aspects of the coherence scheme and Coherence Manager.

- Provides information on system configuration

- Configure address map locations of the Global Interrupt Controller and Cluster power controller.

- Configure the non coherent areas of memory to either real memory or I/O devices.

- Control the coherency of the default shared memory region.

- Controls the handling and reporting of coherency manager errors.

- Controls other options of the Coherency manager

The Global Configuration Registers referred to as GCR, are the system programmers interface to the Coherency manager. The location of these register in the memory map is determined at core build time.

+ The GCRs are used to set the addresses for the Global Interrupt Controller and Cluster power controller.

+ They can configure the non coherent areas of memory to either real memory or I/O devices.

+ Control the coherency of the default shared memory region.

- + Controls the handling and reporting of coherency manager errors.

- + and any other options of the Coherency manager

2

## **Global Configuration Registers**

#### GCR - Memory Mapped Registers

- Control and Status registers

- Total size of 32 Kbytes, divided into 8 KByte (0x2000) blocks

| GCR Base Offset | Description<br>Global Control Block. Contains registers pertaining to the global system<br>functionality.                                                                                                                                                                                                          |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x2000 - 0x3FFF | Core-Local Control Block (aliased for each CPU core). Contains registers pertaining to the core issuing the request. Each CPU has its own copy of registers within this block.                                                                                                                                     |

| 0x4000 - 0x5FFF | Core-Other Control Block (aliased for each CPU core). This<br>block of addresses gives each Core a window into another CPU's Core-<br>Local Control Block. Before accessing this space, the Core-<br>Other_Addressing Register in the Core Local Control Block must be<br>set with the CORENum of the target Core. |

| 0x6000 - 0x7FFF | Global Debug Block. Contains global registers useful in debugging the MPS.                                                                                                                                                                                                                                         |

The Global Control Registers are memory mapped registers located in the system's address space. The GCR space contains control and status registers for the entire Coherent Processing System cluster and for the individual CPUs in the cluster.

+ All registers in the Global Control Block are 32 bits wide and should only be accessed using 32-bit uncached loads and stores. Reads from unpopulated registers in the GCR address space return 0x0, and writes to those locations are silently dropped without generating any exceptions.

+ The GCR address space has a total size of 32 Kbytes, which is divided into 8 Kbyte blocks

+ The first block is a global control block. This is a system wide block that cover all the global aspects of the Coherent Processing System.

Some configuration values are on a per core basis so each core has a set of registers that pertain to these local configuration items. This set of registers is called the Core-Local control block. The address range for this block is the same for all cores relative to the local core performing the ld or store to a register in this block.

A core can access another core's local registers by using the Core-Other Control Block. That way one core can read the status or change the configuration of another core. The address range for this block is also the same for all cores relative to the local core performing the ld or store to a register in this block. The selection of which cores registers will be accessed in this block will be covered later.

The Global Debug Block is system wide block. It used for debugging purposes and Performance information. The Debug Block is covered in upcoming sections.

| Location                                                                                                             | Location of the GCR address space     |                                                                                                                                                                                                                                                                                                                                                                                                        |             |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| Register Fields                                                                                                      |                                       | CMGCR Base Register<br>(CP0 Register 15, Select 3)                                                                                                                                                                                                                                                                                                                                                     | Reset State |  |  |  |

| Name                                                                                                                 | Bits                                  | (CPU Register 15, Select 5)                                                                                                                                                                                                                                                                                                                                                                            |             |  |  |  |

| CMGCR_<br>BASE_ADDR                                                                                                  | 31:11                                 | Bits 31:11 of the base physical address of the memory mapped<br>Coherency Manager GCR registers.<br>This register field reflects the value of the GCR_BASE field within the<br>memory-mapped Coherency Manager GCR Base Register.<br>The number of implemented physical address bits is implementation-<br>specific. For the unimplemented address bits - writes are ignored,<br>returns zero on read. | Preset      |  |  |  |

| #define C0_CMG<br>#define getcmgc<br>({ unsigned int _<br>asmvolat<br>value;})<br>unsigned int x;<br>x = getcmgcrg() | erg() \<br>_value; \<br>tile ("mfc0 % | %0, \$%1, 0" : "=d" (value) : "i" (C0_CMGCR)); \                                                                                                                                                                                                                                                                                                                                                       |             |  |  |  |

| MIPS                                                                                                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                        | 4           |  |  |  |

The memory mapped address for the base of the Global Configuration Registers can be found by reading CP0 register 15 select 3.

+ Here are the macros that will allow you to access the register from a c program.

+ Here is an example of calling the macro from C

| Register Fields            |       |                                                                              | Global Config Register                                    |                                                              |                  |

|----------------------------|-------|------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|------------------|

| Name                       | Bits  |                                                                              | (GCR_CONFIG Offset 0x0000)                                |                                                              |                  |

| NUM_ADDR_ 19:16<br>REGIONS | 19:16 | Total number of CN currently supported                                       | Address Regions. Note: only 0, 4,or 6 Address Regions are | IP Configuration<br>Value                                    |                  |

|                            |       | Encoding                                                                     | Meaning                                                   |                                                              |                  |

|                            |       | 0x0                                                                          | 0 Address Regions                                         |                                                              |                  |

|                            |       | 0x1                                                                          | 1 Address Regions                                         |                                                              |                  |

| NUMIOCU                    | 11:8  | DCU 11:8 Total number of IOCUs in the system. Note: 0 - 2 IOCU are currently |                                                           | CUs in the system. Note: 0 - 2 IOCU are currently supported. | IP Configuration |

|                            |       | Encoding                                                                     | Meaning                                                   | Value                                                        |                  |

|                            |       | 0x0                                                                          | 0 IOCU                                                    |                                                              |                  |

|                            |       | 0x1                                                                          | 1 IOCU                                                    |                                                              |                  |

|                            |       | 0x2                                                                          | 2 IOCUs                                                   |                                                              |                  |

| PCORES                     | 7:0   | Total number of Co                                                           | res in the system not including the IOCUs.                | IP Configuration                                             |                  |

|                            |       | Encoding                                                                     | Meaning                                                   | Value                                                        |                  |

|                            |       | 0x0                                                                          | 1 core                                                    |                                                              |                  |

|                            |       | 0x1                                                                          | 2 cores                                                   |                                                              |                  |

The first register in the Global block section is the global configuration register. This register is a read-only register the gives you information on the configuration of the Coherency Manager in your system.

NUM\_ADDR\_REGIONS is the number of Address Regions. This tells you how many regions you can configure to support different coherency policies. You would use regions, for example, to configure an area of memory to be used for memory mapped I/O or to change the coherency of the region between the I2 cache controller and real memory. I'll talk more about regions later in this section.

NUMIOCU Total number of I/O Control Units in the system. Our cores support either none or up to 2 at this time.

PCORES tells you the number of cores in the Coherent Processing System.

| GCR Base        | SCR Base Register Offset |                                                                                                                                                                               |       |  |  |

|-----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|

| Register Fields |                          | GCR Base Register                                                                                                                                                             | Reset |  |  |

| Name            | Bits                     | (GCR_BASE Offset 0x0008)                                                                                                                                                      | State |  |  |

| GCR_BASE        | 31:15                    | This field sets the base address of the 32KB GCR block of the CPS.<br>This register has a fixed value after reset if configured as Read-Only (an IP<br>Configuration Option). | IP    |  |  |

|                 |                          |                                                                                                                                                                               |       |  |  |

|                 |                          |                                                                                                                                                                               |       |  |  |

|                 |                          |                                                                                                                                                                               |       |  |  |

|                 |                          |                                                                                                                                                                               |       |  |  |

|                 |                          |                                                                                                                                                                               |       |  |  |

|                 |                          |                                                                                                                                                                               |       |  |  |

|                 |                          |                                                                                                                                                                               |       |  |  |

|                 |                          |                                                                                                                                                                               |       |  |  |

The GCR Base register lets you configure the GCR base address and Coherency attributes under certain conditions. In most cases this value is read only value having been configured as a IP option when the core was built.

| Register Fields                 |      |                                                                                                        |                                         | ase Register                                                                           | Rese  |

|---------------------------------|------|--------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------|-------|

| Name                            | Bits | (                                                                                                      | GCR_BAS                                 | E Offset 0x0008)                                                                       | State |

| CCA_DEFAULT_<br>OVERRIDE_VALUE  | 7-5  |                                                                                                        | CCA) value fo                           | RIDE_ENABLE to force the Cache<br>or transactions on the L2/Memory OCP.<br>ABLE field. | 0     |

|                                 |      | Encoding                                                                                               | Name                                    | Description                                                                            |       |

|                                 |      | 0x0                                                                                                    | WT                                      | Write Through                                                                          |       |

|                                 |      | 0x2                                                                                                    | UC                                      | Uncached                                                                               |       |

|                                 |      | 0x3                                                                                                    | WB                                      | Write Back non-coherent                                                                |       |

|                                 |      | 0x4                                                                                                    | CWBE                                    | Mapped to WB                                                                           |       |

|                                 |      | 0x5                                                                                                    | CWB                                     | Mapped to WB                                                                           |       |

|                                 |      | 0x7                                                                                                    | UCA                                     | Uncached Accelerated                                                                   |       |

| CCA_DEFAULT_<br>OVERRIDE_ENABLE | 4    | If CCA_DEFAULT_O<br>and CM_DEFAULT_T<br>transactions with add<br>value set to CCA_DE<br>OVERRIDE_VALUE | ARGET is se<br>resses that do<br>FAULT_ | et to Memory, then<br>o not map to any region will have a CCA                          | 0     |

Default Address Region. For the default Address Region there is one configuration register that determines if the Cache coherency attribute default override is enable, the CCA if the override is enabled and the memory port that is associated with the default region.

CCA\_Override\_Value and CCA\_Override\_enable are used in conjunction with CM\_DEFAULT\_TARGET memory region shown in the next slide. As you will understand when I explain CM regions, you can configure each with a starting address and size. The CM\_DEFAULT\_TARGET region covers any memory not already covered by a configurable CM region. If you don't have any configurable regions then this default region will cover all of memory. The CM\_DEFAULT\_TARGET can be set to 2 different types of addresses, addresses that go to memory and addresses that go to the I/O Coherency Unit for memory mapped I/O. Of course if you don't have any other regions in your system this default region should be set to Memory. In a typical system you would use the other regions to map to the IOCU type for memory mapped I/O and this default region to map to a memory type.

The CCA\_DEFAULT\_OVERRIDE\_VALUE controls the cache coherency algorithm between the L2 cache and memory. So If this is set to Write through any writes to the L2 cache will also be written to memory. If set to uncached writes will not be stored in the L2 and go directly to memory. If set to write back all writes will be stored in the cache and only be written to memory if evicted or flushed, Last if set to uncached accelerated writes will not be stored in the L2 but will be gathered in a cache line size buffer before being written to memory.

The CCA\_DEFAULT\_OVERIDE\_ENABLE bit controls the enabling of the default CCA\_DEFAULT\_OVERRIDE\_VALUE if the bit is set the region will use the CCA\_DEFAULT\_OVERRIDE\_VALUE. If it is zero the it will use the same CCA as the L1 cache.

| GCR Bas               | GCR Base Register |                                                             |                                                  |  |  |  |  |

|-----------------------|-------------------|-------------------------------------------------------------|--------------------------------------------------|--|--|--|--|

| Register Fields       |                   | GCR Base Register                                           | Reset State                                      |  |  |  |  |

| Name                  | Bits              | (GCR_BASE)                                                  |                                                  |  |  |  |  |

| CM_DEFAULT_<br>TARGET | 1:0               | Determines the target device for the default memory region. | Value of signal<br>SI_CM_Default_Target<br>[1:0] |  |  |  |  |

|                       |                   | Encoding Meaning                                            |                                                  |  |  |  |  |

|                       |                   | 0 Memory                                                    |                                                  |  |  |  |  |

|                       |                   | 2 1 <sup>st</sup> IOCU                                      |                                                  |  |  |  |  |

|                       |                   | 3 2 <sup>nd</sup> IOCU                                      |                                                  |  |  |  |  |

|                       |                   |                                                             |                                                  |  |  |  |  |

|                       |                   |                                                             | 8                                                |  |  |  |  |

More on the GCR Base register:

The CM\_DEFAULT\_TAGET controls if the region is used for memory or memory mapped IO.

| Register Fields |      | Global CSR Access Privilege Register (GCR_ACCESS Offset                                                                                                                                                                                                                                                                                                                                                                                                                  | Reset |

|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Name            | Bits | 0x0020)                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | State |

| M_<br>CCESS_EN  | 7:0  | Each bit in this field represents a coherent requester.<br>If the bit is set, that requester is able to write to the GCR registers (this includes all<br>registers within the Global, Core-Local, Core-Other, and Global Debug control blocks.<br>The GIC is always writable by all requestors).<br>If the bit is clear, any write request from that requestor to the GCR registers (Global,<br>Core-Local, Core-Other, or Global Debug control blocks) will be dropped. | 0xff  |

|                 |      | ccess to the GCR registers by other CPUs through the u<br>corresponding bit to 1 enables writes to the GCR from t                                                                                                                                                                                                                                                                                                                                                        |       |

On bring up your system CPU 0 can control access to the GCR registers by other CPUs through the use of this field. Each bit represents a processor or VPE in an MT system. Setting the corresponding bit to 1 enables writes to the GCR from that processor. Bits 0 - 3 correspond to Cores 0 - 1. Bits 4 and 5 correspond to IOCU 0 and 1.

| Register Fi | ields | GCR Revision Register                                                                                                                       | Reset  |

|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Name        | Bits  | (GCR_REV Offset 0x0030)                                                                                                                     | State  |

| MAJOR_REV   | 15:8  | This field reflects the major revision of the GCR block. A major revision might reflect the changes from one product generation to another. | Preset |

| MINOR_REV   | 7:0   | This field reflects the minor revision of the GCR block. A minor revision might reflect the changes from one release to another.            | Preset |

|             |       |                                                                                                                                             |        |

|             |       |                                                                                                                                             |        |

The GCR Revision Register is useful when reporting issues to MIPS Technologies.

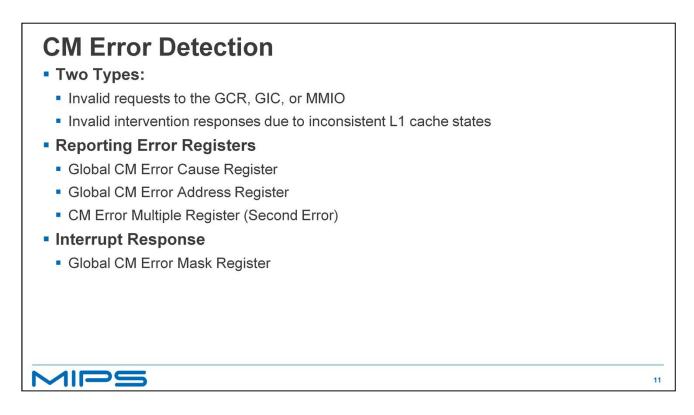

The Coherency Manager can detect,

+ An Invalid request to the GCR, The Global Interrupt Controller or Memory Management I/O controller. These invalid requests are usually caused by trying to access these controllers through something other than uncached accesses.

+ It can also detect an invalid intervention request due to inconsistent L1 cache states caused by improper coherence domain switch or inconsistent Cache Attributes between 2 CPUs for the same cache line.

+ The GIC has several registers

+++ that are use to communicate error conditions which I will cover in detail in upcoming slides.

+ All errors can be configured to cause an interrupt using the CM error mask register.

## **CM Error Detection**

#### Types of errors

- 1 GC\_WR\_ERR or 2 GC\_RD\_ERR

- GIC or GCR register accessed through cache address instead of an uncached address.

- 3 COH\_WR\_ERR or 4 COH\_RD\_ERR

- Coherent read or write error caused by GIC, GCR or MMIO areas accessed with a coherent address (address with a CCA of 4 or 5) instead of an uncached accessed.

- 5 MMIO\_WR\_ERR or 6 MMIO\_RD\_ERR

- Caused by an IOCU device trying to write to Memory Mapped I/O space.

- 17 INTVN\_WR\_ERR or 18 INTVN\_RD\_ERR

- Intervention read or write error caused by the Coherence Domain not properly entered or existed coherence domain or inconsistent CCA value for cache lines in a coherent domain.

- 24 26 L2 Cache Errors

MIPS

There are 8 types of errors;

+ Types 1 and 2 are Global Control register write or read errors that are caused by trying to access the GCR or GIC register space in some way other than with an uncached address with a CCA of 2 causing a read of more than one word.

+ Types 3 and 4 are Coherent write or read errors that are caused by trying to access the GCR, GIC or MMIO with a coherent memory address (address with a CCA of 4 or 5).

+ Types 5 and 6 Memory mapped I/O read or write are caused by an I/O device trying to write to Memory Mapped I/O space. This could happen if an IO device is accessing itself or another IO device, by using the Coherency Manager.

+ types 17 and 18 are intervention read or write errors that can happen if the SW didn't follow the proper procedure for going into or out of the coherence domain. For example, if the Data Cache was not flushed when going from non-coherent to coherent, then it's possible for different cores to have incompatible states for the same line. Also, the cores could have different mappings for the same line, and this could lead to an error if one core mapped the line as coherent and the other mapped it as non-coherent.

+ types 24 – 26 are L2 cache errors. To accommodate L2 cache sizes greater than 1MB, when the index field is too small in the CP0 CacheErr register to hold all index tags, the information is captured in the CM2 Error GCRs. The previous CP0 CacheErr functionality is preserved for L2 cache sizes of 1MB and less.

12

| Global CM Error Mask Register |      |                                                                                                                                                                                                                                                                               |                                                                                                                                              |  |  |  |

|-------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Register Fields               |      | Global CM Error Mask Register<br>(GCR ERROR MASK Offset 0x0040)                                                                                                                                                                                                               | Reset State                                                                                                                                  |  |  |  |

| Name                          | Bits |                                                                                                                                                                                                                                                                               |                                                                                                                                              |  |  |  |

| CM_<br>ERROR_MASK             | 31:0 | Each bit in this field represents an Error Type. If the bit<br>is set, an interrupt is generated if an error of that type is<br>detected.<br>If the bit is set, the transaction for Read-Type Errors<br>completes with OK response to avoid double reporting<br>of the error. | 0x000A_002A<br>This enables error<br>numbers 2, 4, 5, 17, 19<br>(write errors cause<br>interrupts;<br>read errors provide<br>error response) |  |  |  |

|                               | 5    |                                                                                                                                                                                                                                                                               |                                                                                                                                              |  |  |  |

Each bit in the GCR Global CM Mask Register enables an interrupt for the corresponding interrupt type. The default interrupt mask is set to interrupt on write requests and intervention errors.

The interrupt asserts the SI\_CM\_Err signal. It is recommended that this signal be connected to SI\_Cmint 0 of the GIC. The GIC section of this course will go into how the GIC is setup to do that.

If the bit is 0 the error will signal a Bus Error exception for a data access. The next slide tells you how to break it down to the exact eror.

BTW there is a typo in the default value. It sets bit 19 but there is no error type 19!

| Global CM Error Cause Register |       |                                                                                                                                                                                                                      |             |  |

|--------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| Register Fields                |       |                                                                                                                                                                                                                      | Reset State |  |

| Name                           | Bits  | Offset 0x0048)                                                                                                                                                                                                       |             |  |

| CM_<br>ERROR_TYPE              | 31:27 | Indicates type of error detected. When CM_ERROR_TYPE is zero, no errors have been detected. When CM_ERROR_TYPE is non-zero, another error will not be reloaded until a power-on reset or this field is written to 0. | 0           |  |

| CM_ERROR_<br>INFO              | 26:0  | Information about the error. See next slide.                                                                                                                                                                         | Undefined   |  |

| -0                             |       |                                                                                                                                                                                                                      |             |  |

|                                |       |                                                                                                                                                                                                                      |             |  |

|                                |       |                                                                                                                                                                                                                      |             |  |

|                                |       |                                                                                                                                                                                                                      |             |  |

| VIPS                           |       |                                                                                                                                                                                                                      | 1           |  |

For either a Bus error exception or an interrupt the Global CM Error Cause Register will give you more information on the error. This register must be cleared after the exception or interrupt is handled.

One of the 8 error types given in a previous slide will be set in the cm error type field.

The cm error info gives you information on the error formatted based on the error type. The tables in the next slides will show you how to map the errors.

| Glo     | Global CM Error Cause Register Error Types 1 - 6 |      |                              |  |  |  |

|---------|--------------------------------------------------|------|------------------------------|--|--|--|

| 22      | ormat for types 1 – 6 MCmd Description           |      | Description                  |  |  |  |

| (M      | (Memory Access Errors)                           |      | Legacy Write                 |  |  |  |

| Bits    | Description                                      | 0x02 | Legacy Read                  |  |  |  |

| 17:15   | CCA                                              | 0x08 | Coherent Read Own            |  |  |  |

| 17.15   | CCA                                              | 0x09 | Coherent Read Share          |  |  |  |

| 14:12   | Target Region (0: mem, 1:gcr, 2:                 | 0x0A | Coherent Read Discard        |  |  |  |

|         | gic,                                             | 0x0B | Coherent Ready Share Always  |  |  |  |

|         | 3:mmio, 5:cpc)                                   | 0x0C | Coherent Upgrade             |  |  |  |

| 11:7    | OCP MCmd                                         | 0x0D | Coherent Writeback           |  |  |  |

| 6:3     | Source TagID                                     | 0x10 | Coherent Copyback            |  |  |  |

| 2:0     | Source port                                      | 0x11 | Coherent Copyback Invalidate |  |  |  |

|         |                                                  | 0x12 | Coherent Invalidate          |  |  |  |

|         |                                                  | 0x13 | Coherent Write Invalidate    |  |  |  |

| <u></u> |                                                  | 0x14 | Coherent Completion Sync     |  |  |  |

|         | 75                                               |      | 15                           |  |  |  |

There are 2 formats for the CM Error Info.

Here is the format for CM Error Types 1-6.

+Here is the meaning of the OCP MCmd:

| For   | nat for types 17 – 18 (Intervention Error | 5)           |            |

|-------|-------------------------------------------|--------------|------------|

| Bits  | Description                               |              |            |

| 20:19 | Coherent state from core 3                | Cohe         | rent state |

| 18    | Intervention SResp from core 3            | Encoding     | Meaning    |

| 17:16 | Coherent state from core 2                | 0            | Invalid    |

| 15    | Intervention SResp from core 2            | 1            | Shared     |

| 14:13 | Coherent state from core 1                | 2            | Modified   |

| 12    | Intervention SResp from core 1            | 3            | Exclusive  |

| 11:10 | Coherent state from core 0                |              |            |

| 9     | Intervention SResp from core 0            | Intervention | SResp      |

| 8     | Request was from a Store Conditional      | Encoding     | Meaning    |

| 7:3   | OCP MCmd                                  | 0            | OK         |

| 2:0   | Source port                               | 1            | Data (DVA) |

Here are the cm error info values for error types 16 through 31.

+Here is the encoding for the Coherent state errors

+ and here is the encoding for the intervention response errors

|       | Format for types 24 – 26 (L2 Errors)                                                                                                                     |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | For CM Error types 24 – 26 (L2 Errors)                                                                                                                   |

| Bits  | Description                                                                                                                                              |

| 23    | Multiple Uncorrectable                                                                                                                                   |

| 22:18 | Instruction [4:0] associated with the error                                                                                                              |

| 17:16 | Array type[1:0]:<br>00 = None<br>01 = Tag RAM single/double ECC error<br>10 = Data RAM single/double ECC error<br>11 = WS RAM uncorrectable dirty parity |

| 15:12 | DWord[3:0] with error, Array type=2 only                                                                                                                 |

| 11:9  | Way[2:0] associated with the error                                                                                                                       |

| 8     | Multi-way error for Tag or WS RAM                                                                                                                        |

| 7:0   | Syndrome associated with Tag or WS way, or Syndrome associated with Data Dword                                                                           |

Here are the encodings for the L2 error information.

| Hex codes for action that caused the L2 cache error |                |      |                 |  |

|-----------------------------------------------------|----------------|------|-----------------|--|

| de                                                  | Description    | Bits | Description     |  |

| 0                                                   | L2_NOP         | 0D   | L2_SYNC         |  |

|                                                     | L2_ERR_CORR    | 0E   | L2_REFL_ERR     |  |

|                                                     | L2_TAG_INV     | 10   | L2_INDX_WB_INV  |  |

|                                                     | L2_WS_CLEAN    | 11   | L2_INDX_LD_TAG  |  |

|                                                     | L2_RD_MDYFY_WR | 12   | L2_INDX_ST_TAG  |  |

|                                                     | L2_WS_MRU      | 13   | L2_INDX_ST_DATA |  |

|                                                     | L2_EVICT_LN2   | 14   | L2_INDX_ST_ECC  |  |

|                                                     | L2_EVICT       | 18   | L2_FTCH_AND_LCK |  |

|                                                     | L2_REFL        | 19   | L2_HIT_INV      |  |

|                                                     | L2_RD          | 1A   | L2_HIT_WB_INV   |  |

|                                                     | L2_WR          | 18   | L2 HIT WB       |  |

|                                                     | L2_EVICT_MRU   |      |                 |  |

Here are the codes for the actions that caused the L2 error.

| Register Fields  |      | 🗌 - Second and a second s | eset State |  |

|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|

| Name             | Bits | Offset 0x0050)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |  |

| CM_ERROR_ADDR    | 31:0 | Request address which caused error. Loaded when the Global Error Cause<br>Register is loaded.<br>Bits 2:0 should always be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Undefined  |  |

| Register Fi      | elds | Global CM Error Multiple Register (GCR_ERROR_MULT Offse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |  |

| Name             | Bits | 0x0058)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | State      |  |

| CM_ERROR_<br>2ND | 4:0  | Type of second error. Loaded when the Global CM Error Cause Register has valid er<br>information and a second error is detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ror 0      |  |

The Global CM error address register contains the address which caused the error. It should be cleared after the exception or interrupt is handled.

The Global CM Error Multiple Register gives the type of error if a second error is detected before the first one is handled. It must be cleared after the exception or interrupt has been handled.

| Global (    |      | ustom Status Register                                     |             |

|-------------|------|-----------------------------------------------------------|-------------|

| Register Fi | elds | Custom Status Register (GCR_CUSTOM_STATUS Offset          | Reset State |

| Name        | Bits | 0x0068)                                                   |             |

| GGU_EX      | 0    | If this bit is set, the Custom GCRs connected to the CM2. | 1           |

|             |      |                                                           |             |

|             | 5    |                                                           | 20          |

The CM2 provides the capability of including custom (user-defined) GCRs. GGU\_EX indicates if the customer GCR registers exist or not.

The GCR\_CUSTOM\_BASE register sets the physical address of the base address of a 64KByte slice of memory space, where requests are directed to the Custom GCRs.

GGU\_EN enables the redirection of the memory request to the custom CGR memory registers instead of memory.

| Register Fields |       | GCR Custom Base Register (GCR_CUSTOM_BASE Offset                                                                                                                               | Reset State |

|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Name            | Bits  | 0x0060)                                                                                                                                                                        |             |

| CR_CUSTOM_BASE  | 31:16 | This field sets the base address of the 64KB GCR custom user-defined block of the interAptiv MPS.                                                                              | Undefined   |

| GU_EN           | 0     | If this bit is set, the Address Region for the Custom GCR is enabled.<br>This bit cannot be set to 1 if GGU_EX = 0, indicating that a custom GCR is not<br>attached to the CM. | 0           |

|                 |       |                                                                                                                                                                                |             |

|                 |       |                                                                                                                                                                                |             |

|                 |       |                                                                                                                                                                                |             |

|                 |       |                                                                                                                                                                                |             |

The CM2 provides the capability of including custom (user-defined) GCRs. GGU\_EX indicates if the customer GCR registers exist or not.

The GCR\_CUSTOM\_BASE register sets the physical address of the base address of a 64KByte slice of memory space, where requests are directed to the Custom GCRs.

GGU\_EN enables the redirection of the memory request to the custom CGR memory registers instead of memory.

| Global In     | terrı | upt Controller Status Register                              |       |

|---------------|-------|-------------------------------------------------------------|-------|

| Register Fiel | ds    | Global Interrupt Controller Status Register (GCR_GIC_STATUS | Reset |

| Name          | Bits  | Offset 0x00D0)                                              | State |

| GIC_EX        | 0     | If this bit is set, the GIC is connected to the CM.         | 1     |

|               |       |                                                             |       |

|               |       |                                                             |       |

|               |       |                                                             |       |

|               |       |                                                             |       |

|               |       |                                                             |       |

|               |       |                                                             |       |

|               |       |                                                             |       |

|               |       |                                                             |       |

|               |       |                                                             |       |

| NIPS          | 6     |                                                             | 22    |

The GIC is configured into the system at IP build time. The chip designer can decide to include a GIC or not. GIC was configured into the system if the GIC\_EX bit is set.

| Global L2-Or          | nly Sy | nc Base Register                                                                                                                                                       |             |

|-----------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Register Fields       |        | GCR L2-Only Sync Base Register<br>(GCR_L2_ONLY_SYNC_BASE Offset 0x0070)                                                                                                | Reset State |

| Name                  | Bits   |                                                                                                                                                                        |             |

| GCR_L2_ONLY_SYNC_BASE | 31:12  | This field sets the base address of the 4KB GCR L2 only Sync of the interAptiv MPS.                                                                                    | Undefined   |

| CM_L2_ONLY_SYNC_EN    | 0      | If this bit is set, the CM will treat an uncached write request as a L2 only Sync.<br>If set to 0, the CM will treat the uncached write as a regular uncached request. | 0           |

|                       |        |                                                                                                                                                                        |             |

|                       |        |                                                                                                                                                                        |             |

|                       |        |                                                                                                                                                                        |             |

| MIPS                  |        |                                                                                                                                                                        | 23          |

The CM2 adds the ability to issue a barrier-sync to the L2 without executing a SYNC instruction, thus reducing the latency incurred for the sync. The L2-only sync provides a mechanism to guarantee that an uncached request does not pass previous cached requests in the L2 pipeline. For example, the L2-only SYNC can be used between a L2 HitWB cacheop and a subsequent uncached write, to ensure that the uncached write does not pass the writeback from the L2.

CM\_L2\_ONLY\_SYNC\_EN (bit 0) of the register must be set to a 1 for this feature to be enabled. The address match is performed on a 4KB boundary. An uncached write request address [31:12] that matches the address [31:12] in the GCR\_L2\_ONLY\_SYNC\_BASE will cause the CM2 to treat the uncached write request as an L2-only SYNC.

| Global Interrupt Controller Base Address Regis |       |                                                                                                                                                             | ster  |  |

|------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

| Register F                                     | ields | Global Interrupt Controller Base Address Register                                                                                                           | Reset |  |

| Name                                           | Bits  | (GCR_GIC_BASE Offset 0x0080)                                                                                                                                | State |  |

| GIC_<br>BaseAddress                            | 31:17 | This field sets the base address of the 128KB Global Interrupt Controller.                                                                                  | 0     |  |

| GIC_EN                                         | 0     | If this bit is set, the Address Region for the GIC is enabled. This bit can not be set to 1 if GIC_EX = 0, indicating that a GIC is not attached to the CM. | 0     |  |

|                                                |       |                                                                                                                                                             |       |  |

|                                                |       |                                                                                                                                                             |       |  |

|                                                |       |                                                                                                                                                             |       |  |

|                                                |       |                                                                                                                                                             |       |  |

|                                                |       |                                                                                                                                                             |       |  |

|                                                |       |                                                                                                                                                             |       |  |

|                                                | 5     |                                                                                                                                                             |       |  |

The Global Interrupt Controller Base Address Register is dependent on the GIC\_EX bit being set in the Global Interrupt Controller Status Register. Only if it is set is the Global Interrupt Controller Base Address Register valid. This register does 2 things, it is used to set the address of the GIC and to enable the GIC. The address is system dependent. You should consult your system specification or system designer to determine what address in your memory map the GIC is located at. That address must be on a 128k byte boundary. In other words the lower 17 bit of the address must be zeros. This register should be written at system initialization time with the value of that address.

In addition the GIC\_EN bit controls the enabling of the GIC. Once the GIC has been programmed this bit needs to be set to begin receiving interrupts.

# **Cache Revision Register**

Is there an L2 Cache?

| Register Fiel | ds   | Cache Revision Register (GCR_CACHE_REV Offset 0x00E0)                                                                                                                                 | Reset  |

|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Name          | Bits |                                                                                                                                                                                       | State  |

| MAJOR_REV     | 15:8 | This field reflects the major revision of the Cache block attached to the coherence<br>Cluster. A major revision might reflect the changes from one product generation to<br>another. | Preset |

| MINOR_REV     | 7:0  | This field reflects the minor revision of the Cache block attached to the coherence Cluster. A minor revision might reflect the changes from one release to another.                  | Preset |

|               |      |                                                                                                                                                                                       |        |

|               |      |                                                                                                                                                                                       |        |

|               |      |                                                                                                                                                                                       |        |

|               |      |                                                                                                                                                                                       |        |

|               |      |                                                                                                                                                                                       |        |

|               |      |                                                                                                                                                                                       |        |

The cache revision register tells you the Major and Minor revision of the L2 cache.

| Cluster F    | owe  | er Controller Status Register Regis                     | ster  |

|--------------|------|---------------------------------------------------------|-------|

| Register Fie | lds  | Global Power Controller Status Register (GCR_GPC_STATUS | Reset |

| Name         | Bits | Offset 0x00D0)                                          | State |

| CPC_EX       | 0    | If this bit is set, the CPC is connected to the CM2.    | 1     |

|              |      |                                                         |       |

|              |      |                                                         |       |

|              |      |                                                         |       |

|              |      |                                                         |       |

|              |      |                                                         |       |

|              |      |                                                         |       |

|              |      |                                                         |       |

|              |      |                                                         | 26    |

The Cluster power controller is configured into the system at IP build time. This register tells you if a CPC was configured into the system. NOTE: the CPC is always part of the core so this will be set to 1.

| Register F |      | IOCU Revision Register                                                                                                                                                                                     | Rese   |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Name       | Bits | (GCR_IOCU1_REV Offset 0x0200)                                                                                                                                                                              | State  |

| MAJOR_REV  | 15:8 | This field reflects the major revision of the IOCU attached to the CM. A major revision might reflect the changes from one product generation to another. The value of 0x0 means that no IOCU is attached. | Preset |

| MINOR_REV  | 7:0  | This field reflects the minor revision of the IOCU attached to the CM. A minor revision might reflect the changes from one release to another.                                                             | Preset |

|            |      |                                                                                                                                                                                                            |        |

The I/O Coherency Unit is configured into the system at IP build time. This register tells you if a IOCU was configured into the system. If the Major Revision field is 0 then there is no IOCU.

| <ul> <li>Address Regions</li> <li>Default Address Regions</li> <li>0, 4, Additional Address Regions</li> <li>Maps address to specific controllers</li> <li>Memory – CM controlled region</li> <li>CCA Override for L2 to OCP Coherency control</li> <li>IOCU – IOCU controlled region</li> <li>non-coherent and uncached transactions</li> </ul> Base Address <ul> <li>Base Address</li> <li>Mask to determine region size</li> </ul> |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| MIPS                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28 |

There are up to 5 programmable Address Regions that can be programmed to support memory mapped I/O or memory storage regions. The default region that covers any main memory not covered by another region.

+ A region that is mapped to memory storage can be configured to have a different CCA for the L2 to OCP interface than the L1 to L2 interface.

+ Reads and write requests to a region that has been mapped to the IOCU go directly to the IOCU as non-coherent and uncached transactions.

+ Each region is defined by a pair of GCR registers a Base Address Register and an Address Mask Register that determines its size.

The next slides will cover the configuration of these regions using these registers.

| • Addresses of | -      | <b>ters</b><br>Pair Offsets into t | he GCR address           | тар |

|----------------|--------|------------------------------------|--------------------------|-----|

|                | Region | Base Address<br>Register Offset    | Address Mask<br>Register |     |

|                | 0      | 0x0090                             | 0x0098                   |     |

|                | 1      | 0x00A0                             | 0x00A8                   |     |

|                | 2      | 0x00B0                             | 0x00B8                   |     |

|                | 3      | 0x00C0                             | 0x00C8                   |     |

|                |        |                                    |                          |     |

| NPS            |        |                                    |                          | 29  |

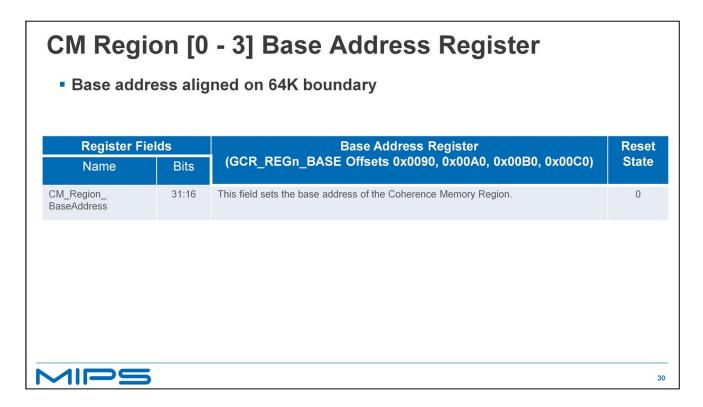

This table shows you the offsets into the GCR where the "region registers" are.

You program the regions physical address by writing to the regions CM Base Address Register. Since CM Address Regions must start on 64K byte boundaries only addresses with the lower 16 bits set to 0 are valid. The lower 16 bits will always read back as zeros.

NOTE: CM2 has only 4 regions so address registers for the other regions have been dropped.

| CM Regi                    | ion[0                                                                | - 3] Address Mask Register                                                                                                                                                                                                                                  |       |

|----------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Register Fi                | Register Fields Address Mask Register (GCR_REGn_MASK Offsets 0x0098, |                                                                                                                                                                                                                                                             | Reset |

| Name                       | Bits                                                                 | 0x00A8, 0x00B8, 0x00C8)                                                                                                                                                                                                                                     | State |

| CM_Region_<br>Address_Mask | 31:16                                                                | This field is used to set the size of the CM Region.<br>The only allowed values in this register are contiguous sets of leading 0x1's. An 0x1 preceded by a 0x0 is not allowed (e.g., the value of 0xfff0 is allowed, but the value 0xffef is not allowed). | UD    |

|                            | 5                                                                    |                                                                                                                                                                                                                                                             | 31    |

CM\_Region\_Address\_Mask determines the size of the region. This field is used along with its equivalent CM Region Base Address Register.

The request physical address is logically ANDed with the value of this register and ANDed with the value of the region's Base Address Register to see if the requested address is in range of this region. If it is the request it is routed to this CM region.

NOTE: CM2 has only 4 regions so mask registers for the other regions have been dropped.

| Register Fields         |      |                |                               | GCR_REGx_MASK Offsets                                                                         | Reset |

|-------------------------|------|----------------|-------------------------------|-----------------------------------------------------------------------------------------------|-------|

| Name                    | Bits | 0x0098, 0x00A8 | , 0x00B8,                     | 0x00C8)                                                                                       | State |

| CCA_<br>OVERRIDE_VALUE  | 7-5  |                |                               | BLE to force the Cache Coherence<br>ons on the L2/Memory OCP.                                 | 0     |

|                         |      | Encoding       | Name                          | Description                                                                                   |       |

|                         |      | 0x0            | WT                            | Write Through                                                                                 |       |

|                         |      | 0x2            | UC                            | Uncached                                                                                      |       |

|                         |      | 0x3            | WB                            | Write Back non-coherent                                                                       |       |

|                         |      | 0x4            | CWBE                          | Mapped to WB                                                                                  |       |

|                         |      | 0x5            | CWB                           | Mapped to WB                                                                                  |       |

|                         |      | 0x7            | UCA                           | Uncached Accelerated                                                                          |       |

| CCA_<br>OVERRIDE_ENABLE | 4    |                | ET is set to I<br>will have a | t to 1 and<br>Memory, then transactions with addresses<br>CCA value set to CCA_Override_Value | 0     |

Continuing with the Address Mask Register:

CCA\_Override\_Value and CCA\_Override\_Enable are used in conjunction with CM\_REGION\_TARGET memory region. If the CCA\_OVERRIDE\_ENABLE is not set then the CCA for the L2 to memory is the same as the CCA form the L1 caches to the L2. If the CCA\_OVERRIDE\_EENABLE bit is set then the CCA value in the CCA\_OVERRIDE\_VALUE field will be used for the CCA from L2 to Memory.

| CM Reg     | jion[0 | - 3] Ad          | ldress           | Mask F               | Register             |       |

|------------|--------|------------------|------------------|----------------------|----------------------|-------|

| Register F | ields  | Address N        | lask Registe     | r (GCR_REGn_         | MASK Offsets 0x0098, | Reset |

| Name       | Bits   |                  |                  | A8, 0x00B8, 0x       |                      | State |

| CM_Region_ | 1:0    | Maps this region | to the specified | device:.             |                      | 0     |

| TARGET     |        |                  | Encoding         | Meaning              |                      |       |

|            |        |                  | 0                | Disabled             |                      |       |

|            |        |                  | 1                | Memory               |                      |       |

|            |        |                  | 2                | 1 <sup>st</sup> IOCU |                      |       |

|            |        |                  | 3                | 2 <sup>nd</sup> IOCU |                      |       |

|            |        |                  |                  |                      |                      |       |

|            | 5      |                  |                  |                      |                      | :     |

More on the Address Mask Register:

The CM\_REGION\_TARGET directs the region to Memory or the I/O Coherency Unit.

NOTE: A second IOCU has been added with CM2.