# Programming the MIPS32® 34K™ Core Family

Document Number: MD00427 Revision 01.64 November 19, 2010 Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Tech, LLC, a Wave Computing company ("MIPS") and MIPS' affiliates as applicable. Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS or MIPS' affiliates as applicable or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines. Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS (AND MIPS' AFFILIATES AS APPLICABLE) reserve the right to change the information contained in this document to improve function, design or otherwise.

MIPS and MIPS' affiliates do not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS, MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPSr3, MIPS32, MIPS64, microMIPS32, microMIPS64, MIPS-3D, MIPS16, MIPS16e, MIPS-Based, MIPSsim, MIPSpro, MIPS-VERIFIED, Aptiv logo, microAptiv logo, interAptiv logo, microMIPS logo, MIPS Technologies logo, MIPS-VERIFIED logo, proAptiv logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, M14K, 5K, 5Kc, 5Kf, 24K, 24Kc, 24Kf, 24KE, 24KEc, 24KEf, 34K, 34Kc, 34Kf, 74K, 74Kc, 74Kf, 1004K, 1004Kc, 1004Kf, 1074Kc, 1074Kc, 1074Kf, R3000, R4000, R5000, Aptiv, ASMACRO, Atlas, "At the core of the user experience.", BusBridge, Bus Navigator, CLAM, CorExtend, CoreFPGA, CoreLV, EC, FPGA View, FS2, FS2 FIRST SILICON SOLUTIONS logo, FS2 NAVIGATOR, HyperDebug, HyperJTAG, IASim, iFlowtrace, interAptiv, JALGO, Logic Navigator, Malta, MDMX, MED, MGB, microAptiv, microMIPS, Navigator, OCI, PDtrace, the Pipeline, proAptiv, Pro Series, SEAD-3, SmartMIPS, SOC-it, and YAMON are trademarks or registered trademarks of MIPS and MIPS' affiliates as applicable in the United States and other countries.

All other trademarks referred to herein are the property of their respective owners. U @o

M '#

| Chapter 1: Introduction                                                         | 11 |

|---------------------------------------------------------------------------------|----|

| 1.1: Readership                                                                 |    |

| 1.2: In this chapter                                                            |    |

| 1.3: Chapter summary                                                            |    |

| 1.4: Typographical conventions                                                  |    |

| 1.5: Register diagrams and field descriptions                                   |    |

| 1.6: Finding information in this manual                                         |    |

| 1.7: Specification summary                                                      |    |

| 1.8: Pipeline and implementation                                                |    |

|                                                                                 |    |

| Chapter 2: The MIPS® MT ASE - Multithreading the RISC way                       | 17 |

| 2.1: What's a thread and its context?                                           |    |

| 2.2: Why multi-threading?                                                       |    |

| 2.3: Different kinds of multi-threading: TCs and VPEs                           |    |

| 2.3.1: How an MT CPU's hardware uses TCs and VPEs                               |    |

| 2.3.2: CPU resources and registers shared between all threads                   |    |

| 2.3.3: CPU resources and registers replicated per-TC                            |    |

| 2.3.4: CPU resources and registers replicated per-VPE                           |    |

| 2.4: When can't threads run?                                                    |    |

| 2.5: Thread-scheduling decisions and the policy manager                         |    |

| 2.6: Multithreading, exceptions and interrupts                                  |    |

| 2.6.1: Multithreading and interrupts                                            |    |

| 2.7: Multithreading, non-blocking loads and stores, and gating storage          |    |

| 2.7: 1. Gating storage                                                          |    |

| 2.8.1: Yield, Yield Qualifiers and threads waiting for hardware events          |    |

| 2.8.2: All MT instructions in alphabetical order                                |    |

| 2.9: Multithreading ASE - CP0 (privileged) registers                            |    |

| 2.9.1: What CP0 registers are per-TC, per-VPE and per-CPU?                      |    |

| 2.9.2: VPEControl                                                               |    |

| 2.9.3: TCRestart, TCHalt and TCContext                                          |    |

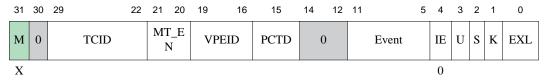

| 2.9.4: TCStatus                                                                 |    |

| 2.9.5: TCBind                                                                   |    |

| 2.9.6: MVPConf0-1 - read-only multithreading-specific configuration information |    |

| 2.9.7: MVPControl Register - CPU-wide VPE control                               |    |

| 2.9.8: VPEConf0-1 registers - initializable per VPE resource lists              |    |

| 2.9.9: YQMask register - enable yield "conditions"                              |    |

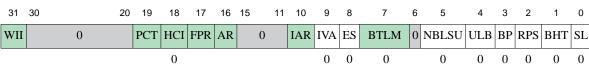

| 2.9.10: VPEOpt register - reserve some cache "way" for use of one VPE           |    |

| 2.9.11: Shadow register configuration SRSConf0-4                                |    |

| 2.9.12: Thread scheduling hints - TCSchedule, TCScheFBack, VPESchedule          |    |

| Chapter 3: How the 34K™ core implements multi-threading                         | 44 |

|                                                                                 |    |

| 3.1: The 34K <sup>™</sup> core pipeline and multithreading                      |    |

| 3.1.1: Resource limits and consequences                                         |    |

| 3.1.2: Choosing what TC's instruction to issue next                             |    |

| 3.2: Thread scheduling in the 34K <sup>™</sup> core                             |    |

| 3.2.2: The Policy Manager interface                                             |    |

| 3.2.3: MIPS Policy managers included with the 34K <sup>™</sup> core family      |    |

| 3.2: Inter-thread communication storage (ITC)                                   |    |

| 3.3.1: Configuring ITC base address and cell repeat interval                    |    |

| 3.4: The 34K <sup>™</sup> core and interrupts                                   |    |

| 3.5: Synchronization: "II" and "sc" instructions implementation                 |    |

|                                                                                 |    |

| Chapter 4: Initialization and identity                                              | 53 |

|-------------------------------------------------------------------------------------|----|

| 4.1: Probing your CPU - Config CP0 registers                                        | 53 |

| 4.1.1: The Config register                                                          | 54 |

| 4.1.2: The Config1-2 registers                                                      | 56 |

| 4.1.3: The Config3 register                                                         | 57 |

| 4.1.4: The Config6 register                                                         | 58 |

| 4.1.5: CPU-specific configuration — Config7                                         |    |

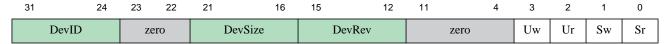

| 4.2: PRId register — identifying your CPU type                                      |    |

| 4.3: Multi-Threaded bootstrap issues                                                |    |

| 4.3.1: Bootstrapping without worrying about multithreading                          | 61 |

| 4.3.2: Configuring your choice of VPEs and TCs                                      |    |

| 4.3.3: Setting up a VPE for legacy software                                         | 63 |

| 4.3.4: Sharing and not sharing the TLB                                              |    |

| 4.3.5: Setting up a TC to run a thread                                              |    |

| 4.3.6: TCs recycled as Shadow registers                                             |    |

| Chapter 5: Memory map, caching, reads, writes and translation                       | 67 |

| 5.1: The memory map                                                                 | 67 |

| 5.2: Fixed mapping option                                                           | 68 |

| 5.3: Reads, writes and synchronization                                              | 68 |

| 5.3.1: Read/write ordering and cache/memory data queues in the 34K™ core            | 68 |

| 5.3.2: The "sync" instruction in 34K™ family cores                                  |    |

| 5.3.3: Write gathering and "write buffer flushing" in 34K™ family cores             | 70 |

| 5.4: Caches                                                                         |    |

| 5.4.1: The L2 cache option                                                          |    |

| 5.4.2: Cacheability options                                                         |    |

| 5.4.3: Uncached accelerated writes                                                  |    |

| 5.4.4: The cache instruction and software cache management                          |    |

| 5.4.5: Cache instructions and CP0 cache tag/data registers                          |    |

| 5.4.6: L1 Cache instruction timing                                                  |    |

| 5.4.7: L2 cache instruction timing                                                  |    |

| 5.4.8: Cache management when writing instructions - the "synci" instruction         |    |

| 5.4.9: Cache management and multithreaded CPUs                                      |    |

| 5.4.10: Cache aliases                                                               |    |

| 5.4.11: Cache locking                                                               |    |

| 5.4.12: Cache initialization and tag/data registers                                 |    |

| 5.4.13: L23TagLo Regiser                                                            |    |

| 5.4.14: L23DataLo Register                                                          |    |

| 5.4.15: L23DataHi Register                                                          |    |

| 5.4.16: TagLo registers in special modes                                            |    |

| 5.4.17: Parity error exception handling and the CacheErr register                   |    |

| 5.4.18: ErrCtl register                                                             |    |

| 5.5: Bus error exception                                                            |    |

| 5.6: Scratchpad memory/SPRAM                                                        |    |

| 5.7: Common Device Memory Map                                                       |    |

| 5.8: The TLB and translation                                                        |    |

| 5.8.1: A TLB entry                                                                  |    |

| 5.8.2: The TLB and Multithreading                                                   |    |

| 5.8.3: Live translation and micro-TLBs                                              |    |

| 5.8.4: Reading and writing TLB entries: Index, Random and Wired                     |    |

| 5.8.5: Reading and writing TLB entries - EntryLo0-1, EntryHi and PageMask registers |    |

| 5.8.6: TLB initialization and duplicate entries                                     |    |

| 5.8.7: TLB exception handlers — BadVaddr, Context, and ContextConfig registers      |    |

| 5.5.1. TED ONOOPHON NAMED DAG VAGGI, CONTON, AND CONTONING IGGISTON                 |    |

| Chapter 6: Programming the 34K™ core in user mode                                 | 93  |

|-----------------------------------------------------------------------------------|-----|

| 6.1: User-mode accessible "Hardware registers"                                    |     |

| 6.2: Prefetching data                                                             |     |

| 6.3: Using "synci" when writing instructions                                      | 94  |

| 6.4: The multiplier                                                               | 95  |

| 6.5: Tuning software for the 34K <sup>™</sup> family pipeline                     | 96  |

| 6.5.1: Cache delays and mitigating their effect                                   | 96  |

| 6.5.2: Branch delay slot                                                          | 97  |

| 6.6: Tuning floating-point                                                        | 97  |

| 6.6.1: -Branch misprediction delays                                               | 98  |

| 6.6.2: Data dependency delays classified                                          | 98  |

| Chapter 7: Kernel-mode (OS) programming and Release 2 of the MIPS32® Architect    |     |

| 7.1: Hazard barrier instructions                                                  |     |

| 7.2: MIPS32® Architecture Release 2 - enhanced interrupt system(s)                |     |

| 7.2.1: Traditional MIPS® interrupt signalling and priority                        |     |

| 7.2.2: VI mode - multiple entry points, interrupt signalling and priority         |     |

| 7.2.3: External Interrupt Controller (EIC) mode                                   |     |

| 7.3: Exception Entry Points                                                       |     |

| 7.3.1: Summary of exception entry points                                          |     |

| 7.4: Shadow registers                                                             |     |

| 7.4.1: Recycling multi-threading CPU's TCs as shadow sets                         |     |

| 7.5: Saving Power                                                                 |     |

| 7.6: The HWREna register - Control user rdhwr access                              | 110 |

| Chapter 8: Floating point unit                                                    | 113 |

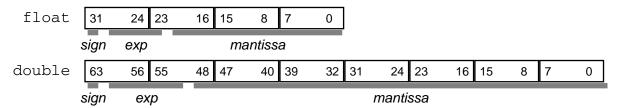

| 8.1: Data representation                                                          | 113 |

| 8.2: Basic instruction set                                                        |     |

| 8.3: Floating point loads and stores                                              |     |

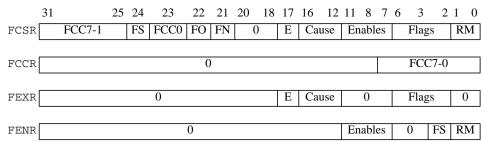

| 8.4: Setting up the FPU and the FPU control registers                             | 115 |

| 8.4.1: IEEE options                                                               |     |

| 8.4.2: FPU "unimplemented" exceptions (and how to avoid them)                     |     |

| 8.4.3: FPU control register maps                                                  |     |

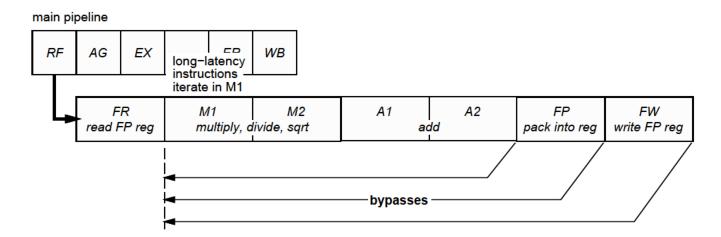

| 8.5: FPU pipeline and instruction timing                                          |     |

| 8.5.1: FPU register dependency delays                                             |     |

| 8.5.2: Delays caused by long-latency instructions looping in the M1 stage         |     |

| 8.5.3: Delays on FP load and store instructions                                   |     |

| 8.5.4: Delays when main pipeline waits for FPU to decide not to take an exception |     |

| 8.5.5: Delays when main pipeline waits for FPU to accept an instruction           |     |

| 8.5.6: Delays on mfc1/mtc1 instructions                                           |     |

| 8.5.7: Delays caused by dependency on FPU status register fields                  |     |

| 8.5.8: Slower operation in MIPS I™ compatibility mode                             | 121 |

| Chapter 9: The MIPS32® DSP ASE                                                    | 123 |

| 9.1: Features provided by the MIPS® DSP ASE                                       | 123 |

| 9.2: The DSP ASE control register                                                 |     |

| 9.2.1: DSP accumulators                                                           |     |

| 9.3: Software detection of the DSP ASE                                            |     |

| 9.4: DSP instructions                                                             |     |

| 9.4.1: Hints in instruction names                                                 |     |

| 9.4.2: Arithmetic - 64-bit                                                        |     |

| 9.4.3: Arithmetic - saturating and/or SIMD Types                                  | 127 |

|    | 9.4.4: Bit-shifts - saturating and/or SIMD types                       |              |

|----|------------------------------------------------------------------------|--------------|

|    | 9.4.5: Comparison and "conditional-move" operations on SIMD types      | . 127        |

|    | 9.4.6: Conversions to and from SIMD types                              | . 128        |

|    | 9.4.7: Multiplication - SIMD types with result in GP register          |              |

|    | 9.4.8: Multiply Q15s from paired-half and accumulate                   | . 129        |

|    | 9.4.9: Load with register + register address                           | . 129        |

|    | 9.4.10: DSPControl register access                                     | . 129        |

|    | 9.4.11: Accumulator access instructions                                |              |

|    | 9.4.12: Dot products and building blocks for complex multiplication    |              |

|    | 9.4.13: Other DSP ASE instructions                                     |              |

|    | 9.5: Macros and typedefs for DSP instructions                          |              |

|    | 9.6: Almost Alphabetically-ordered table of DSP ASE instructions       |              |

|    | 9.7: DSP ASE instruction timing                                        | . 136        |

| Cŀ | napter 10: 34K™ core features for debug and profiling                  | 138          |

|    | 10.1: EJTAG on-chip debug unit                                         |              |

|    | 10.1.1: Debug communications through JTAG                              | . 139        |

|    | 10.1.2: Debug mode                                                     | . 139        |

|    | 10.1.3: The debug unit and multi-threading                             | . 140        |

|    | 10.1.4: Exceptions in debug mode                                       | . 140        |

|    | 10.1.5: Single-stepping                                                | . 141        |

|    | 10.1.6: The "dseg" memory decode region                                | . 141        |

|    | 10.1.7: EJTAG CP0 registers, particularly Debug                        | . 143        |

|    | 10.1.8: The DCR (debug control) memory-mapped register                 | . 145        |

|    | 10.1.9: JTAG-accessible registers                                      |              |

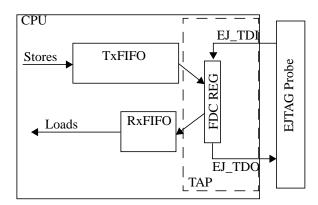

|    | 10.1.10: Fast Debug Channel                                            |              |

|    | 10.1.11: EJTAG breakpoint registers                                    |              |

|    | 10.1.12: Understanding breakpoint conditions                           |              |

|    | 10.1.13: Imprecise debug breaks                                        | . 154        |

|    | 10.1.14: PC Sampling with EJTAG                                        |              |

|    | 10.1.15: JTAG-accessible and memory-mapped PDtrace TCB Registers       |              |

|    | 10.2: PDtrace™ instruction trace facility                              |              |

|    | 10.2.1: 34K core-specific fields in PDtrace™ JTAG-accessible registers |              |

|    | 10.2.2: CP0 registers for the PDtrace™ logic                           |              |

|    | 10.2.3: JTAG triggers and local control through TraceIBPC/TraceDBPC    |              |

|    | 10.2.4: UserTraceData1 reg and UserTraceData2 reg                      |              |

|    | 10.2.5: Summary of when trace happens                                  |              |

|    | 10.3: CP0 Watchpoints                                                  |              |

|    | 10.3.1: The WatchLo0-3 registers                                       |              |

|    | 10.3.2: The WatchHi0-3 registers                                       |              |

|    | 10.4: Performance counters                                             |              |

|    | 10.4.1: Reading the event table.                                       | . 167        |

| Αp | ppendix A: References                                                  | 173          |

| Ar | ppendix B: Glossary                                                    | 175          |

| Ī  |                                                                        |              |

| Αþ | opendix C: CP0 register summary and reference                          |              |

|    | C.1: CP0 registers by name                                             |              |

|    | C.2: CP0 registers by number                                           |              |

|    | C.3: CP0 registers by function                                         | . 183<br>194 |

|    | TO A MINISTRACTION OF PLANMENT ADSCRIPTIONS                            | 1 24 /       |

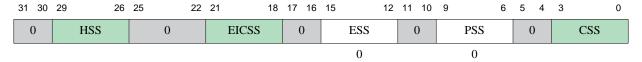

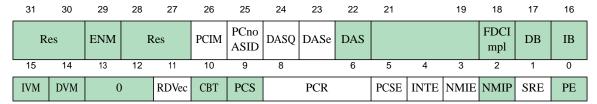

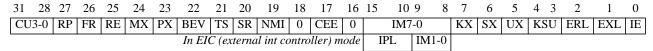

| C.4.1: Status register                                                           | 184 |

|----------------------------------------------------------------------------------|-----|

| C.4.2: The UserLocal register                                                    | 185 |

| C.4.3: Exception handling: Cause register                                        | 186 |

| C.4.4: Count and Compare                                                         | 187 |

| C.4.5: The Config7 register                                                      | 188 |

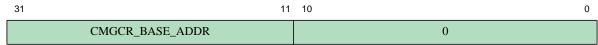

| C.4.6: The CMGCRBase register                                                    |     |

| C.4.7: Cache registers in special diagnostic modes                               | 190 |

| Appendix D: MIPS® Architecture quick-reference sheet(s)                          | 191 |

| D.1: General purpose register numbers and names                                  |     |

| D.2: User-level changes with Release 2 of the MIPS32® Architecture               |     |

| D.2.1: Release 2 of the MIPS32® Architecture - new instructions for user-mode    |     |

| D.2.2: Release 2 of the MIPS32® Architecture - Hardware registers from user mode |     |

| D.3: FPU changes in Release 2 of the MIPS32® Architecture                        | 193 |

| Appendix E: Revision History                                                     | 105 |

| Appendix E. Nevision instory                                                     | 193 |

| Figure 2.1: Fields in the VPEControl register                                       | 34  |

|-------------------------------------------------------------------------------------|-----|

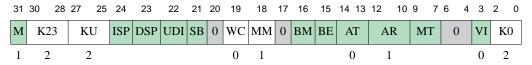

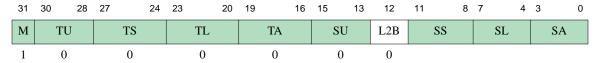

| Figure 2.2: Fields in the TCStatus register                                         | 35  |

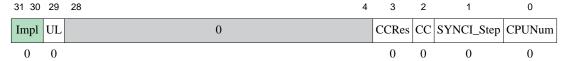

| Figure 2.3: Fields in the TCBind register                                           | 37  |

| Figure 2.4: Fields in the MVPConf0-1 registers                                      | 37  |

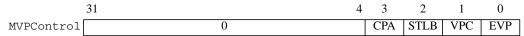

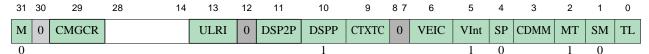

| Figure 2.5: Fields in the MVPControl register                                       | 38  |

| Figure 2.6: Fields in the VPEConf0-1 registers                                      | 39  |

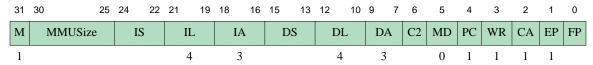

| Figure 2.7: Fields in the VPEOpt register                                           | 40  |

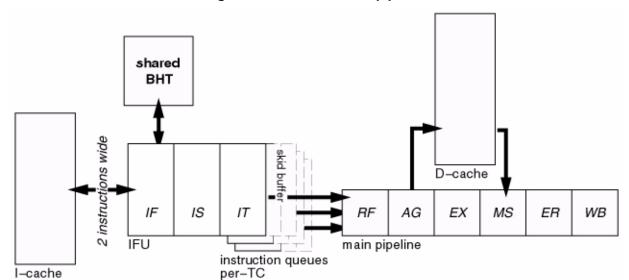

| Figure 3.1: The 34K™ core pipeline                                                  | 41  |

| Figure 3.2: Fields in the TCSchedule and VPESchedule registers (WRR policy manager) | 47  |

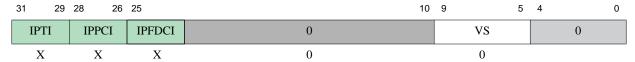

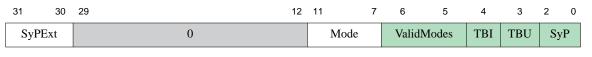

| Figure 3.3: Field layout in an ITC cell control view                                | 48  |

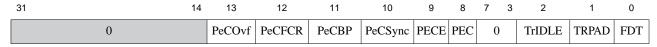

| Figure 3.4: ITC configuration information                                           | 49  |

| Figure 4.1: Fields in the Config Register                                           | 54  |

| Figure 4.2: Fields in the Config1 Register                                          | 56  |

| Figure 4.3: Fields in the Config2 Register                                          | 56  |

| Figure 4.4: Config3 Register Format                                                 | 57  |

| Figure 4.5: Config6 Register Format                                                 | 58  |

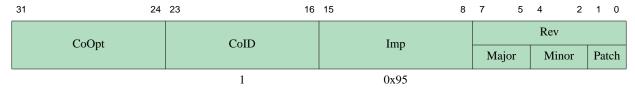

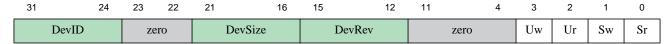

| Figure 4.6: Fields in the PRId Register                                             | 59  |

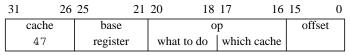

| Figure 5.1: Fields in the encoding of a cache instruction                           | 72  |

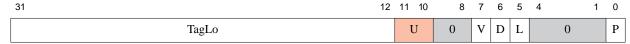

| Figure 5.2: Fields in the TagLo Registers                                           | 78  |

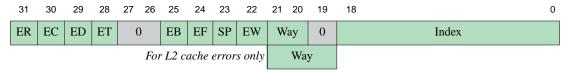

| Figure 5.3: L23TagLo Register Format                                                |     |

| Figure 5.4: L23DataLo Register Format                                               | 79  |

| Figure 5.5: L23DataHi Register Format                                               | 80  |

| Figure 5.6: Fields in the CacheErr Register                                         |     |

| Figure 5.7: Fields in the ErrCtl Register                                           |     |

| Figure 5.8: SPRAM (scratchpad RAM) configuration information in TagLo               |     |

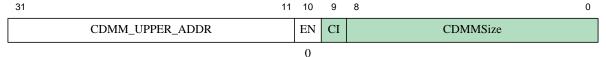

| Figure 5-9: Fields in the CDMMBase Register                                         |     |

| Figure 5.10: Fields in the Access Control and Status (ACSR) Register                | 86  |

| Figure 5.11: Fields in a 34K™ core TLB entry                                        |     |

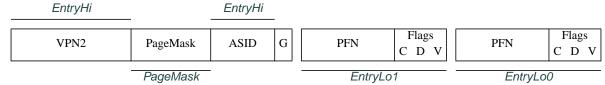

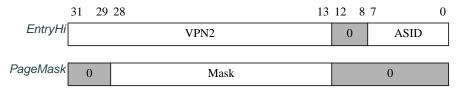

| Figure 5.12: Fields in the EntryHi and PageMask registers                           |     |

| Figure 5.13: Fields in the EntryLo0-1 registers                                     | 89  |

| Figure 5.14: Fields in the Context register when Config3CTXTC=0 and Config3SM=0     | 90  |

| Figure 5.15: Fields in the Context register when Config3CTXTC=1 or Config3SM=1      | 91  |

| Figure 5.16: Fields in the ContextConfig register                                   | 92  |

| Figure 7.1: Fields in the IntCtl Register                                           | 103 |

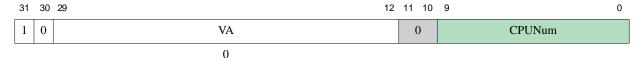

| Figure 7.2: Fields in the EBase Register                                            | 106 |

| Figure 7.3: Fields in the SRSCtl Register                                           | 107 |

| Figure 7.4: Fields in the SRSMap Register                                           | 109 |

| Figure 7.5: Fields in the SRSConf0 register                                         | 109 |

| Figure 7.6: Fields in the HWREna Register                                           | 110 |

| Figure 8.1: How floating point numbers are stored in a register                     |     |

| Figure 8.2: Fields in the FIR register                                              |     |

| Figure 8.3: Floating point control/status register and alternate views              |     |

| Figure 8.4: Overview of the FPU pipeline                                            |     |

| Figure 9.1: Fields in the DSPControl Register                                       |     |

| Figure 10.1: Fields in the EJTAG CP0 Debug register                                 |     |

| Figure 10.2: Exception cause bits in the debug register                             |     |

| Figure 10.3: Debug register - exception-pending flags                               | 145 |

| Figure 10.4: Fields in the memory-mapped DCR (debug control) register               |     |

| Figure 10.5: Fields in the JTAG-accessible ImpCode register                         |     |

| Figure 10.6: Fields in the JTAG-accessible EJTAG_CONTROL register                   |     |

| Figure 10.7: Fast Debug Channel                                                     |     |

| Figure 10.8: Fields in the FDC Access Control and Status (FDACSR) Register          | 150 |

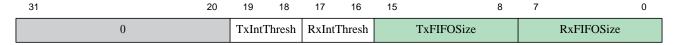

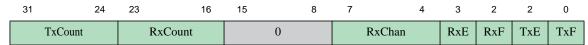

| Figure 10.9: Fields in the FDC Config (FDCFG) Register                              |     |

| Figure 10.10: Fields in the FDC Status (FDSTAT) Register                       | 151 |

|--------------------------------------------------------------------------------|-----|

| Figure 10.11: Fields in the FDC Receive (FDRX) Register                        | 151 |

| Figure 10.12: Fields in the FDC Transmit (FDTXn) Registers                     | 151 |

| Figure 10.13: Fields in the IBS/DBS (EJTAG breakpoint status) registers        | 152 |

| Figure 10.14: Fields in the hardware breakpoint control registers (IBCn, DBCn) | 153 |

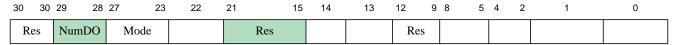

| Figure 10.15: Fields in the TCBCONTROLE register                               | 159 |

| Figure 10.16: Fields in the TCBCONFIG register                                 | 159 |

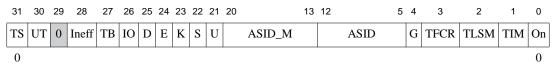

| Figure 10.17: Fields in the TraceControl Register                              | 159 |

| Figure 10.18: Fields in the TraceControl2 Register                             | 160 |

| Figure 10.19: Fields in the TraceControl3 register                             | 160 |

| Figure 10.20: Fields in the TracelBPC/TraceDBPC registers                      | 162 |

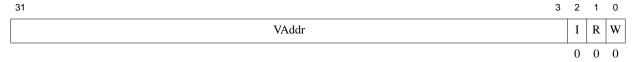

| Figure 10.21: Fields in the WatchLo0-3 Register                                | 165 |

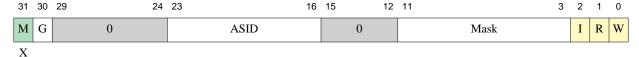

| Figure 10.22: Fields in the WatchHi0-3 Register                                | 165 |

| Figure 10.23: Fields in the PerfCtl Registers                                  | 166 |

| Figure C.1: All Status register fields                                         | 184 |

| Figure C.2: Fields in the Cause register                                       | 186 |

| Figure C-3: Fields in the Config7 Register                                     | 188 |

| Figure C-4: Fields in the CMGCRBase Register                                   | 190 |

| Figure C-5: Fields in the TagLo Register (ErrCtl[WST] set)                     | 190 |

|                                                                                |     |

| Table 2.1: MTTR/MFTR - "U" and "SEL" values                                   |     |

|-------------------------------------------------------------------------------|-----|

| Table 2.2: MT instruction summary in alphabetical order                       |     |

| Table 2.3: MTTR/MFTR "assembler idioms" in alphabetical order                 | 31  |

| Table 2.4: CP0 registers required by MIPS® MT ASE                             |     |

| Table 2.5: Thread exception codes in VPEControl[EXCPT]                        | 34  |

| Table 2.6: TC summary state as expressed in per-TC register fields            | 37  |

| Table 3.1: Dynamic priorities for finer resolution - group priority sequences | 46  |

| Table 3.2: ITC cell views and what they do                                    | 48  |

| Table 4.1: Roles of Config registers                                          | 53  |

| Table 4.2: 34K™® core releases and PRId[Revision] fields                      | 59  |

| Table 5.1: Basic MIPS32® architecture memory map                              | 67  |

| Table 5.2: Fixed memory mapping                                               |     |

| Table 5.3: Cache Code Values                                                  |     |

| Table 5.4: Operations on a cache line available with the cache instruction    |     |

| Table 5.1: Caches and their CP0 cache tag/data registers                      |     |

| Table 5.5: Cache instruction timings                                          |     |

| Table 5.6: L23DataLo Register Field Description                               |     |

| Table 5.7: L23DataHi Register Field Description                               |     |

| Table 5.8: Recommended ContextConfig Values                                   |     |

| Table 6.1: Hints for "pref" instructions                                      |     |

| Table 6.2: Register → eager consumer delays                                   |     |

| Table 6.3: Lazy producer → register delays                                    |     |

| Table 7.1: All Exception entry points                                         |     |

| Table 8.1: FPU (co-processor 1) control registers                             |     |

| Table 8.2: Long-latency FP instructions                                       | 120 |

| Table 9.1: Mask bits for instructions accessing the DSPControl register       |     |

| Table 9.2: DSP instructions in alphabetical order                             |     |

| Table 10.1: JTAG instructions for the EJTAG unit                              |     |

| Table 10.2: EJTAG debug memory region map ("dseg")                            |     |

| Table 10.3: Fields in the JTAG-accessible EJTAG_CONTROL register              |     |

| Table 10.4: FDC Register Mapping                                              |     |

| Table 10.5: Mapping TCB Registers in drseg                                    |     |

| Table 10.6: Fields in the TCBCONTROLA register                                |     |

| Table 10.7: Fields in the TCBCONTROLB register                                |     |

| Table 10.8: Fields in the TCBCONTROLC register                                |     |

| Table 10.9: Performance counter events                                        |     |

| Table C.1: Register Index by Name                                             |     |

| Table C.2: Cross-referenced list of CP0 registers by number                   |     |

| Table C.3: CP0 registers grouped by function                                  |     |

| Table C.4: Exception Code values in Cause[ExcCode]                            |     |

| Table D.1: Conventional names of registers with usage mnemonics               |     |

| Table D.2: Release 2 of the MIPS32® Architecture - new instructions           | 192 |

I

# Introduction

The MIPS32® 34K<sup>™</sup> core is a 32-bit MIPS32 CPU core for SoC ("System-On-a-chip") applications, licensed as synthesizable RTL. In typical 65nm process technology it runs at up to 800MHz with a 8-9-stage pipeline. But what is special about the 34K core are the following features:

- The MIPS® MT ASE: The multithreading ASE ("application-specific extension" to the MIPS architecture). It's a modest addition to the instruction set, but a profound change to the CPU, which can now run multiple threads concurrently. The set of software-visible resources devoted to one thread are known as a TC. The MT ASE allows for two multithreading models which are very different for software:

- Multiple Virtual Processing Elements (VPEs) in a CPU: each "VPE' has at least one TC together with its own copies of everything required to make it just like an independent MIPS CPU. Your 2-VPE (or more) core seems to software just like a 2-CPU "SMP" multiprocessor: indeed, it can run SMP software software which knows nothing about MIPS MT without requiring any CPU-related changes.

- Multiple concurrent threads running within one VPE, usable by software which knows about MIPS MT. These

multiple threads are relatively cheap, because they're equipped only with the resources necessary to run userlevel programs (but they share a lot of OS-controlled resources.)

The 34K core supports both models of multithreading.

Much of this manual won't make any sense until you get your head round multithreading, so unless you're thoroughly familiar with it already you should acquaint yourself with Chapter 2, "The MIPS® MT ASE - Multithreading the RISC way" on page 17.

• DSP ASE: this adds a lot of new computational instructions with a fixed-point math unit crafted to speed up popular signal-processing algorithms, which form a large part of the computational load for voice and imaging applications. Some of these functions are "SIMD" - they might, for example, do two math operations at once on two 16-bit values packed into one 32-bit register.

There's a guide to the DSP ASE in Chapter 9, "The MIPS32® DSP ASE" on page 123 and the formal specification is [MIPSDSP].

# 1.1 Readership

This document is for programmers who are already familiar with the MIPS® architecture and who can read MIPS assembler language (if that's not you yet, you'd probably benefit from reading a generic MIPS book, see Appendix A, "References" on page 173).

More precisely, you should definitely be reading this manual if you have an OS, compiler or low-level application which already runs on some earlier MIPS CPU, and you want to adapt it to the 34K core. So this document concentrates on where a MIPS 34K family core behaves differently from its predecessors. That's either:

- Behavior which is not completely specified by Release 2 of the MIPS32® architecture: these either concern privileged operation, or are timing-related.

- Behavior which was standardized only in the recent Release 2 of the MIPS32 specification (and not in previous versions). All Release 2 features are formally documented in [MIPS32]<sup>1</sup>, and [MIPS32V1] contains a brief summary.

But the summary is too brief to program from, and the details are widely spread; so you'll find a shortform presentation of the changes here in Section D.2 "User-level changes with Release 2 of the MIPS32® Architecture".

Details of timing, relevant to engineers optimizing code (and that very small audience of compiler writers).

This manual is intentionally much more focussed and therefore smaller than the full [SUM] manual. It does leave some material out; if you need to write processor subsystem diagnostics, this will not be enough! If you want a very careful corner-cases-included delineation of exactly what an instruction does, you'll need [MIPS32V2]... and so on.

For readability, some MIPS32 material is repeated here, particularly where a reference would involve a large excursion for the reader for a small saving for the author. Appendices mention every user-level-programming difference any active MIPS software engineer is likely to notice when programming the 34K core.

# 1.2 In this chapter

In the remainder of this chapter you'll find:

- Section 1.3, "Chapter summary": what's in the chapters (hot links if you're reading online).

- Section 1.4, "Typographical conventions": a manual like this is made easier to read (though perhaps not made more beautiful) if we use typographical conventions so you can recognize machine registers, instructions and so on. Here's what they look like.

- Section 1.6 "Finding information in this manual": how to find things in here, whether you're reading online or on paper.

- Section 1.7, "Specification summary": a terse summary of facts and figures.

# 1.3 Chapter summary

- Chapter 2, "The MIPS® MT ASE Multithreading the RISC way" on page 17: about the MIPS Multi-Threading instruction set extension ("ASE").

- Chapter 3, "How the 34K<sup>TM</sup> core implements multi-threading" on page 41: implementation options and more details.

- Chapter 4, "Initialization and identity" on page 53: setting up the 34K core, including its multi-threading system.

- Chapter 5, "Memory map, caching, reads, writes and translation" on page 67: all about memory accesses and translation.

<sup>1.</sup> References (in square brackets) are listed in Appendix A, "References" on page 173.

#### Introduction

- Chapter 7, "Kernel-mode (OS) programming and Release 2 of the MIPS32® Architecture" on page 101: use of "hazard barriers", the advanced interrupt system, shadow registers and power management.

- Chapter 10, "34KTM core features for debug and profiling" on page 138: EJTAG debug unit, watchpoints and performance counters.

- Chapter 6, "Programming the 34K<sup>TM</sup> core in user mode" on page 93: on tuning code specifically for the 34K core family.

- Chapter 8, "Floating point unit" on page 113: a software view of the (optional) 64-/32-bit floating point unit.

- Chapter 9, "The MIPS32® DSP ASE" on page 123: the instruction set extension for faster media algorithms.

#### Appendices:

- Appendix A, "References" on page 173: further reading.

- Appendix B, "Glossary" on page 175: a glossary of terms which may be unfamiliar (particularly relating to multi-threading).

- Appendix C, "CP0 register summary and reference" on page 179: functionally orientated index to the 34K core's

"co-processor zero" registers and fields, and contains descriptions of all the registers not already included in one

of the other chapters.

- Appendix D, "MIPS® Architecture quick-reference sheet(s)" on page 191: handy guide to easily-forgotten data on MIPS.

- Appendix E, "" on page 195: for this document.

# 1.4 Typographical conventions

CPU register names are in *oblique monospace*. *Co-processor zero* (*CP0*) registers fields are shown after the register name in brackets, so the interrupt enable bit in the *Status* register appears as *Status[IE]*. CP0 register numbers are denoted by n.s, where "n" is the register number (between 0-31) and "s" is the "select" field (0-7). If the select field is omitted, it's zero. A select field of "x" denotes all eight potential select numbers.

The acronym *CP0* in the paragraph above is a word defined in Chapter B, "Glossary" on page 175 and shows up in *italics* - but if you're reading on-line it also shows up as *blue*, showing that it's a link which you can click to get to the definition.

References to other manuals are collected together in Appendix A, "References" on page 173 and look like this [MIPS32].

Instruction mnemonics and assembler code fragments are set in **bold monospace**, core interface signal names in *small italics*, and C or other programming language constructs in monospace.

To use register and field names in your program, you'll need a C header file or something similar. It's probably better and easier not to write your own: see [m32c0.h] and [mt.h].

## 1.5 Register diagrams and field descriptions

It's a tradition of MIPS CPUs that most control and status information is passed through registers - the most numerous are the "CPO" registers used for kernel-level CPU control operations, but there are also memory-mapped registers in the debug unit and to control special memory arrays. All of them are 32 bits wide.

Many of the registers are broken up into multiple fields with substantially independent meanings and effects. Any register which is not simply a 32-bit number comes with a register "figure", and there's a list of figures at the start of this manual. The register figures are growing extra information in this version of the manual:

• We're introducing color-codes to identify fields. Fields which you can write, have some hardware effect and read back the same are regarded as "standard" and have a white background. But the background color tells you which fields are read-only (green), which are zero or "X" (gray), are purely for software use (blue-green), which are *not* just write-and-read-back (yellow), or are reserved and where use might be dangerous (red):

| read-only (green) | zero/X (gray) | software-only (blue/ | not just write-back | reserved, take care |

|-------------------|---------------|----------------------|---------------------|---------------------|

| read-only (green) | Zelo/A (glay) | green)               | (yellow)            | (red)               |

If you've printed this manual in black-and-white, those will all look much the same, sorry!

• Register diagrams may carry a third row (below the field descriptions in the boxes) which tell you about any value guaranteed to be in the register after a hardware reset. Those values will always be described separately in the field descriptions, and careful programmers will probably avoid relying on them wherever they can.

## 1.6 Finding information in this manual

If you're reading this manual on-screen, text shown in blue is a hot-link; click on the text to go to the section, figure or table referenced. The chapter index and lists of tables and figures at the start of the book is click-through too.

All the special *Co-processor zero* (*CP0*) registers are listed in Appendix C, "CP0 register summary and reference" on page 179. That appendix has the registers listed by name, by number and by function. The by-number table has hotlinks to other sections where each is mentioned - and for those reading on paper, all those links have page numbers.

# 1.7 Specification summary

The 34K core is provided as a synthesizable package, and customers have considerable freedom to customize it. But all 34K cores share these:

- *CPU architecture*: compliant to Release 2 of the MIPS32 Architecture [MIPS32].

- *Multi-threading*: as defined by the Multithreading extension to the MIPS32 architecture as specified by [MIPSMT].

The 34K core can be synthesized to be able to run nine concurrent threads (9 TCs) in up to two "virtual processors" (2 VPEs).

It may be equipped with a bank of *Inter-Thread Communication storage (ITC)* locations, following the recommendations of [MIPSMT].

• DSP-orientated instruction set: it implements the DSP extension to the MIPS32 architecture, see [MIPSDSP].

- MIPS16e<sup>TM</sup>: the 16-bit instruction set option for compact code, see [MIPS16e].

- 8-9-stage pipeline<sup>2</sup>: a sophisticated branch prediction unit keeps the CPU efficient, even when it's only running one thread.

- Separate I- and D-caches: 4-way set associative. The SoC designer may choose from 8, 16, 32 or 64Kbytes size for each cache (and can even omit either cache). Parity checking in the cache is optional.

Caches are non-blocking, and both allow for hit-under-miss and miss-under-miss - the I-cache uses that to allow a cache-hitting thread to continue even though an I-cache refill is pending for some other thread.

The D-cache is write-back (memory regions may also be configured as write-through and a special "uncached accelerated" write mode). You can lock data into the caches.

• *OCP system interface*: industry-standard interconnect.

## SoC Builder's Optional features

Some features are provided only at the option of the SoC integrator, and may depend on separate licensed material from MIPS Technologies:

- L2 (secondary) cache: you can configure your 34K core with MIPS Technologies' L2 cache between 128Kbyte

and 1Mbyte in size. Full details are in [L2CACHE], but programming information is in Section 5.4 "Caches" of

this manual.

- *CorExtend*<sup>TM</sup> *user-defined instructions*: the 34K Pro Series<sup>TM</sup> core family allows you to add custom instructions as described in [CorExtend].

- Floating point unit: fitted to 34Kf<sup>TM</sup> cores, with 32 full 64-bit floating point registers.

- Fixed mapping MMU: reduces core size when a TLB is not required.

- Instruction- or data-side "scratchpad" memory: each can be up to 1Mbyte of high-performance on-chip memory, which can be dual-ported to the OCP interface for "push" I/O architectures.

- EJTAG debug unit: on-chip debug resources, summarized in Section 10.1, "EJTAG on-chip debug unit".

- Power-management options: summed up in Section 7.5, "Saving Power" below.

- *OCP L2 extensions*: to allow front-side L2 cache.

Refer to [INTGUIDE] for full details about the options.

# 1.8 Pipeline and implementation

In programming documents about MIPS Technologies cores you'd usually find a section which describes the pipeline, at least at a broad level useful for programmers. With the 34K core that is hard to describe without knowing something about multi-threading so we've moved it to Section 3.1, "The 34KTM core pipeline and multithreading" below.

<sup>2.</sup> Single TC configurations enable a bypass of a thread selection stage to get down to 8 stages, otherwise it'll be 9. When executing MIPS16e instructions, it'll be 11 stages

1.8 Pipeline and implementation

# The MIPS® MT ASE - Multithreading the RISC way

We use "MT" for "multi-threading". So what does a MIPS architecture CPU do to run multiple threads concurrently? That question is one about "architecture" - the corresponding "how does the 34K core run multiple threads?" question is about implementation, and is answered below in Chapter 3, "How the 34KTM core implements multi-threading" on page 41.

#### In this chapter:

- Section 2.1, "What's a thread and its context?": basic definitions.

- Section 2.2, "Why multi-threading?": motivation.

- Section 2.3, "Different kinds of multi-threading: TCs and VPEs": we offer two levels of multi-threading in one CPU

- Section 2.4, "When can't threads run?": and what they're doing when stopped.

- Section 2.5, "Thread-scheduling decisions and the policy manager": what happens and what influence can you

have.

- Section 2.6, "Multithreading, exceptions and interrupts": interrupts and other exceptions in the MIPS MT CPU.

- Section 2.7, "Multithreading, non-blocking loads and stores, and gating storage"

- Section 2.8, "MIPS® Multithreading ASE new instructions"

- Section 2.9, "Multithreading ASE CP0 (privileged) registers": understanding multi-threading in fine detail.

#### Why multi-threading takes a lot of thinking about

Any form of concurrency makes your head hurt. Our brains are doubtless extremely parallel: we can talk on a cell-phone and drive with only a 50% increase in our chance of crashing. But our ability to reason correctly is distinctly sequential, and so far we have not bred a race of super-kids who can write explicitly parallel software.

Multi-tasking software has been successfully understood by dividing it into sequential chunks ("threads", though a more precise definition follows) which communicate and synchronize with each other only in carefully controlled ways. You can then unleash a flock of threads and allow them to evolve separately. Programmers find it almost impossible to keep track of what every thread is doing at any one time - but with simple-enough rules about the interactions, the system will still work.

The multithreading CPU pushes thread concurrency down to the hardware level, so you should expect to find it somewhat mystifying from time to time. To really understand multi-threading and the 34K core you need to be able to switch between a software-orientated threads-eye-view (where threads are internally sequenced and other threads are happening somewhere else) and a hardware engineers CPUs-eye-view (where everything happens in sequence along

the pipeline). This is difficult, but we hope not impossible. This chapter takes the "thread" viewpoint, and the next chapter stays closer to the hardware.

## 2.1 What's a thread and its context?

There are a couple of critical phrases and acronyms which it's useful to define carefully before we start:

Thread: a set of computer instructions read and activated in their programmed order.

Operating systems most often use the word "thread" specifically for application-software visible threads scheduled by the OS. But our wider definition means that any piece of software must have at least one thread.

By this definition something like an interrupt handler (which is not reached as a result of normal program flow) counts as a thread in its own right. This more general definition of "thread" seems to be a more logical starting point for describing multi-threading hardware.

- Thread context: you might want to consider the complete state of a running thread, enough so you could restart it successfully. But for our purposes we're particularly interested in the part of the state which gets stored inside the CPU what [MIPSMT] calls the "thread context". The thread context always (of course) includes the Program Counter (PC) and the general-purpose registers. There are some good justifications for narrowing our focus down to the state held in the CPU:

- 1. We don't need to encompass the thread's data stored in memory, because we know how to share memory already (for OS-defined threads, for example);

- 2. We don't include state which is inherently inaccessible to this particular instruction stream so kernel-only readable CP0 registers are invisible to a user-privilege thread;

- 3. We don't include state which is logically unnecessary, and just kept for efficiency for example, cache contents, which generally make no difference to the underlying memory image.

With this definition, what is included in the thread context varies according to what sort of software is running. For a Linux interrupt handler on a conventional MIPS architecture CPU the CPO registers are part of the thread state, but for a Linux application thread they're not visible.

You could have found the definitions of *Thread* and *Thread context* in Appendix B, "Glossary" on page 175 below. Any word or phrase in blue (or slightly faint in real black-and-white print) is probably explained. If you're reading online and it's blue, it will link to its definition: try it.

# 2.2 Why multi-threading?

Traditionally, a CPU only held one thread's context (one PC, one set of registers). Operating systems providing multiple threads held all the state for the non-running threads in OS-specific data structures.

But MIPS MT CPUs are equipped with more than one PC and register set so they can hold more than one thread's context.

There's more than one reason why you might want to build a multithreading CPU. For MIPS MT the main motivation is to build a CPU which can continue to do useful work when some computation is held up for a period of a few to some hundreds of CPU cycles - typical of cache misses and some other interactions in embedded systems. Such a hold-up is too short to allow an OS to borrow the CPU to do something else (the OS thread-switch overhead is itself

probably 100 cycles or more). But in many workloads such hold-ups are frequent enough that the CPU spends half its time waiting for data.

A multithreading CPU can keep other threads making progress when one thread is held up. If (as is commonly the case these days) the real workload is already split into multiple threads, that can turn into extra application performance without modifying application code.

The extra thread state storage (mostly the register file) only represents a fraction of the gate count of a CPU, so this extra performance has cost only a small increment in area and complexity. That's why in 2005 everyone wants to do multithreading.

## 2.3 Different kinds of multi-threading: TCs and VPEs

In some ways the simplest thing to do is to replicate every software-visible piece of CPU state. Then your multi-threading CPU will look pretty much like two CPUs which happen to share memory, creating a "virtual multiprocessor" (*VSMP*). That's what Intel's newer multithreading x86 processors do; you can drop a Linux kernel designed for a two-way multiprocessor onto such a CPU and it just works. It's an easy way to get a software market for a new technology.

But performance-critical embedded applications are those where the multithreading is an explicit part of the system design - we'll call it "explicit multithreading" or *EMT*. EMT is new, so we don't need to offer backward compatibility. An EMT application does not need the whole CPU replicated; it can manage with what is visible to user-level programs - the PC, GPRs and a little more.

The original and ingenious trick in the MIPS MT architecture is that you have a choice of either model, and can even do both in the same CPU at the same time. So a MIPS MT CPU has multiple *TC*s (the acronym started out as *Thread context*), but also provides for more than one *VPE* ("VPE" started out as a *Virtual Processing Element*.) A TC provides the minimum required to do explicit multithreading, while one or more TCs with their own VPE really look like an independent CPU, enough to provide a congenial home for software which doesn't really want to know about MIPS MT - perhaps even a non-MT-aware legacy operating system.

#### 2.3.1 How an MT CPU's hardware uses TCs and VPEs

Each instruction being run by an MT CPU has a TC number. Whenever the instruction accesses some state - reads or writes a general-purpose register, for example - it uses its TC number to extend the register-number field which is already defined inside the instruction. An instruction sees a different set of registers depending on the TC number: it's very simple, and it just works.

It's not quite that simple on a MIPS architecture CPU, because of the TC/VPE trick mentioned above. So this instruction might be for TC #5 (it uses general purpose registers from the fifth bank) but VPE #1 (it gets most of its CP0 registers from the first bank). Again, this should just work. What's more complicated, of course, is to get those CPU resources working which can't simply be reduced to registers. But that's not architecture, it's implementation, and described in Chapter 3, "How the 34K<sup>TM</sup> core implements multi-threading" on page 41 below.

## 2.3.2 CPU resources and registers shared between all threads

Many of the CPU's resources are not replicated for MIPS MT, just used by whichever TC is identified by the instruction accessing the resource. They include:

• *Caches*: the cache's contents are just like memory (only faster) and unproblematic. On a CISC CPU the cache is usually completely invisible to running software, and there's no issue at all about multiple threads - but MIPS architecture CPUs generally need the OS to intervene in the caches at some points.

The MIPS MT ASE requires that the writeback and invalidate **cache** instructions used by real OS' when running are multi-threading safe. Cache manipulations may be independently mixed by two VPEs<sup>3</sup> without immediate harm; even if one VPE invalidates a cache entry from right under the feet of another one, everything should keep working - the consuming VPE will either get the old copy (which it was happy with) or cache-miss and pull in a new one (which should be just the same data).

However, arbitrary re-initialization of a cache already in use by another VPE will not be safe; writeback data could be lost. Programs running on separate VPEs would probably be well-advised to get cache initialization done by a thread running alone before other VPEs are enabled.

With a multithreading workload, cache performance could suffer; multiple threads will probably produce a larger and more diverse "working set" of active memory regions. However, a cache works well (or not) when optimizing repeated accesses over spans of code executing hundreds of thousands to millions of instructions. During that time which even a single-threaded workload will climb all over application and OS space. The 34K core's caches are already 4-way set associative, which should be enough to minimize misses caused by overlapping hot-spots of several concurrent threads. Our measurements to date back that up.

- Main pipeline: each of the 34K core's main pipeline stages just serve the TC associated with the current instruction. No problem.

- *The TLB (sometimes)*: the MIPS MT ASE allows the TLB entries to be shared between all VPEs, or partitioned between VPEs. The 34K core can be configured to do either (to share the TLB, set MVPControl[STLB] to 1.)

If the TLB is not shared, it is partitioned by hardware so each VPE sees its own independent array of entries.

When the TLB is shared, there's a problem of managing concurrent access by the two VPEs. It's up to OS software to control concurrent access by OS maintenance routines. But that still leaves the risk that one VPE's maintenance software will collide with another VPE's TLB refill exception handler: see Section 4.3.4, "Sharing and not sharing the TLB" for how that's avoided.

• Basic configuration registers: in a highly adaptable design like the 34K core the initialization software needs to know the full resource complement of the CPU, or it can't know how to share it between the VPEs.

The registers MVPControl and MVPConf0-1 allow software to see what resources are provided CPU-wide, and these registers are not replicated per-VPE.

• *Performance counters*: since these are infrequently used, but it's valuable to have as many as possible available, the four registers are shared between both VPEs.

This is more implementation than architecture, but some software-invisible resources are also shared. Notably, the 34K core's "branch history table" (BHT) in the instruction fetch unit is shared. That seems quite wrong: the branch histories of different threads are certainly likely to be different. But the BHT was only statistically correct anyway; the branch history is only recorded in entries indexed by some modest number of low virtual address bits. Even in a conventional single-thread CPU, different branches could map onto the same entry and cause confusion (and thus

<sup>3.</sup> The CP0 registers used with the **cache** instruction are only replicated per-VPE, so EMT code must take care to avoid re-entry into cache management functions by other threads.

lower the prediction accuracy) - but there are enough different entries that this relatively rarely happens. Having multiple threads doesn't really make it much worse, and the BHT should continue to perform well in typical applications.

## 2.3.3 CPU resources and registers replicated per-TC

Some state needs to be independently kept for each TC, including:

- Program counter and general purpose (integer) registers: the TC's program counter can be seen and adjusted (when the TC is halted, otherwise it's a moving target) in TCRestart. The architecture does not define what you'll get if you read your own TCRestart; probably some "historical value".

- Each TC, of course, has its own set of 32 general purpose registers. It also needs its own copies of the accumulator registers in the multiply-divide unit (*hi/lo*), and the extra accumulator registers and control register provided as part of the DSP ASE described in Chapter 9, "The MIPS32® DSP ASE" on page 123.

- Privilege state: some TCs (sharing a VPE) may be in the kernel while others are running user-mode software. So

each TC has its own copy of the user-mode/kernel-mode flags Status[KSU]. TCStatus[TKSU] provides a convenient per-TC view of the same flags. Each TC gets a copy of the TCContext register too: it has no hardware significance, but provides a useful scratch register for the OS to keep some key thread identifier.

- Address space: we don't want to insist that all TCs which share a VPE must execute in the same address space. Different address spaces in MIPS architecture CPUs are managed by only returning TLB translations for virtual addresses when they're presented together with the right "ASID" value, an arbitrary 8-bit token held in EntryHi[ASID] while the system runs.

- So each TC also has its own copy of the EntryHi[ASID] field the same field is accessible as TCStatus[TASID].

- Access to co-processors: the 34K core's FPU when fitted is built with just one set of registers. That makes sense because the registers in the floating point unit already occupy a lot of logic space, and the 1-register-set FPU design is identical to that used in the 24K<sup>TM</sup> core family. But it means that the FPU can't be used by multiple concurrent threads.

- Some other co-processors might have one set of data registers per TC, supporting arbitrary multi-threading.

- In the MIPS architecture you can't use any co-processor unless you first turn on the corresponding *Status[CUx]* bit in the status register. MIPS MT uses that to provide a mechanism to share the co-processors, detailed in the notes to Figure 2.2 below. As part of that mechanism the *Status[CU3-1]* bits are also visible at *TCStatus[TCU3-1]*.

- Which VPE we're using: a TC must know which VPE is belongs to, or it can't get at the right copy of the per-VPE registers. The VPE affiliation is readable and writable in TCBind[CurVPE]. (Each VPE also has a distinct number readable at EBase[CPUNum], to allow seamless use of multi-CPU software on multiple VPEs.)

- *TC halted*: think of this as "TC anesthetized" it stops the TC from wriggling around when under surgery, or even just close inspection. It occupies its own 1-bit register *TCHalt* so it can be set and cleared atomically.

- While this is set the TC is frozen: won't run, can't be picked by **fork**. The architecture abhors the idea of a halted thread being half-way through a synchronization access, and any pending load/store to *Gating Storage* will be rolled back when this bit is set. From a hardware point of view the gating storage access is aborted; but unless you do something special to stop it the access will be quietly retried once the OS is finished with its maintenance and clears *TCHalt*.

- *TC interrupt-exempt*: set *TCStatus[IXMT]* to mean this TC will never be picked to handle an interrupt exception (even if that means the interrupt is completely ignored).

- *Per-TC flags*: there are also bits to control the ability of **fork** to seize a "free" TC and make it run a new thread, and for other purposes. See the description of **fork** in Section 2.8, "MIPS® Multithreading ASE new instructions" and the notes on Figure 2.2.

- *Debug state*: the single-step bit *Debug[SSt]* is replicated per-TC, for fine debugger control. The debugger is also given a control bit *Debug[OffLine]* which it can use to prevent TCs other than the one under debug from springing into life during single-step or when running a thread to the next breakpoint.

## 2.3.4 CPU resources and registers replicated per-VPE

We want a TC running alone in a VPE to be a MIPS32-compliant processor in its own right, so each VPE replicates all the CPO registers required by release 2 of the MIPS32 specification (a few read-only registers are in fact shared between VPEs on the same CPU, but they're read-only, so who's to know?)

So what is replicated?

- State related to exceptions: MIPS architecture experts will recall that you enter exception mode by taking an exception, and remain in it until you either return with an **eret** or (more common in a complicated OS) you carefully clean up exception-dependent information and then manually clear Status[EXL].

- The MIPS MT architects determined that only one TC from a VPE is allowed to be in exception mode at any one time when one TC takes the exception, its VPE siblings are suspended until the first TC clears *Status[EXL]*. To do otherwise would require a lot of extra replicated state, and would lead to some nasty concurrency hazards.

- *Interrupt system and interrupts*: interrupt signals to the chip are wired to VPEs separately (a reasonable strategy may be to wire all the VPEs in parallel to the same inputs, but that's an SoC designer's decision).

- The interrupt management fields in the Cause and Status registers are all per-VPE.

- Cache management registers: all the cache operation staging registers are per-VPE. In fact, most of the CP0 registers are per-VPE.

- *The TLB (sometimes)*: on the 34K core the TLB may either be shared, or partitioned invisibly so that two VPEs each think they have their own dedicated chunk of the TLB<sup>4</sup>.

- The EJTAG debug unit: the physical unit may or may not be replicated, but the registers in its CP0 software interface (DEPC, DESAVE and Debug) are replicated per-VPE.

In debug mode all TCs other than the one running the debugger are suspended, regardless of VPE affiliation. Moreover, the TC in debug mode continues to run even if it is otherwise marked as halted, not-allocated etc. More details in Section 10.1.2, "Debug mode".

## 2.4 When can't threads run?

A CPU can be compliant to the MIPS MT ASE without being committed to any particular thread-scheduling algorithm - the decision as to which thread's instruction to pick next is implementation-dependent. But that level of abstraction is difficult, so let's make some working assumptions - which will, happily, turn out to be correct for the 34K core.

<sup>4.</sup> The amount of the TLB awarded to each VPE is configurable when your core is synthesized. Ask your hardware engineer.

#### The MIPS® MT ASE - Multithreading the RISC way

Some implementations permit customizable hardware outside of the core to influence the CPU to favor one TC over another when deciding what instruction to run next; see Section 2.5, "Thread-scheduling decisions and the policy manager" below.

But before worrying about that, let's look at something simpler. A practical CPU might run instructions in turn ("round-robin") from each live thread. But what about that weasel word "live"? When can a thread *not* make progress? Well, it can be:

- Waiting for memory data: most often, to resolve a cache miss (for of the order of 50 cycles) making use of this idle time is the first motivation for contemporary multithreading.

- Or this might also be an uncached read of some device-register data (of the order of 100-500 cycles) particularly relevant to embedded applications.

- Blocked on read/write "gating storage": we envisage that multithreading applications are likely to use special memory locations where the wait-for-transfer is used as a deliberate way of matching the speed of the software to the arrival of data either from other threads, or some direct hardware source/sink. Waits of this kind may extend for thousands of cycles. So the MIPS MT ASE describes how some memory locations are accessed according to special rules which make them Gating Storage, and describes a particular application of gating storage to optional ITC locations. See Section 3.3, "Inter-thread communication storage (ITC)" for the facility provided by the 34K core.

- Blocked on an "interrupt-like" external signal: a thread which waits for a particular hardware signal is an obvious multithreading analogue of an interrupt handler, and likely to be useful. You'll see how the MIPS MT yield instruction can be used for that purpose.

- *Halted closed for maintenance*: there are bound to be things the OS wants to do with TCs which can't be done while it's live, and each TC comes with a "Halt" button in the *TCHalt* register.

- Not "allocated": the MT system includes the **fork** instruction, which provides a very lightweight way of starting a new thread potentially, it's even usable from user-mode in a protected OS. An OS obviously can't simply relinquish control of thread scheduling, but it can arrange to provide a pool of "free" threads which **fork** can use they're a bit like taxis waiting at a taxi-rank for customers. The TCs "at the rank" are prevented from running code by having their TCStatus[A] ("allocated") bit clear. If a system doesn't use **fork**, then it must take care to set the allocated bit explicitly on any TC which is to run.

- Affiliated to an unactivated VPE: that is, one with VPEConf0[VPA] zero.

- Asleep after executing a wait instruction: in which case it won't awake until its VPE gets an interrupt (it doesn't matter which TC runs the interrupt code, all TCs are woken from their sleep).

- Suspended temporarily inhibited to avoid some concurrency problem: for example we'll see that a VPE becomes "single-threaded" while it is handling exceptions, so that implicitly suspends all the VPE's other TCs. OS software can achieve a similar effect using instructions such as dmt (stop all other threads with the same VPE affiliation) and dvpe (stop all other threads, even in different VPEs).

- "Offlined" by a debugger: using Debug[OffLine], typically so the debugger can isolate another thread for test.

In this manual we'll try to consistently use the word *stopped* for a thread subject to any of the conditions above - and by analogy, we'll use the same adjective to describe the TC which is executing the thread. The opposite of "stopped" is *live*.

We'll distinguish a stopped thread as either:

- *Stalled*: waiting for a condition which could be experienced by a program on a single-threaded CPU that includes waiting for data from a cache miss or an uncached read, OR:

- *Blocked*: waiting for something other than the above. That's some deliberate multithreading synchronization by **yield**, a gating storage read, or explicitly stopped as a result of software activity.

The blocked state is new with MIPS MT. The nearest thing that a thread on a non-MT MIPS CPU can come to "blocked" is when the CPU is asleep after executing wait.

For blocked threads we'll use *halted*, *suspended* and *asleep* in the specific senses above. The use of these terms is compatible with the formal specification [MIPSMT], though that uses *running* to instead of live. In the formal specification "running" means either live or waiting for a normal read/write.

Regardless of why a thread is stopped:

- *The CPU*: will be interested in issuing instructions from some other live thread. In a simple pipelined CPU, that may involve discarding some instructions from the stopped thread, if they've already entered the main pipeline.

- The OS: may be interested in taking control when a thread is blocked for a long time the TC could be in principle given another thread which might be able to make more progress. The OS overhead in changing the TC to another thread really the same job as a thread-switch on a conventional CPU is likely to be more than 100 instructions so the OS should only do this when the thread is likely to remain stopped for many hundreds of cycles.

But it's important that the OS has the power to take a blocked thread and detach it from its TC cleanly, so it can be restarted. That motivates some of the key features of the architecture, including the details of *Gating Storage*, see Section 2.7.1, "Gating storage".

# 2.5 Thread-scheduling decisions and the policy manager

The MIPS MT architecture is agnostic about thread scheduling. The immediate choice of which thread to run next is made inside the core; in the absence of any directions to the contrary, this choice is required to be fair to TCs in the long run.

However, in MIPS Technologies cores we envisage a rather dumb in-core scheduler given long-term hints by a *Policy Manager (PM)* which, living outside the core, may be customized for specific applications.

In particular the *TCSchedule* and *VPESchedule* registers (if implemented at all) will typically be inside the policy manager block; so what they do is strictly implementation-dependent.

The way the in-core scheduler in the 34K core works is described in Section 3.2.1, "How the Dispatch Scheduler Works", and the choice of policy managers available from MIPS Technologies is in Section 3.2.3, "MIPS Policy managers included with the 34K' core family".

# 2.6 Multithreading, exceptions and interrupts