# MIPS® BusBridge<sup>™</sup> 3 Modules User's Manual

Document Number: MD00660 Revision 02.02 April 17, 2014 Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Tech, LLC, a Wave Computing company ("MIPS") and MIPS' affiliates as applicable. Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS or MIPS' affiliates as applicable or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines. Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS (AND MIPS' AFFILIATES AS APPLICABLE) reserve the right to change the information contained in this document to improve function, design or otherwise.

MIPS and MIPS' affiliates do not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS, MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPSr3, MIPS32, MIPS64, microMIPS32, microMIPS64, MIPS-3D, MIPS16, MIPS16e, MIPS-Based, MIPSsim, MIPSpro, MIPS-VERIFIED, Aptiv logo, microAptiv logo, interAptiv logo, microMIPS logo, MIPS Technologies logo, MIPS-VERIFIED logo, proAptiv logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, M14K, 5K, 5Kc, 5Kf, 24K, 24Kc, 24Kf, 24KE, 24KEc, 24KEf, 34K, 34Kc, 34Kf, 74K, 74Kc, 74Kf, 1004K, 1004Kc, 1004Kf, 1074K, 1074Kc, 1074Kf, R3000, R4000, R5000, Aptiv, ASMACRO, Atlas, "At the core of the user experience.", BusBridge, Bus Navigator, CLAM, CorExtend, CoreFPGA, CoreLV, EC, FPGA View, FS2, FS2 FIRST SILICON SOLUTIONS logo, FS2 NAVIGATOR, HyperDebug, HyperJTAG, IASim, iFlowtrace, interAptiv, JALGO, Logic Navigator, Malta, MDMX, MED, MGB, microAptiv, microMIPS, Navigator, OCI, PDtrace, the Pipeline, proAptiv, Pro Series, SEAD-3, SmartMIPS, SOC-it, and YAMON are trademarks or registered trademarks of MIPS and MIPS' affiliates as applicable in the United States and other countries.

All other trademarks referred to herein are the property of their respective owners.

| <br><sup></sup> U¢ao """ | Ū. | У | Ū | ĸ |  |

|--------------------------|----|---|---|---|--|

## **Table of Contents**

| Chapter 1: Introduction                                          | 9  |

|------------------------------------------------------------------|----|

| 1.1: Features                                                    | 9  |

| 1.1.1: OCP2AXI Bridge (OCP-AXI)                                  | 9  |

| 1.1.2: OCP Splitter (OCP-SPL)                                    |    |

| 1.1.3: AXI-to-OCP Bridge (AXI-OCP)                               |    |

| 1.2: OCP-AXI and AXI-OCP Usage                                   |    |

| 1.2.1: MIPS32® Core                                              |    |

| 1.2.2: MIPS32 Core with SOC-it L2                                |    |

| 1.2.3: 1004K Coherent Processing System AXI Bridge Configuration |    |

| 1.3: OCP-SPL Usage                                               |    |

| Chapter 2: Installation                                          | 17 |

| 2.1: Tool Assumptions                                            |    |

| 2.1.1: General Tool Requirements                                 |    |

| 2.1.2: Supported EDA Tools                                       |    |

| 2.1.3: Supported Tool Versions.                                  |    |

| 2.1.4: Synopsys Verification IP Version (VIP)                    |    |

| 2.2: Installing a Release                                        |    |

| 2.2.1: Unpacking Release Deliverables                            |    |

| 2.2.2: Release Naming Convention                                 |    |

| 2.2.3: Configuring Perl Scripts                                  |    |

| 2.2.4: Creating a Project Area                                   |    |

| 2.2.5: Environment Variable Setup                                |    |

| 2.2.6: Path Setup                                                |    |

| 2.2.7: Welcome! - The Place to Start                             |    |

| 2.2.8: Verifying the Release                                     |    |

| 2.3: Directory Structure of the Deliverables                     |    |

| 2.3.1: \$MIPS_HOME/\$MIPS_CORE Directory Tree                    |    |

| 2.3.2: \$MIPS_PROJECT Directory Tree                             |    |

| Chapter 3: Functional Descriptions                               | 31 |

| 3.1: OCP-AXI Functional Description                              |    |

| 3.1.1: Functional Block Diagram                                  |    |

| 3.1.2: Output Ports                                              |    |

| 3.1.3: Pending Read Buffer                                       |    |

| 3.1.4: Pending Write Buffer                                      |    |

| 3.1.5: OCP 2.1 to AXI 1.0 Map Block                              |    |

| 3.1.6: Special Topics                                            |    |

| 3.2: OCP-SPL Functional Description                              |    |

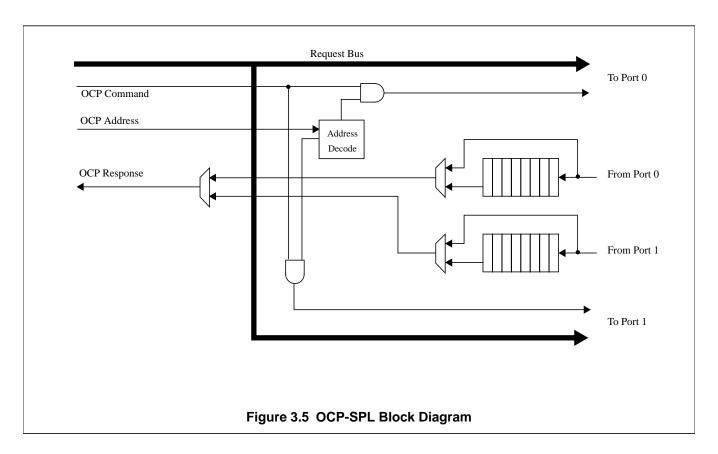

| 3.2.1: OCP-SPL Block Diagram                                     |    |

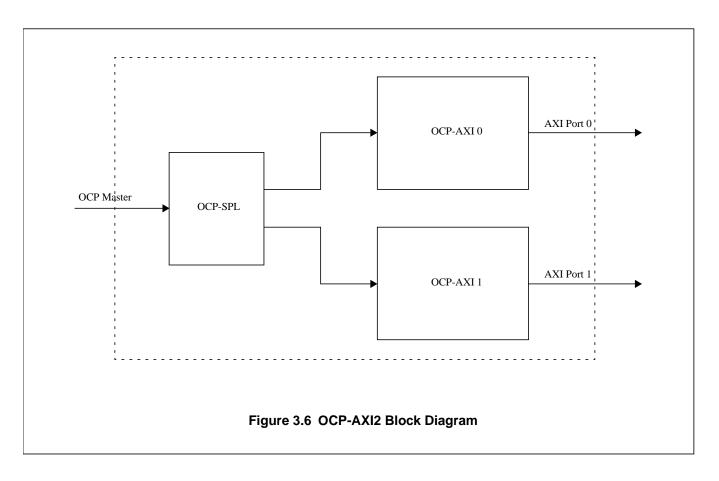

| 3.3: OCP-AXI2 Functional Description                             |    |

| 3.3.1: OCP-AXI2 Block Diagram                                    |    |

| 3.3.2: OCP-AXI2 Configuration                                    |    |

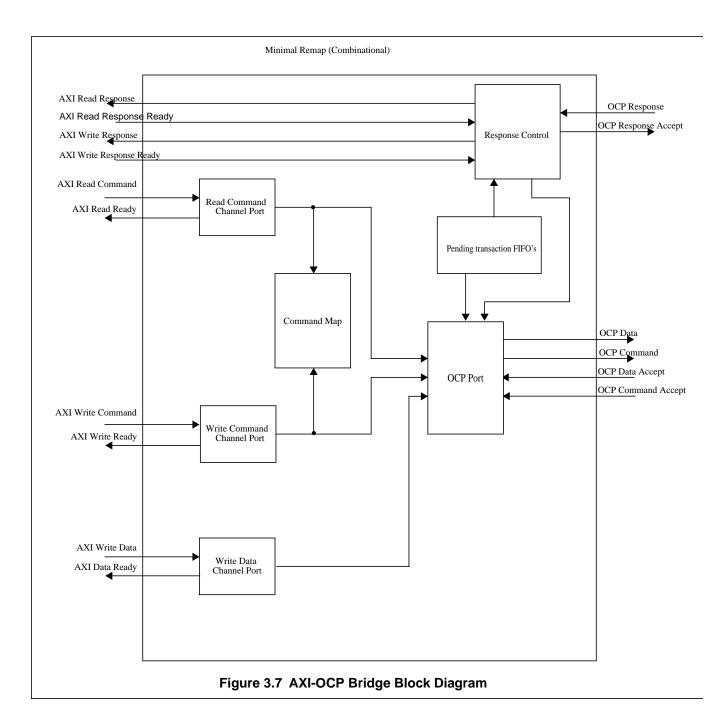

| 3.4: AXI-OCP Functional Description                              |    |

| 3.4.1: AXI Command and Data Ports                                |    |

| 3.4.2: AXI Command Map                                           |    |

| 3.4.3: OCP Port                                                  |    |

|                                                                  |    |

| 3.4.4: Pending Transaction FIFO                         |    |

|---------------------------------------------------------|----|

| 3.4.5: Response Control                                 |    |

| 3.4.6: AXI-OCP Bridge Latency                           |    |

| 3.4.7: AXI Slave Interface Requirements                 |    |

| 3.4.8: Sideband Signals                                 |    |

| 5                                                       |    |

| Chapter 4: Clocking and Reset Methodology               | 57 |

| 4.1: Clocking Methodology                               |    |

| 4.1: Clock Domains                                      |    |

|                                                         |    |

| 4.3: Clock Gating                                       |    |

| 4.3.1: Standard Clock Gating Circuit                    |    |

| 4.3.2: Fine-Grain Clock Gating of Conditional Registers |    |

| 4.4: Reset                                              |    |

| 4.4.1: OCP-AXI                                          |    |

| 4.4.2: AXI-OCP                                          |    |

|                                                         |    |

| Chapter 5: Functional Verification                      |    |

| 5.1: Verification Overview                              |    |

| 5.2: Running Simulations                                |    |

| 5.2.1: General Simulation Setup                         |    |

| 5.2.2: Simulation Setup for Synopsys VCS                |    |

| 5.2.3: Creating the Simulation Executable               |    |

| 5.2.4: Running Random Tests                             |    |

| 5.3: Debugging Simulation Runs                          |    |

| 5.3.1: Result Files                                     |    |

| 5.4: Creating New Templates                             |    |

| 5.4.1: Template Files                                   |    |

| •                                                       |    |

| Chapter 6: Waveforms                                    | 73 |

| 6.1: OCP-AXI Bridge Waveforms                           |    |

| 6.1.1: Single Read Command                              |    |

| 6.1.2: Burst Read Command                               |    |

| 6.1.3: Read Command with Wait States                    |    |

| 6.1.4: Single Write Command                             |    |

| 6.1.5: Burst Write Command                              |    |

| 6.1.6: Write Command with Wait States                   |    |

| 6.2: AXI-OCP Bridge Waveforms                           |    |

|                                                         |    |

| 6.2.1: Single Read                                      |    |

| 6.2.2: Burst Read with AXI Master Wait States           |    |

| 6.2.3: Single Write Command                             |    |

| 6.2.4: Burst Write with Wait States                     |    |

|                                                         |    |

| Chapter 7: Synthesis                                    |    |

| 7.1: Methodology                                        |    |

| 7.2: Flow File Structure                                |    |

| 7.3: Synthesis                                          |    |

| 7.3.1: Preparing for Synthesis                          |    |

| 7.3.2: Running Synthesis                                |    |

| Chapter 8: Port Definitions                             |    |

| 8.1: Naming Conventions                                 |    |

| 8.1.1: Signal Direction                                 |    |

|                                                         |    |

| 8.2: OCP-AXI Detailed Signal Descriptions  |  |

|--------------------------------------------|--|

| 8.3: OCP-SPL Detailed Signal Descriptions  |  |

| 8.4: OCP-AXI2 Detailed Signal Descriptions |  |

| 8.5: AXI-OCP Detailed Signal Descriptions  |  |

|                                            |  |

| Appendix A: References                     |  |

|                                            |  |

| Appendix B: Revision History               |  |

## **List of Figures**

| Figure 1.1: MIPS32® Core Connection                                          |  |

|------------------------------------------------------------------------------|--|

| Figure 1.2: MIPS32® Core with SOC-it® L2 connection                          |  |

| Figure 1.3: MIPS32® 1004K <sup>™</sup> Coherent Processing System connection |  |

| Figure 2.1: Directory Structure of the Bus Bridge 3 Modules                  |  |

| Figure 3.1: OCP-AXI Bridge Block Diagram                                     |  |

| Figure 3.2: Output Port Diagram                                              |  |

| Figure 3.3: Pending Read Buffer                                              |  |

| Figure 3.4: Pending Write Buffer                                             |  |

| Figure 3.5: OCP-SPL Block Diagram                                            |  |

| Figure 3.6: OCP-AXI2 Block Diagram                                           |  |

| Figure 3.7: AXI-OCP Bridge Block Diagram                                     |  |

| Figure 3.8: Input Port Diagram                                               |  |

| Figure 3.9: ARSIDEBAND/AWSIDEBAND Format                                     |  |

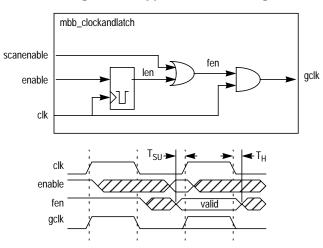

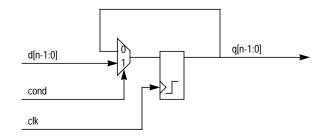

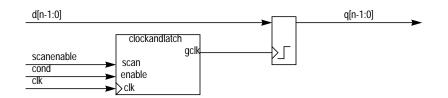

| Figure 4.1: Typical Clock Gating Circuit                                     |  |

| Figure 4.2: Conditional Register Implementation Without Gated Clocks         |  |

| Figure 4.3: Conditional Register Implementation With Gated Clocks            |  |

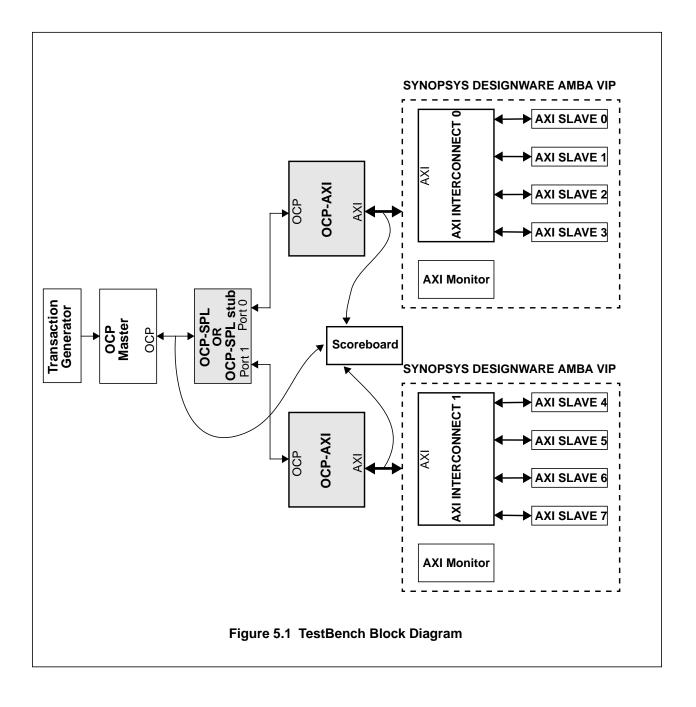

| Figure 5.1: TestBench Block Diagram                                          |  |

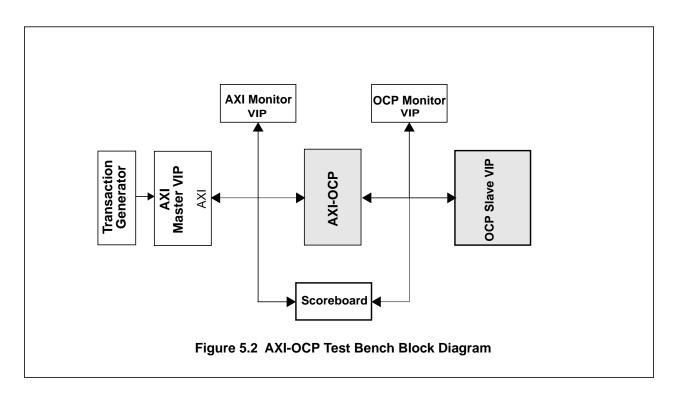

| Figure 5.2: AXI-OCP Test Bench Block Diagram                                 |  |

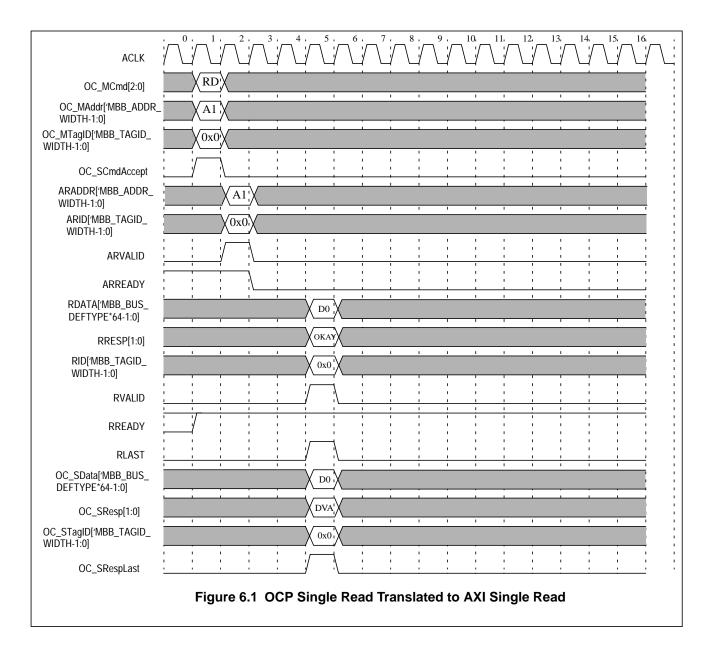

| Figure 6.1: OCP Single Read Translated to AXI Single Read                    |  |

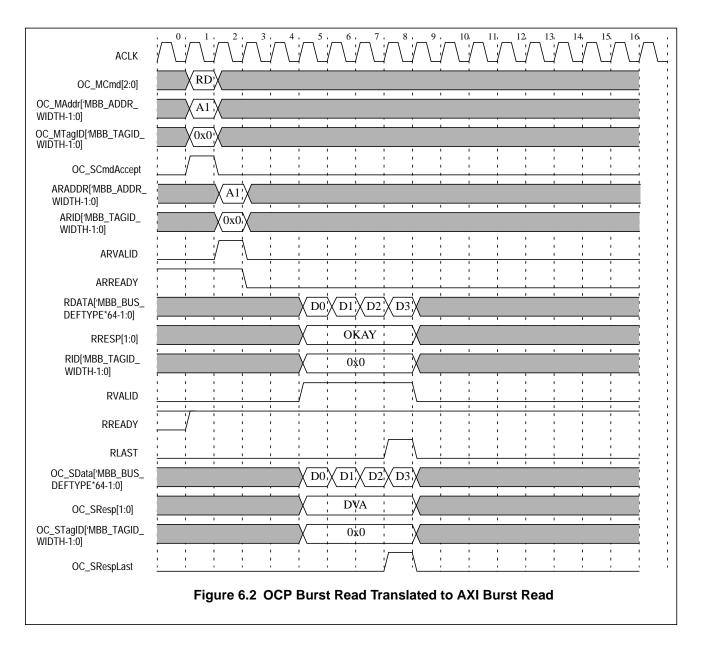

| Figure 6.2: OCP Burst Read Translated to AXI Burst Read                      |  |

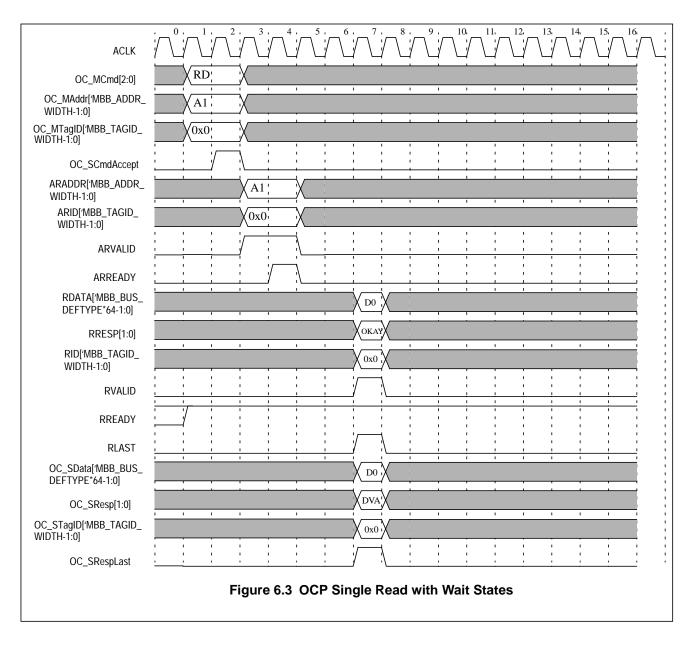

| Figure 6.3: OCP Single Read with Wait States                                 |  |

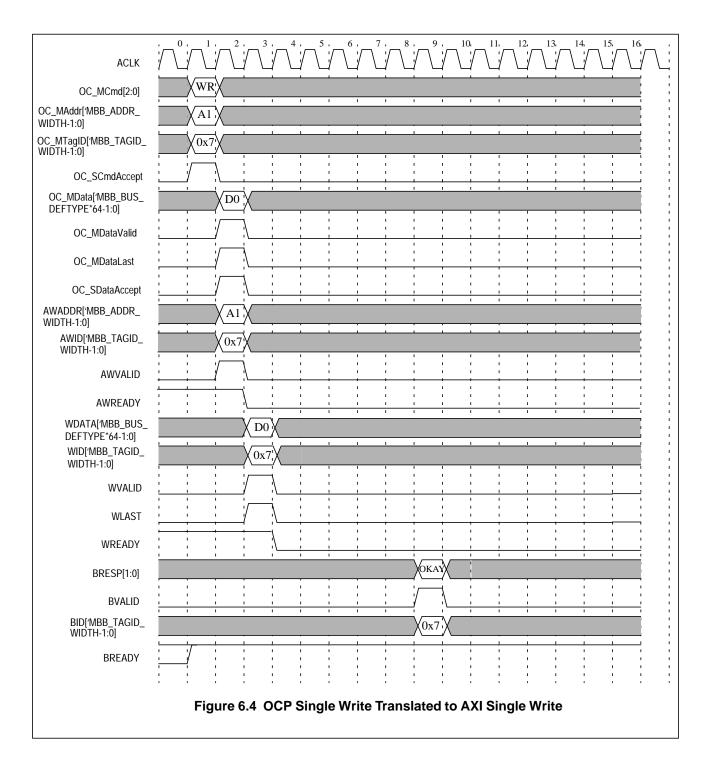

| Figure 6.4: OCP Single Write Translated to AXI Single Write                  |  |

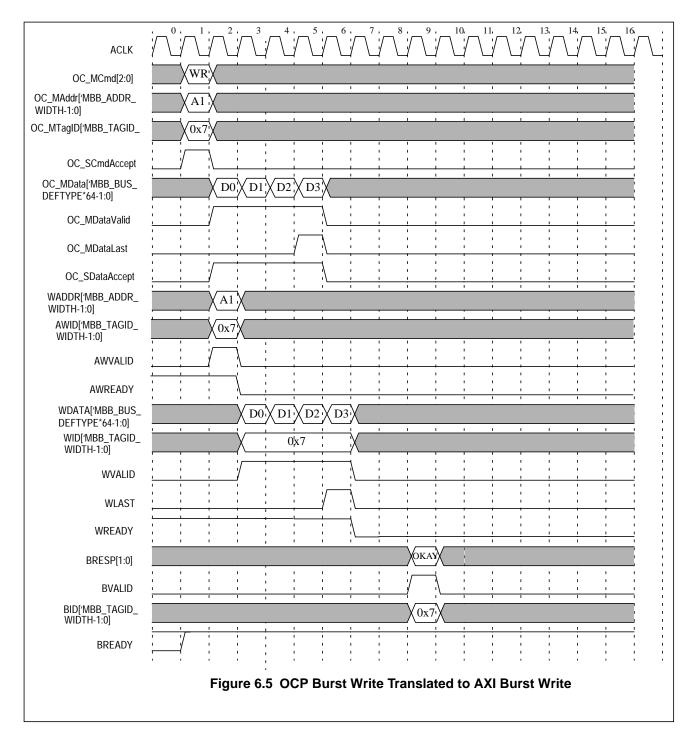

| Figure 6.5: OCP Burst Write Translated to AXI Burst Write                    |  |

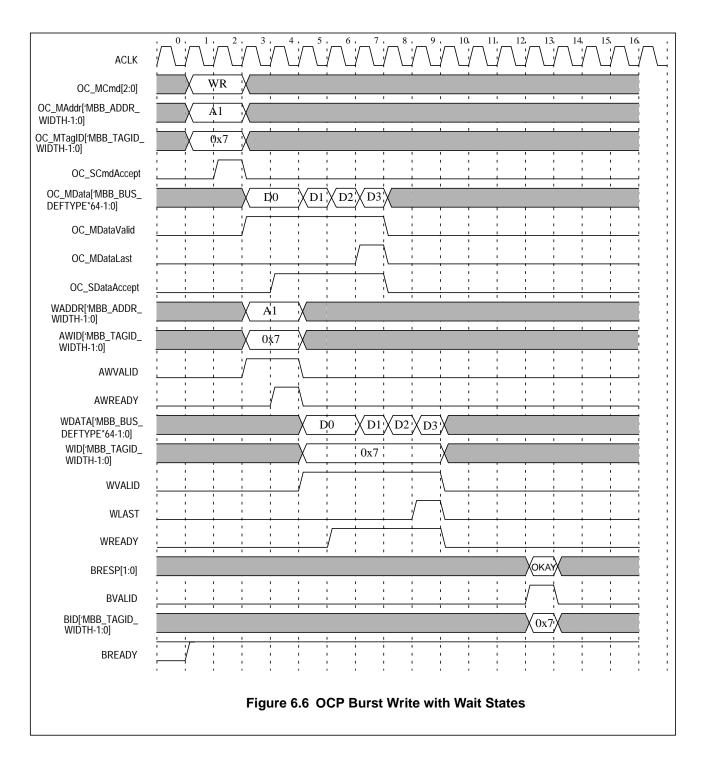

| Figure 6.6: OCP Burst Write with Wait States                                 |  |

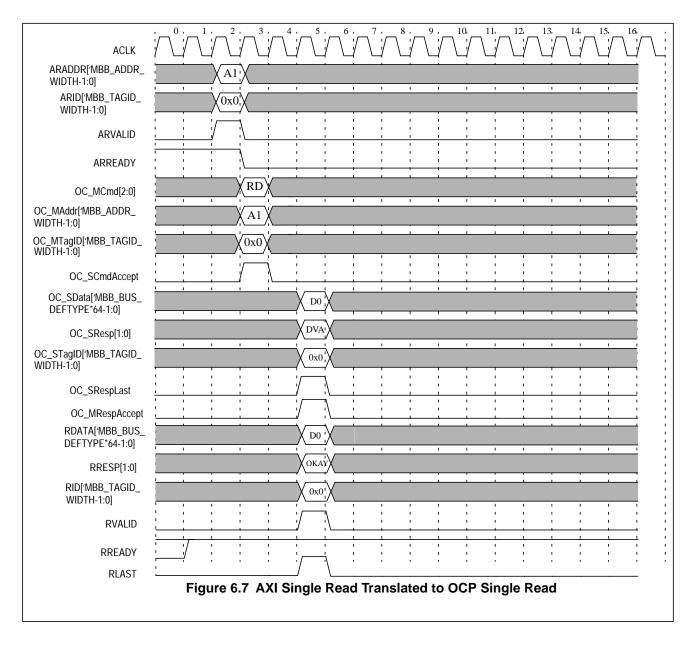

| Figure 6.7: AXI Single Read Translated to OCP Single Read                    |  |

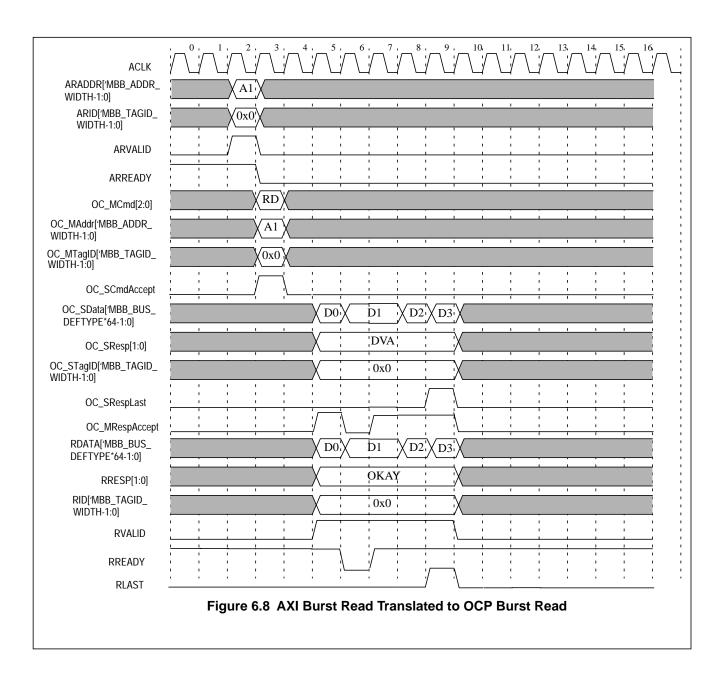

| Figure 6.8: AXI Burst Read Translated to OCP Burst Read                      |  |

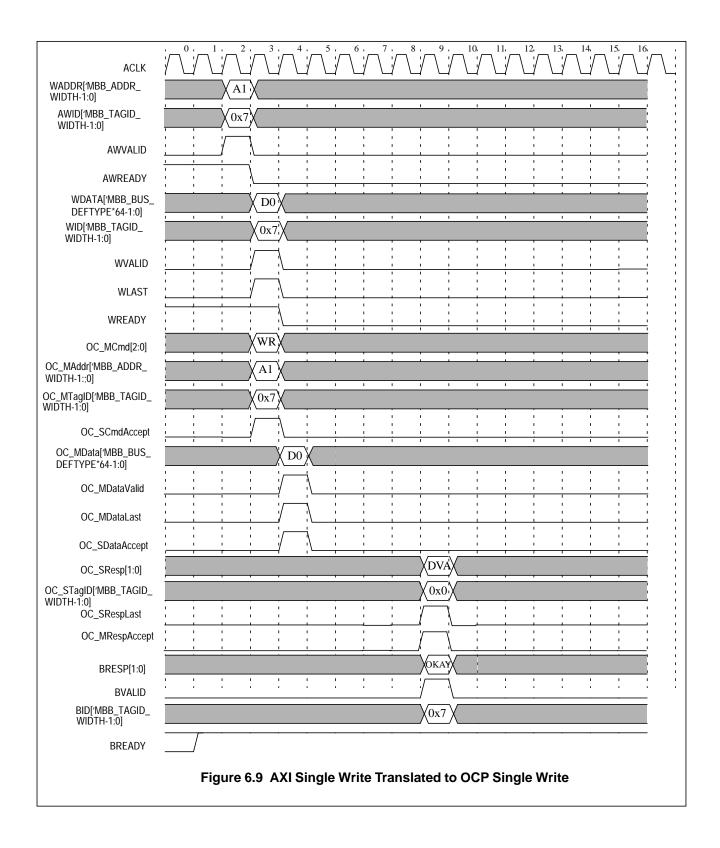

| Figure 6.9: AXI Single Write Translated to OCP Single Write                  |  |

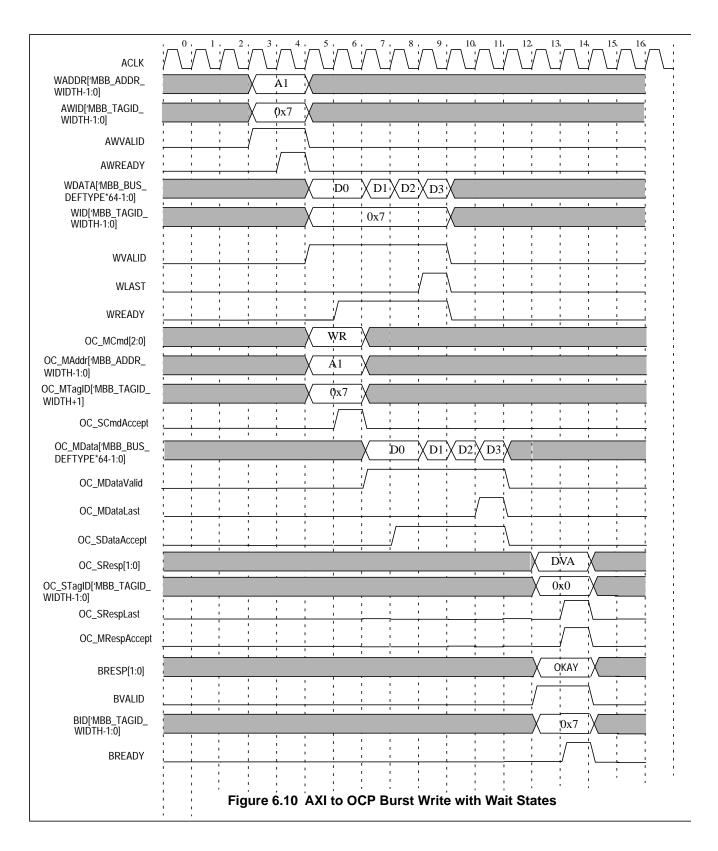

| Figure 6.10: AXI to OCP Burst Write with Wait States                         |  |

## **List of Tables**

| Table 2.1: Supported Tool/OS versions                              | 18  |

|--------------------------------------------------------------------|-----|

| Table 2.2: List of Environment Variables Set in the source.me File | 20  |

| Table 2.3: Description of Documents Found in the doc Subdirectory  | 27  |

| Table 3.1: OC_MCmd Mapping                                         | 35  |

| Table 3.2: OC_MReqInfo Mapping                                     | 36  |

| Table 3.3: OC_MBurstSeq Mapping                                    | 37  |

| Table 3.4: OC_MTagID[`'MBB_TAGID_WIDTH-1:0] Mapping                | 37  |

| Table 3.5: OC_MBurstLength Mapping                                 | 38  |

| Table 3.6: OC_MByteEn Mapping                                      | 39  |

| Table 3.7: OCP Write Data Bus Mappings                             | 39  |

| Table 3.8: Response Data Mapping                                   | 40  |

| Table 3.9: RRESP Mapping                                           |     |

| Table 3.10: SYNC Transaction Signals                               |     |

| Table 3.11: L2/L3 Cacheop Handling                                 | 42  |

| Table 3.12: Effective Priority And Read Request Restrictions       | 46  |

| Table 3.13: ARADDR/AWADDR Mapping                                  | 51  |

| Table 3.14: AWVALID/ARVALID Mapping                                |     |

| Table 3.15: ARSIZE Mapping for 64-bit Wide Data Bus                |     |

| Table 3.16: ARBURST/AWBURST Mapping                                | 53  |

| Table 3.17: AXI Port Arbitration                                   | 53  |

| Table 5.1: OCP-AXI Template                                        |     |

| Table 5.2: Template for AXI-OCP Template                           |     |

| Table 8.1: AXI Bridge Signal Direction Key                         |     |

| Table 8.2: OCP-AXI Bridge Signals                                  |     |

| Table 8.3: OCP-SPL Signals                                         |     |

| Table 8.4: OCP-AXI2 Signals                                        |     |

| Table 8.5: AXI-OCP Bridge Signals                                  | 119 |

|                                                                    |     |

Chapter 1

## Introduction

The MIPS<sup>®</sup> BusBridge<sup>™</sup> 3 Modules family provides high-performance OCP 2.1 interfaces between a MIPS core and other subsystems in an SOC.

This document is designed to serve as a high-level description of the MIPS BusBridge 3 Modules. This chapter provides an overview of the design and feature set of the various modules, and the ways they can be used.

This chapter is organized as follows:

- Section 1.1 "Features"

- Section 1.2 "OCP-AXI and AXI-OCP Usage"

- Section 1.3 "OCP-SPL Usage"

## **1.1 Features**

The MIPS BusBridge 3 Modules family includes the following blocks:

- OCP-to-AXI Bridge (OCP-AXI)

- AXI-to-OCP Bridge (AXI-OCP)

In addition, some products are delivered with an additional Reference Design for a dual AXI bridge (OCP-AXI2), which can be built with the OCP Splitter (OCP-SPL) and two instances of the OCP-AXI. Consult the MIPS softcore product datasheet to determine whether the OCP Splitter is included in the release.

## 1.1.1 OCP2AXI Bridge (OCP-AXI)

This module is a bridge between an OCP 2.1 master and an AMBA AXI slave. The main features of this bridge are:

- Connects to the master OCP port (v2.1) of the following MIPS® product families.

- MIPS32® 24K®

- MIPS32® 34K®

- MIPS32® 74К<sup>тм</sup>

- MIPS32<sup>®</sup> 1004K<sup>™</sup> Coherent Processing System

- MIPS® SOC-it® L2 Cache Controller

- MIPS32® P5600 core family

MIPS® BusBridge™ 3 Modules User's Manual, Revision 02.02

- AXI interface is compliant to AMBA AXI v1.0

- Support for 32-bit or 40-bit address, and 64-bit, 128-bit, or 256-bit data path

- No combinational paths from AXI to OCP flow control signals. This allows for full flexibility in closing SOC timing.

- Single-cycle latency on request path. No additional latency on the response path.

- Clocked with AXI system clock

- AXI clock needs to be a supported synchronous divisor of OCP master's clock

- Fully synthesizable Verilog design

### 1.1.2 OCP Splitter (OCP-SPL)

The OCP Splitter is not a standard design. Consult the MIPS softcore product datasheet to determine whether the OCP Splitter is included in the release.

This module splits the slave OCP port into two master OCP ports based on a user-defined address decode. This enables an SOC designer to direct bus transactions from the MIPS32 core to two different subsystems. The main features of the OCP-SPL are:

- Connects to the master OCP port (v2.1) of the following MIPS product families:

- MIPS32® 24K®

- MIPS32® 34K®

- MIPS32® 74K<sup>TM</sup>

- MIPS32<sup>®</sup> 1004K<sup>™</sup> Coherent Processing System

- MIPS® SOC-it® L2 Cache Controller

- MIPS32® P5600

- User-configurable address decode

- Configurable port priority

- Supports OCP response flow control

- Combinational block with no additional latency

- Fully synthesizable design

## 1.1.3 AXI-to-OCP Bridge (AXI-OCP)

This module is a bridge between an AMBA AXI master and an OCP 2.1 compliant slave. It facilitates connection of an AMBA AXI based subsystem to the OCP 2.1 slave interfaces of the I/O Coherence Unit (IOCU) on the MIPS32

1004K Coherent Processing System (CPS) or the ScratchPad RAMs DMA interfaces on MIPS32 cores. The main features of the bridge are:

- Connects an AMBA AXI master interface to the OCP 2.1 slave interfaces of the ISPRAM, DSPRAM, and IOCU blocks on the following MIPS32 cores:

- MIPS32® 24K®

- MIPS32® 34K®

- MIPS32® 74К<sup>тм</sup>

- MIPS32<sup>®</sup> 1004K<sup>TM</sup> Coherent Processing System (CPS)

- MIPS32® P5600

- Support for 32-bit or 40-bit address and 64-bit, 128-bit, or 256-bit data path

- No combinational paths from OCP to AXI flow-control signals. This allows full flexibility in closing SOC timing.

- Single-cycle latency on request path. No additional latency on the response path.

- Clocked with AXI system clock

- If the AXI-OCP bridge is connected to the IOCU of the MISP32® 1004K<sup>TM</sup> CPS, AXI clock has to be derived with a supported synchronous divisor of the CM clock. Please refer to the 1004K<sup>TM</sup> CPS Users Manual for details of the supported divisors.

- If the AXI-OCP bridge is connected to DMA interface of the ScratchPad RAMs on MIPS32 cores, AXI clock has to be derived with the same supported synchronous clock divisor as on the main OCP port of the core. Please refer to the appropriate MIPS32 Core Integrator's Guide for more details.

- Fully synthesizable Verilog design

## 1.2 OCP-AXI and AXI-OCP Usage

This section describes the different use models for the OCP-AXI and the AXI-OCP bridges with the supported MIPS product families.

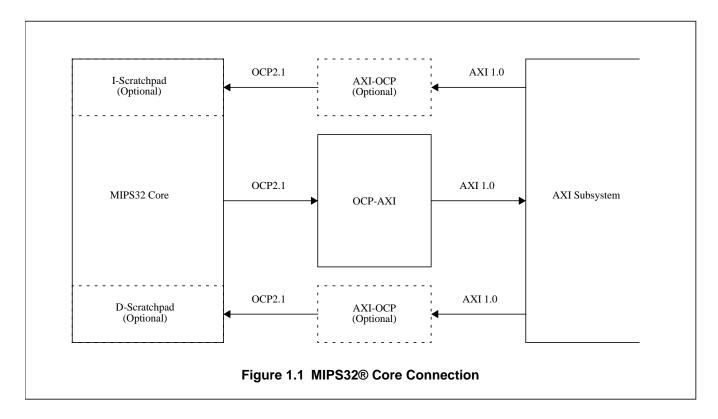

## 1.2.1 MIPS32® Core

In the most basic configuration, the OCP-AXI bridge connects to a MIPS32 core's system OCP interface directly, as shown in Figure 1.1. Note that the arrow directions in the figure are used to indicate master/slave interfaces and not data movement; all master interfaces have arrows pointing away from them. Note also that the AXI-OCP bridge is only needed if the MIPS32 core is configured with Scratchpad RAMs (ISPRAM/DSPRAM). The MIPS32 core can be one of the following:

- MIPS32® 24K® core family

- MIPS32® 34K® core family

- MIPS32® 74K<sup>TM</sup> core family

- MIPS32® 1004K Coherent Processing System

- MIPS32® P5600 core family

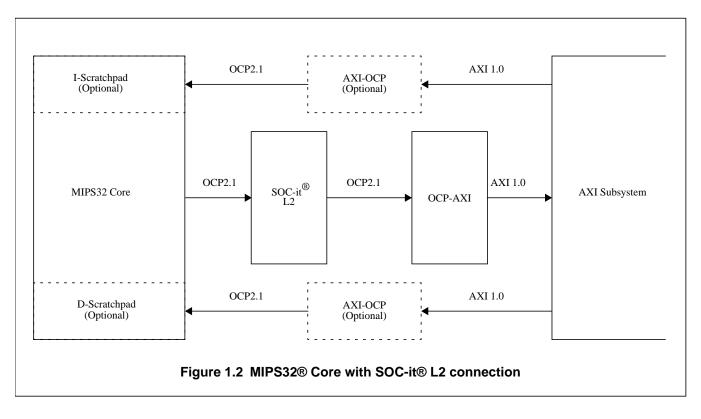

## 1.2.2 MIPS32 Core with SOC-it L2

In this type of system, where the MIPS32 core includes a SOC-it L2 Cache Controller, the OCP-AXI bridge connects directly to the SOC-it L2 cache controller's system OCP interface, as shown in Figure 1.2. The optional scratchpad connections are the same as those described in Section 1.2.1 "MIPS32® Core".

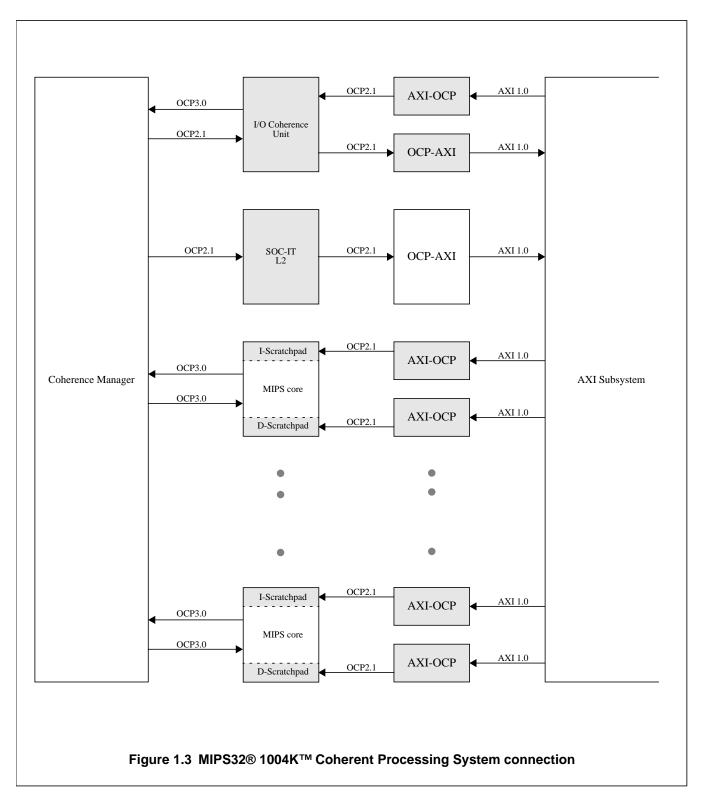

## 1.2.3 1004K Coherent Processing System AXI Bridge Configuration

In a MIPS32 1004K Coherent Processing system (CPS), a number of AXI bridges may be required. To begin, each processor core may require bridges for optional scratchpad RAMs. In addition, the following bridges may be needed:

- 1. If the system is not configured with an optional SOC-it L2, then an OCP-AXI bridge is connected to the Coherence Manager block's system OCP interface. Otherwise, if a SOCit-L2 is present, then the OCP-AXI bridge connects to the SOC-it L2 cache controller's system OCP interface.

- 2. If an optional I/O Coherence Unit (IOCU) is included, then two AXI bridges may need to be added to that block (a master port and a slave port).

Note that for simplicity, Figure 1.3 shows the maximum configuration for a multi-core system, with all optional blocks shown as shaded.

## 1.3 OCP-SPL Usage

#### Introduction

I

This section describes the different use models for the OCP-SPL with supported MIPS products. The OCP-SPL can be used with the following MIPS IP blocks by connecting to the OCP master interface of the MIPS IP block.

- MIPS32® 24K® core family

- MIPS32® 34K® core family

- MIPS32® 74K<sup>TM</sup> core family

- MIPS32® 1004K<sup>TM</sup> Coherent Processing System

- MIPS® SOC-it® L2 Cache Controller

- MIPS32® P5600 core family

Chapter 2

## Installation

This chapter describes the installation of the BusBridge<sup>TM</sup> 3 Modules package and its contents, and consists of the following sections:

- Section 2.1 "Tool Assumptions"

- Section 2.2 "Installing a Release"

- Section 2.3 "Directory Structure of the Deliverables"

## 2.1 Tool Assumptions

The deliverables associated with the MIPS® BusBridge 3 Modules assume the availability of a minimal set of UNIX-based scripting tools and front-end Electronic Design Automation (EDA) tools, as described in this section.

Use of the deliverables requires a x86 Linux operating system platform. Supported versions of the operating systems and tools are summarized in Section 2.1.3 "Supported Tool Versions".

### 2.1.1 General Tool Requirements

The following scripting tools are assumed to be available at the implementor's site:

- csh: csh/tcsh are used internally. All of the reference commands in this manual are given in C shell syntax and the various Makefiles depend on the use of csh. The deliverables have not been tested with bash, ksh, or any other shell program.

- Perl: Perl version 5 is required for some scripts included in various subdirectories of the release. Perl version 5 can be downloaded from http://www.perl.com.

- make: All Makefiles included in the release have been written to work with the GNU make tool. GNU make can be downloaded from the GNU web page at http://www.gnu.org.

- Tcl/Tk: The configuration tool assumes the availability of Tcl/Tk 8.0 or 8.1 for its graphical user interface. Tcl/Tk can be downloaded from the Tcl Developer Xchange web site at http://www.tcl.tk.

- C compiler: Compilation of MIPS-provided PLI routines requires a native C compiler. MIPS uses gcc, available at http://www.gnu.org. The deliverables have not been tested using other compilers.

- Binary tools: Compilation of MIPS-provided PLI routines requires the GNU linker and other GNU binary utilities. These are available at http://www.gnu.org.

## 2.1.2 Supported EDA Tools

The following is a list of front-end EDA tools directly supported with the MIPS BusBridge<sup>TM</sup> 3 Modules deliverables:

- Functional simulation: The RTL code is written in Verilog. The simulation environment includes support for the VCS simulator from Synopsys.

- Synthesis: The synthesis scripts support Synopsys DesignCompiler (DC).

There are no tool requirements for the back-end EDA tools that may be used to create a physical implementation of the MIPS BusBridge 3 Modules.

#### 2.1.3 Supported Tool Versions

Table 2.1 shows the tool and platform versions with which the 24Kc core deliverables have been developed and tested internally at MIPS Technologies. The core deliverables should generally work with newer tool versions, but may not work with older ones. Synthesis and backend flow have been tested with the named versions. Newer versions have not been tested with the flows but should generally work.

| ΤοοΙ                     | Version(s)           |

|--------------------------|----------------------|

| RedHat Linux             | RHEL4 (WS release 4) |

| Synopsys VCS             | 2006.06-SP2-8        |

| Synopsys VERA            | 2007.12-1            |

| Synopsys CoreTools       | B-2008.06-SP2        |

| Synopsys Design Compiler | 2007.12-SP3          |

| GNU binutils             | 2.9                  |

| gcc                      | 3.4.6                |

| gmake                    | 3.80                 |

| Tcl/Tk                   | 8.3 or 8.4           |

| Perl                     | 5.8.2                |

#### Table 2.1 Supported Tool/OS versions

#### 2.1.4 Synopsys Verification IP Version (VIP)

The testbench included with the MIPS BusBridge 3 Modules requires the installation of the Synopsys Designware VIP packages listed below. They can be downloaded from the Synopsys website.

- dw\_vip\_amba\_5.20b.run

- dw\_vip\_ocp\_vrt\_1.50a.run

This package should be installed in \$DESIGNWARE\_HOME.

## 2.2 Installing a Release

Detailed instructions for retrieving, unpacking, and installing the tar file from MIPS, containing deliverables associated with the MIPS BusBridge 3 Modules, were provided when notification about the availability of the release was received.

### 2.2.1 Unpacking Release Deliverables

The tar file containing deliverables associated with the MIPS BusBridge 3 Modules should be unpacked inside a site-wide installation directory that is accessible to all users. Customers are encouraged to install all MIPS deliverables inside this directory.

In this document, the directory that hosts various installations of MIPS deliverables is referred to as "<mips\_home>". Unpacking the tar file in <mips\_home> will create a directory tree for this release called <mips\_core>. See Section 2.2.2 "Release Naming Convention" for a description of the naming conventions used for MIPS cores.

## 2.2.2 Release Naming Convention

The MIPS BusBridge 3 Modules release is named in the following format: <core\_type>\_<release\_id>. The <core\_type> field is described below:

mbb3 for the MIPS BusBridge 3 Modules release. The <release\_id> is in the format  $x_y_z$ , with the following meaning:

- x\_y refers to the version of the MIPS BusBridge 3 Modules contained in the release. The x is a number indicating the major release version, and y is an alphanumeric value indicating the minor release version; y may be a number, or optionally a number followed by a letter, where the letter indicates a patch update to a minor version number.

- z is a number that refers to the version of all the other supporting deliverables (documentation, BFM model, synthesis scripts, etc.). There is never a patch letter associated with this version. When an RTL version is initially created, the z version number is reset to 0.

Here are an example of legal MIPS BusBridge 3 version name:

mbb3\_2\_0\_0 # Release with the MIPS BusBridge 3 Modules RTL version 2.0, and version 0 release of other deliverables

## 2.2.3 Configuring Perl Scripts

Generally, all Perl scripts require perl5. The first line of the Perl scripts included in a release contains the following interpreter line for the location of perl5 used at MIPS:

```

#! /usr/local/bin/perl

```

Since it cannot be assumed that the customer's Perl location is in the same place as MIPS, all of the Perl scripts included in a release must be updated to point to the customer's perl5 location. This is done by using a provided script:

% setenv MIPS\_HOME <mips\_home>

% setenv MIPS\_CORE <mips\_core>

% cd \$MIPS\_HOME/\$MIPS\_CORE % perl bin/perl\_path.pl <path to perl 5>

where the variable <path to perl 5> is the absolute path to the perl5 executable. Note that the perl\_path.pl script is invoked using the format 'perl <script name>'.

For example, if the perl5 executable is called perl, and located in the /bin directory, the script would be called with the following parameter:

% perl bin/perl\_path.pl /bin/perl

To find the absolute path to your Perl executable, execute:

% which perl

Note that the perl\_path.pl script will verify that the given perl5 location is actually running version 5 of Perl.

### 2.2.4 Creating a Project Area

While the basic installation of a MIPS BusBridge 3 Modules deliverables is done in the <mips\_home>/<mips\_core> hierarchy, all customizations required in implementing a core should be performed in a separate project directory. The top level directory that contains all deliverables that might require customization is referred to as <mips\_project>. Before calling the CreateProject script to create a new <mips\_project> directory, *MIPS\_HOME* and *MIPS\_CORE* environment variables should be set. If these variables are not defined, the script tries to infer them from the path to the CreateProject script. The inferred variables are printed out and should be reviewed by the implementor before proceeding further.

To create a <mips\_project> directory tree, execute:

- % setenv MIPS\_HOME <mips\_home>

- % setenv MIPS\_CORE <mips\_core>

- % mkdir <mips\_project>

- % cd <mips\_project>

- % <mips\_home>/<mips\_core>/bin/CreateProject

#### 2.2.5 Environment Variable Setup

Once the tar file containing the MIPS BusBridge 3 Modules deliverables has been installed in

<mips\_home>/<mips\_core> and the <mips\_project> directory has been created, there are a number of

environment variables that should be set. These are used by the various scripts to configure them for the customer

site. A file, <mips\_project>/proc/bin/source.me, has been included that sets the appropriate variables.

Some of these will need to be customized to match the customer site. The environment variables that need to be set

are summarized in Table 2.2.

| Variable Name | Description                                                                    | Legal Values                                                                                                |  |

|---------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| MIPS_HOME     | Central installation directory for MIPS releases, i.e. <mips_home></mips_home> | Full path of the central installation directory                                                             |  |

| MIPS_CORE     | Name of the release, i.e. <mips_core></mips_core>                              | e, i.e. <mips_core> Name of the release,<br/>m<core_type>_<release_id></release_id></core_type></mips_core> |  |

Table 2.2 List of Environment Variables Set in the source.me File

| Variable Name             | Description                                                                                                                       | Legal Values                                                             |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| MIPS_PROJECT              | Top directory containing customized files,<br>i.e., <mips_project>,</mips_project>                                                | Full path to the project directory                                       |

| MIPS_SITE<br>MIPS_PROFILE | Used to disable internal MIPS scripts                                                                                             | customer                                                                 |

| MIPS_PLATFORM             | Hosttype                                                                                                                          | Linux                                                                    |

| MIPS_SIM_TYPE             | Simulator Type                                                                                                                    | vcs                                                                      |

| MIPS_VCS_VERSION          | VCS VERSION                                                                                                                       | 2006_06                                                                  |

| The following are not set | in the source.me file. These                                                                                                      | will need to be set by the customer.                                     |

| GCC_HOME                  | Path to GCC install                                                                                                               | Path to gcc                                                              |

| VCS_HOME                  | Path to VCS install directory                                                                                                     | Path to VCS install - standard variable for VCS                          |

| VERA_HOME                 | Path to VERA install directory                                                                                                    | Path to VERA install - standard variable for VERA                        |

| OVL_HOME                  | Path to Accellera OVL2.3 install directory                                                                                        | Path to Accellera OVL2.3 install directory                               |

| DESIGNWARE_HOME           | Path to Synopsys DesignWare Install                                                                                               | This is where Synopsys DesignWare IP and VIP pack-<br>ages are installed |

| DW_VIP_DIR                | Path to where DesignWare VIP setup was run.                                                                                       | This directory contains AHB verification IP models.                      |

| VMT_VERSION               | This indicates the VMT version being used.                                                                                        | This should be set to 3.10a                                              |

| VIP_AMBA_VERSION          | This indicates the AMBA VIP version<br>being used.This should be set to 5.20b                                                     |                                                                          |

| SYNOPSYS                  | Path to Synopsys Design Compiler install         Path to Synopsys Design Compiler install - standard variable for Design Compiler |                                                                          |

| Table 2.2 List of Environment Variables Set in the source.me File (C | Continued) |

|----------------------------------------------------------------------|------------|

|----------------------------------------------------------------------|------------|

## 2.2.6 Path Setup

Add the following to your path in order to find scripts and executables used during various steps in implementing a MIPS BusBridge 3.

The following are added to your path in the <mips\_project>/proc/bin/source.me script.

- <mips\_home>/<mips\_core>/bin

- <mips\_home>/<mips\_core>/flow/bin

- <mips\_home>/<mips\_core>/flow/verif/bin

The following paths need to be added manually by the customer.

- \$SYNOPSYS/bin, \$SYNOPSYS/linux/syn/bin

- \$DESIGNWARE\_HOME/bin

- \$VCS\_HOME/bin

- \$VERA\_HOME/bin

- \$VERA\_HOME/lib

- \$GCC\_HOME/bin

- Path to make

- Path to perl

#### 2.2.7 Welcome! - The Place to Start

Included in the release is a Welcome file, in HTML format. This file includes information on MIPS support, helpful links, and most importantly, hooks to easily locate documentation for the MIPS BusBridge 3 Modules. It has been designed as the initial reference point for your MIPS BusBridge 3 Module questions. Use your favorite web browser to look at the file  $MIPS_HOME/MIPS_CORE/welcome.html$ .

#### 2.2.8 Verifying the Release

In order to be sure the release has been delivered and installed properly, users can compile the design and testbench using VCS. Please ensure that the environment variables and path setup described in the previous sections is complete before attempting to proceed to the instructions described below. The following steps must be performed before a VCS compile can be performed.

- 1. Configure the design. Please edit the configuration file "mbb\_config.vh" located in the directory \$MIPS\_PROJECT/proc/config/customer. The configuration choices are:

- 1. For the OCP-SPL module:

- MBB\_SPL: This module facilitates the creation of a dual AXI bridge (OCP-AXI2). The choices are:

mbb\_spl: Use OCP-SPL to create a Dual AXI bridge (OCP-AXI2)

mbb\_spl\_stub: Use a stub module for OCP-SPL. This is used when simulating a single AXI bridge (OCP-AXI)

MBB\_SPL\_ADDR\_DEC\_MODULE: OCP-SPL address decode module. The choices are:

mbb\_spl\_addr\_dec: The reference address decode module.

or

I

mbb\_spl\_addr\_dec\_custom: Customer defined address decode module.

- 2. For the OCP-AXI or OCP-AXI2 modules:

- MBB\_SIDEBAND\_WIDTH: Width of Sideband signals. See Section 3.1.6.4 "Sideband Signals".

- MBB\_02A\_MCONNID\_WIDTH: Width of *MConnID* signal. See Section 3.1.6.4 "Sideband Signals".

- 3. For the AXI-OCP module:

- MBB\_02A\_MCONNID\_WIDTH: Width of *MConnID* if connecting to the IO Coherence Unit (IOCU)

- MBB\_02A\_MREQINFO\_WIDTH: Width of *MReqInfo* if connecting to the IO Coherence Unit (IOCU)

- 4. Configuration choices common to all modules:

- MBB\_CREGW\_MODULE: Fine-grained Clock gating. The choices are:

mvp\_mbb\_cregister\_gc: Fine grained clock gating enabled (default).

- MBB\_ADDR\_WIDTH: Width of the MBB3 address bus. Valid values are 32 or 40 only.

- MBB\_TAGID\_WIDTH: Default width of the *OC\_MTagID* bus. Valid values are 4 and 12. This default value can be overwritten by passing a parameter value when instantiating a copy of the MBB3 module. For example:

mbb\_ocp2axi #(.BUS\_ID\_WIDTH(4)) my\_mbb\_ocp2axi (...

• MBB\_BUS\_DEFTYPE: Default bus width or type of the data bus in MBB3. Valid values are 1, 2 or 4. "1" indicates a 64b wide bus, "2" indicates a 128b wide bus, and "4" indicates a 256b wide bus. This default value can be overwritten by passing a parameter value when instantiating a copy of the MBB3 module. For example:

mbb\_ocp2axi\_dual #(.BUS\_TYPE(2), ...

- mvp\_mbb\_cregister\_ngc: Fine-grained clock gating disabled.

- MBB\_NUM\_SCAN\_CHAIN: Number of Scan chains.

- 2. Setup Synopsys Verification IP (VIP). Create a directory where you want to setup the VIP. The environment variable DW\_VIP\_DIR should be set to that directory. Please ensure that you set VMT\_VERSION and VIP\_AMBA\_VERSION as described in Table 2.2.

```

% setenv VMT_VERSION 3.10a

```

- % setenv VIP\_AMBA\_VERSION 5.20b

- % mkdir <vip\_install\_dir>

- % cd <vip\_install\_dir>

- % setenv DW\_VIP\_DIR \$PWD

% dw\_vip\_setup -path . -vmt \$VMT\_VERSION -add axi\_port\_monitor\_vmt -v \$VIP\_AMBA\_VERSION -ntb

% dw\_vip\_setup -path . -vmt \$VMT\_VERSION -add axi\_interconnect\_vmt -v \$VIP\_AMBA\_VERSION -ntb

% dw\_vip\_setup -path . -vmt \$VMT\_VERSION -add axi\_slave\_vmt -v \$VIP\_AMBA\_VERSION

-ntb

% dw\_vip\_setup -path . -vmt \$VMT\_VERSION -add axi\_master\_vmt -v \$VIP\_AMBA\_VERSION

-ntb

% dw\_vip\_setup -path . -vrt 1.20a -add ocp\_slave\_svt -v 1.50a

% dw\_vip\_setup -path . -vrt 1.20a -add ocp\_monitor\_svt -v 1.50a

3. Create a configuration file for the Synopsys AMBA VIP models.

Create a file named "axi\_bridge\_iconnect.config" under \$DW\_VIP\_DIR. It should contain the following lines:

program AxiSlaveProgram.vrp program AxiPortMonitorProgram.vrp program AxiInterconnectProgram.vrp program AxiMasterProgram.vrp

- 4. Build a simulation model (RTL + Testbench) using VCS

- % cd \$MIPS\_PROJECT % mkdir <build\_dir> % cd <build\_dir> For the OCP-AXI bridge or the OCP-AXI2 reference design do % buildSim -b sa\_rtl -local -define OCP2AXI For the AXI-OCP bridge do % buildSim -b sa\_rtl -local -define AXI2OCP

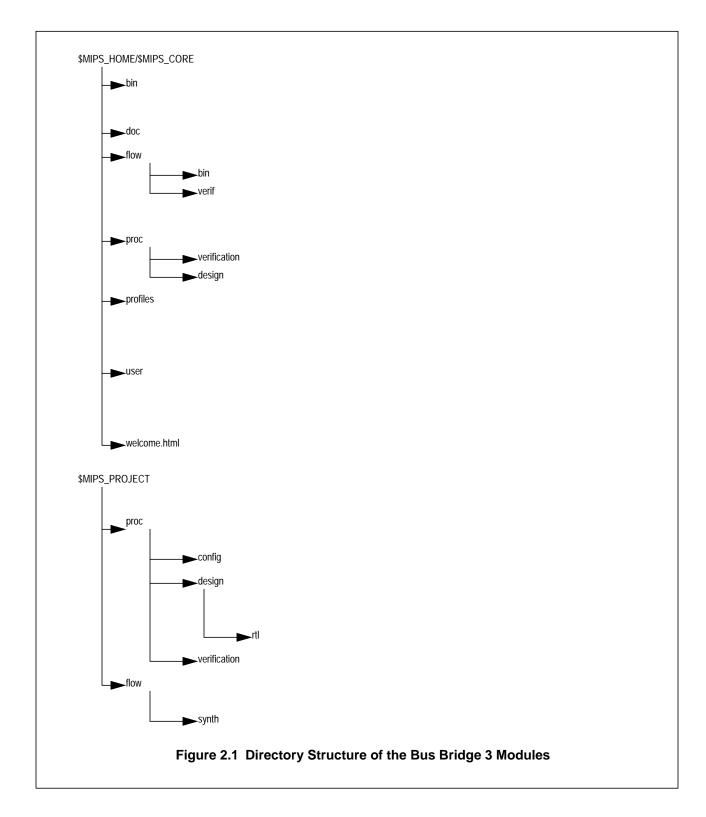

## 2.3 Directory Structure of the Deliverables

The directory structure of a MIPS BusBridge 3 Modules distribution is shown in Figure 2.1. The contents are divided into two separate directory trees based on whether or not they require modification by the customer. The \$MIPS\_HOME/\$MIPS\_CORE hierarchy contains all 'golden' components that should only be used as delivered. The \$MIPS\_PROJECT hierarchy contains components that can be customized if required.

#### Installation

## 2.3.1 \$MIPS\_HOME/\$MIPS\_CORE Directory Tree

The \$MIPS\_HOME/\$MIPS\_CORE tree contains top-level directories listed in the following subsections. Each subsection briefly describes the contents of each of these directories, and the remainder of this document goes into further detail about using the deliverables contained within them:

- Section 2.3.1.1 "bin Subdirectory"

- Section 2.3.1.2 "doc Subdirectory"

- Section 2.3.1.3 "flow Subdirectory"

- Section 2.3.1.4 "proc Subdirectory"

- Section 2.3.1.5 "profiles Subdirectory"

- Section 2.3.1.6 "user Subdirectory"

#### 2.3.1.1 bin Subdirectory

The bin subdirectory contains scripts and/or executables that are needed when creating, simulating or synthesizing the MIPS BusBridge 3 Modules. This directory should become part of the user's path in order to allow access to the scripts as described in Section 2.2.6 "Path Setup".

A MIPS BusBridge 3 Modules release includes the following Perl scripts or executables:

- buildSim Script to create a simulation executable of the core.

- checksum\_deliv Script to check that the entire release directory structure was delivered and installed properly.

- CreateProject Creates the <mips\_project> directory where the core can be configured and customized.

- perl\_path.pl- Script to update interpreter line of perl scripts to customer's perl version 5 location.

Generally, all Perl scripts require perl5. See Section 2.2.3 "Configuring Perl Scripts" for instructions on how to update all of the perl scripts contained in the release to point to your location of perl5.

#### 2.3.1.2 doc Subdirectory

The doc subdirectory contains general documents included in the delivery. The formats may be one of:

- .html WWW Browser format

- .pdf Adobe Acrobat format

- .txt ASCII text format

Documents in this area may be accessed via the file \$MIPS\_HOME/\$MIPS\_CORE/welcome.html, or directly from the doc subdirectory.

A MIPS BusBridge 3 Modules release includes the documents shown in Table 2.3.

Documents that are assigned a MIPS Document number are named with an amalgamation of the document number, security class, short title, document type, and revision; see "MD Document Filename format" on page 27 for more details.

| MIPS Document<br>Number | Title/Description                                   |

|-------------------------|-----------------------------------------------------|

| MD00660                 | MIPS® BusBridge <sup>™</sup> 3 Modules Users Manual |

#### Table 2.3 Description of Documents Found in the doc Subdirectory

#### MD Document Filename format

The filename of all pdf documents with an MD number is in the following format:

<MD number>-<security class>-<product>-<type>-<revision>.pdf

The fields have the following meaning:

- <MD number> consists of the prefix MD and a unique 5 digit number

- <security class> defines the confidentiality level of the document. The meaning and treatment of the confidentiality levels is described in a MIPS legal contract. This field is always two characters and usually has one of the following values:

- 1B: restricted confidential document

- 1C: internal confidential document

- 1D: external confidential document

- 2B: commercial document

- <product> is a variable length string holding a descriptive name about the MIPS product to which the document is related.

- PLATFORMS: for MIPS32 CPU platform specific documents

- <type> is a 3 character string that encodes the type of document. Some examples are:

- USM: users manual

- AFP: architecture document for programmers

- APP: application note

- DTS: data sheet

- ERS: errata sheet

- IMG: implementation guide

- ING: integration guide

- SUM: software user's manual

- SPC: specification

- <revision> is a 5 character string in the form *xx.yy*, holding the major (*xx*) and minor (*yy*) revision number of a document.

Since the MD naming scheme is somewhat difficult to decipher, symbolic links have been created with slightly more meaningful names.

#### 2.3.1.3 flow Subdirectory

The flow subdirectory contains scripts for synthesis and verification of the MIPS BusBridge 3 Modules and is further subdivided into two subdirectories:

#### bin Subdirectory

This subdirectory contains the various Perl scripts used while carrying out verification, synthesis, and static timing analysis on the MIPS BusBridge 3 Modules.

#### verif Subdirectory

This subdirectory contains a make subdirectory which contains the common simulator makefile to build the simulation executables.

#### 2.3.1.4 proc Subdirectory

This directory contains the RTL files for the MIPS BusBridge 3 Modules in the following subdirectories:

#### design/rtl Subdirectory

The design/rtl subdirectory contains the majority of Verilog RTL source code of the MIPS BusBridge 3 Modules for synthesis and simulation. Two types of files are present :

- \*.v files Verilog RTL source of the MIPS BusBridge 3 Modules for synthesis and simulation.

- \*.vh files The include files containing 'define statements used in RTL files. These files are 'included into all Verilog files that use the 'defines.

#### verification Subdirectory

The verification hierarchy contains all files needed to simulate a variety of testbenches provided with the MIPS BusBridge 3 Modules. Notable files or directories in this tree include:

- testbenches Directory holding testbench files

- build Directory holding files related to simulator builds.

#### 2.3.1.5 profiles Subdirectory

The profiles subdirectory contains default configurations for rundiags and buildSim.

#### 2.3.1.6 user Subdirectory

The user subdirectory contains files that are used by the CreateProject script to construct a fresh <mips\_project> directory. Files in this directory should not be used for synthesis and simulation and the deliverables provided with the BusBridge 3 Modules do not use these files directly. The script CreateProject copies over these files into the <mips\_project> directory and the BusBridge 3 deliverables pick up these files from there. It is anticipated that users might need to change some of the information in these files (as explained in other portions of this document) and users should be careful to modify these files only in their <mips\_project> directory.

## 2.3.2 \$MIPS\_PROJECT Directory Tree

The \$MIPS\_PROJECT tree contains top-level directories listed in the following subsections. Each subsection briefly describes the contents of each of these directories, and the remainder of this document goes into further detail about using the deliverables contained within them:

• Section 2.3.2.1 "proc Subdirectory"

#### 2.3.2.1 proc Subdirectory

This directory contains files needed for configuring and customizing the MIPS BusBridge 3 Modules. This is also where the simulation executable for the design should be built. The subdirectories are described in more detail below.

#### bin Subdirectory

The bin subdirectory contains the source.me file to set up various environment variables required to simulate or synthesize the design. This file should be customized according to environment of the customer and then sourced before carrying out simulation or synthesis.

#### config Subdirectory

This directory contains mbb\_config.vh that is used to configure the MIPS BusBridge 3 RTL.

#### design Subdirectory

This directory contains user modifiable RTL files for the MIPS BusBridge 3.

#### verification Subdirectory

The verification subdirectory is where the simulation executable or script is built, as appropriate for the implementor's chosen simulator, via a standard Makefile.

#### 2.3.2.2 flow Subdirectory

This directory contains the files needed for running synthesis using Synopsys Design Compiler (DC) on the MIPS BusBridge 3 Modules. For a more detailed description on the files, refer to Chapter 7, "Synthesis" on page 85.

synth/projsyn/lib Subdirectory

This directory contains the library specific setup file for DC, called lib\_setup.dc, for running synthesis.

synth/projsyn/script Subdirectory

This directory contains all the scripts required to run synthesis on Layer 1 of the MIPS32 CPU platform.

synth/projsyn/sdc Subdirectory

This directory contains sdc constraints.

Chapter 3

## **Functional Descriptions**

This chapter describes the basic functionality of the different component blocks of the BusBridge<sup>™</sup> 3 Modules. It is organized as follows:

- 1. Section 3.1 "OCP-AXI Functional Description"

- 2. Section 3.2 "OCP-SPL Functional Description"

- 3. Section 3.3 "OCP-AXI2 Functional Description"

- 4. Section 3.4 "AXI-OCP Functional Description"

## 3.1 OCP-AXI Functional Description

## 3.1.1 Functional Block Diagram

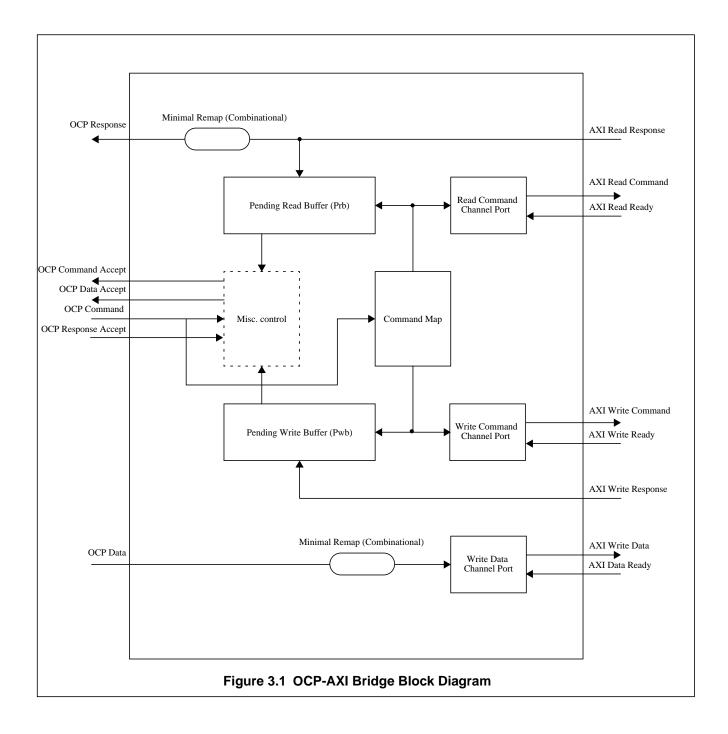

The block diagram for the OCP-AXI bridge is shown in Figure 3.1. The bridge consists of the following main components, which are described in more detail in the following sections:

- 1. Section 3.1.2 "Output Ports"

- 2. Section 3.1.3 "Pending Read Buffer"

- 3. Section 3.1.4 "Pending Write Buffer"

- 4. Section 3.1.5 "OCP 2.1 to AXI 1.0 Map Block"

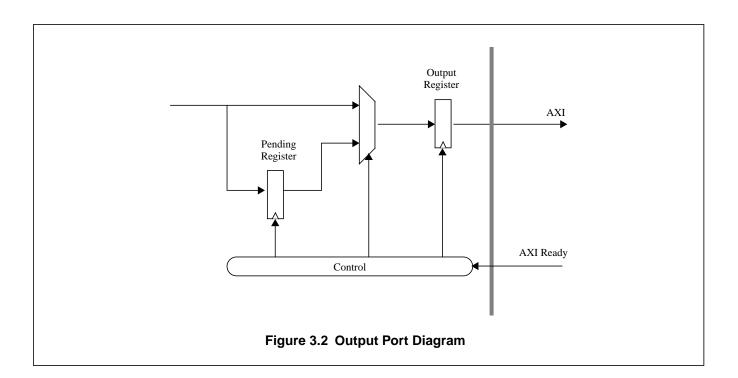

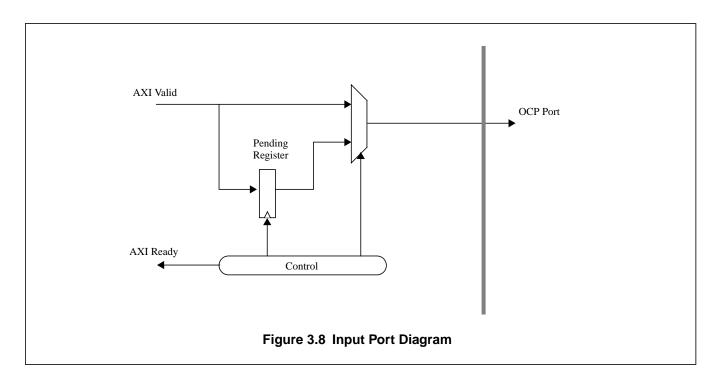

## 3.1.2 Output Ports

The bridge has three output ports to the AXI interface; one each for the read address channel, write address channel, and write data channels. The three output ports are identical from a logic point of view, with the only difference being in the port width. The output ports are used for the following reasons:

#### **Functional Descriptions**

- 1. Eliminate any dependency between the OCP flow control signals and the AXI flow control signals, i.e OC\_SCmdAccept and OC\_SDataAccept are not derived from ARREADY, AWREADY, and WREADY.

- 2. Buffer a stalled OCP transaction to allow other transactions behind it to proceed.

As shown in Figure 3.2, the port consist mainly of a pending register, an output register, a mux to control the data to the output register, and some associated control.

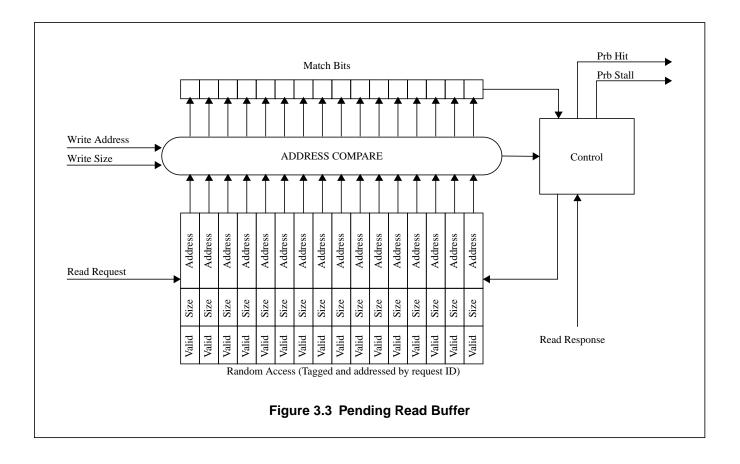

### 3.1.3 Pending Read Buffer

The Pending Read Buffer (Prb) is used to prevent write-after-read hazards (WAR). It consist of 16 entries to keep track of pending read transactions. Each read request that is issued to the read command port is entered into the Prb. The address of the request as well as the burst length are recorded. When the last read data for the request is received by the Prb, the corresponding entry is deleted. Note that the Prb is tag compared and selected by the ID of the read request.

When a write request is getting issued to the bridge, its address is checked against all pending reads. If there is an overlap, then a Prb hit is signal and the matching entries are recorded in a match vector. The write request is then prevented from updating the output register. Instead, it is staged in the pending register in the write command port and waits until all matching read entries completed. During that time, no new write requests are accepted by the OCP-AXI bridge. Note that write data and read requests can still be accepted when the write request is stalled due to WAR hazard.

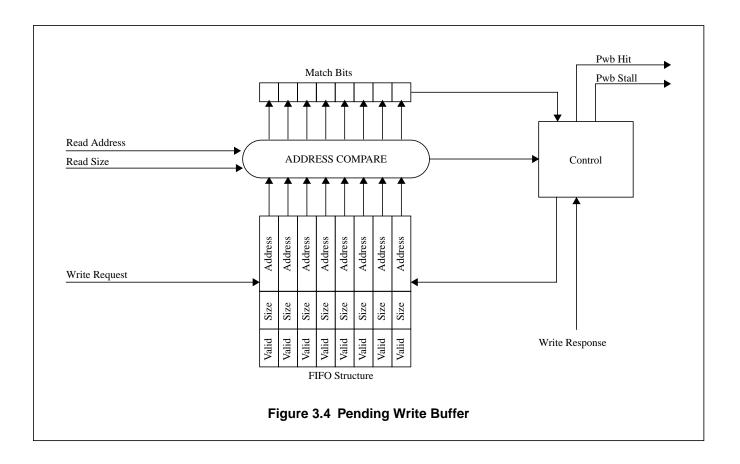

## 3.1.4 Pending Write Buffer

The Pending Write Buffer (Pwb) is used to prevent read-after-write hazards (RAW). It consist of 8 entries to keep track of pending write transactions. Each write request that is issued to the write command port is entered into the Pwb. The address of the request as well as the burst length are recorded. When the completion response for the write is received by the Pwb, the corresponding entry is deleted. The Pwb is analogous in functionality to the Prb, but is structured as a FIFO, because all writes complete in order.

When a read request is issued to the bridge, its address is checked against all pending writes. If there is an overlap, then a Pwb hit is signaled, and the matching entries are recorded in a match vector. The read request is then prevented from updating the output register. Instead, it is staged in the pending register in the read command port, and waits until all matching write entries completed. During that time, no new read requests are accepted by the OCP-AXI bridge. Note that write data and write requests can still be accepted when the read request is stalled due to WAR hazard. When there is no available Pwb entry, the bridge does not accept any more write commands and backpressures the OCP master.

## 3.1.5 OCP 2.1 to AXI 1.0 Map Block

The command mapping block is a combinational block that maps OCP encodings to AXI encodings. The detailed mapping are described in the following sections.

### 3.1.5.1 OCP 2.1 Request Signals

#### OC\_MCmd[3:0]

OCP command bus, indicates the type of transaction requested. Only some encodings are used and they are set in concert with the values on OC\_MReqInfo and OC\_MAddrSpace. The encodings used are shown in the following table:

| Encoding | Command | Mnemonic | AXI Mapping | Notes                            |

|----------|---------|----------|-------------|----------------------------------|

| 0        | Idle    | IDLE     | None        | No transaction                   |

| 1        | Write   | WR       | AWVALID     | L2 cacheop writes are not mapped |

| Table 3.1 O | C_MCmd | Mapping |

|-------------|--------|---------|

|-------------|--------|---------|

| Encoding | Command | Mnemonic | AXI Mapping | Notes                           |

|----------|---------|----------|-------------|---------------------------------|

| 2        | Read    | RD       | ARVALID     | L2 cacheop reads are not mapped |

| 3-7      | Unused  | -        | -           | Not used                        |

#### Table 3.1 OC\_MCmd Mapping (Continued)

#### OC\_MReqInfo[6:0]

For transactions other than SYNC and CACHE, the *OC\_MReqInfo[2:0]* field encodes the cacheability attributes for a transaction; it uses the same encoding as the CCA field described in a *MIPS32® Processor Core Family Software Users Manual. OC\_MReqInfo[3]* indicates that the transaction is due to a SYNC instruction; when this bit is high, the lower bits [2:0] indicate an uncached CCA type.

The encoding of the OC\_MReqInfo field for all transactions other than CACHE is summarized in the following table:

|          |                                                 | AXI Mapping (ARCACHE[3:0])<br>(WA = write allocate, RA= read allocate, C= cacheable, B = bufferable) |    |   |   |  |

|----------|-------------------------------------------------|------------------------------------------------------------------------------------------------------|----|---|---|--|

| Encoding | Encoding Command Information                    |                                                                                                      | RA | С | В |  |

| 0        | Cacheable, noncoherent, WT, NWA                 | 0                                                                                                    | 1  | 1 | 0 |  |

| 1        | Cacheable, noncoherent, WT, WA                  | 1                                                                                                    | 1  | 1 | 0 |  |

| 2        | Uncached, noncoherent                           | 0                                                                                                    | 0  | 0 | 0 |  |

| 3        | Cacheable, noncoherent, WB, WA                  | 1                                                                                                    | 1  | 1 | 0 |  |

| 4        | Cacheable, coherent, WB, WA, exclusive          | 1                                                                                                    | 1  | 1 | 0 |  |

| 5        | Cacheable, coherent, WB, WA, exclusive on write | 1                                                                                                    | 1  | 1 | 0 |  |

| 6        | Reserved                                        | 0                                                                                                    | 0  | 0 | 0 |  |

| 7        | Uncached accelerated                            | 0                                                                                                    | 0  | 0 | 0 |  |

| 8-9      | Reserved                                        | 0                                                                                                    | 0  | 0 | 0 |  |

| 10       | SYNC with uncached CCA                          | 0                                                                                                    | 0  | 0 | 0 |  |

| 11-15    | Reserved                                        | 0                                                                                                    | 0  | 0 | 0 |  |

#### Table 3.2 OC\_MRegInfo Mapping

Note: The AXI bridge will not map OC\_MReqInfo[6:4], since these deal with L2 cache exclusivity control.

#### OC\_MAddrSpace[1:0]

The OC\_MAddrSpace signal is used as L2/L3 Address Space indicator. When the core is issuing an L2 or an L3 CACHE operation, the corresponding bit (Bit [0] for L2, and Bit [1] for L3) is asserted. It indicates to the system that this OCP command is targeted to the address space of the L2 or L3 Cache.

The AXI bridge does **not** map this field since an L2 or an L3 cache should be on the OCP side.

#### OC\_MAddr['MBB\_ADDR\_WIDTH-1:0]

The  $OC\_MAddr$  is the physical doubleword address bus. Note that the least-significant 3 address bits are statically tied to 0, and the address of the byte(s) within the doubleword are indicated by the read ( $OC\_MByteEn$ ) or write ( $OC\_MDataByteEn$ ) byte enable fields. This field maps to:

- 1. ARADDR['MBB\_ADDR\_WIDTH-1:0] (Read requests)

- 2. AWADDR['MBB\_ADDR\_WIDTH-1:0] (Write requests)

Note that on AXI, the address bus refers to the starting byte address, so the OC\_MByteEn are used to generate the lower address ARADDR.

#### OC\_MBurstSeq[2:0]

This field indicates the type of burst sequence. The core can only generate two possible values, determined by the  $SI\_SBlock$  static input, as shown in the following table:

#### Table 3.3 OC\_MBurstSeq Mapping

| Encoding  | Burst Sequence                                                                     | AXI Mapping                                                                             |

|-----------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 2         | Sequential: Critical dword first, with linear wrapping for subsequent beats        | ARBURST[1:0] = WRAP (Read request)<br>AWBURST[1:0] = WRAP (Write request)               |

| 4         | Sub-block Critical dword first, with increment/decre-<br>ment for subsequent beats | AXI does not support sub-block ordering. Therefore SI_SBlock <b>should be tied to 0</b> |

| 0-1,3,5-7 | Unused by 24Kc core                                                                | -                                                                                       |

#### OC\_MTagID['MBB\_TAGID\_WIDTH-1:0]

The transaction tag identifier maps directly to the read transaction ID *ARID* for read requests, and to the write transaction ID *AWID* for write requests. Note that the field is also used to generate the instruction/data bit indicator *ARPROT[2]* on the AXI interface.

I

| Table 3.4 OC_MTagID[`'MBB_TAGID_WIDTH-1:0] Mapping | Table 3.4 OC | MTagID[ | 'MBB | TAGID | WIDTH-1:0 | Mapping |

|----------------------------------------------------|--------------|---------|------|-------|-----------|---------|

|----------------------------------------------------|--------------|---------|------|-------|-----------|---------|

| Encoding Tag Allocation |                        | AXI Mapping                |  |

|-------------------------|------------------------|----------------------------|--|

| 0                       | From Read buffer 0     |                            |  |

| 1                       | From Read buffer 1     |                            |  |

| 2                       | From Read buffer 2     | $- \qquad ARPROT[2] = 0$   |  |

| 3                       | From Read buffer 3     | _                          |  |

| 4                       | From Fetch buffer 0    | A B D D O T [2] - 1        |  |

| 5                       | From Fetch buffer 1    | - ARPROT[2] = 1            |  |

| 6                       | SYNC                   | Does not get passed to AXI |  |

| 7                       | WR, CACHE-RD, CACHE-WR |                            |  |

| 8-11                    | Reserved               | -                          |  |

| 12                      | From Fetch buffer 2    | ARPROT[2] = 1              |  |

| 13                      | From Fetch buffer 3    |                            |  |

| 14-15                   | Reserved               | -                          |  |

| Encoding | Tag Allocation      | AXI Mapping   |  |

|----------|---------------------|---------------|--|

| 8        | From Read buffer 4  |               |  |

| 9        | From Read buffer 5  | ARPROT[2] = 0 |  |

| 10       | From Read buffer 6  |               |  |

| 11       | From Read buffer 7  |               |  |

| 12       | From Fetch buffer 2 | ARPROT[2] = 1 |  |

| 13       | From Fetch buffer 3 | 1             |  |

| 14-15    | Reserved            | -             |  |

#### Table 3.4 OC\_MTagID[`'MBB\_TAGID\_WIDTH-1:0] Mapping (Continued)

Note that the correlation of IDs to processor buffers is only valid when the bridge is directly connected to the processor core.

#### OC\_MBurstPrecise

Indicates whether the burst length is precise. Burst lengths are always fixed to either 4 or 8 beats, so this pin is static set to 0x1.

#### OC\_MBurstSingleReq

Indicates whether there is a single request for all data transfers in a burst. In the core, there is always a single command request so this pin is statically set to 0x1. This signal is unused by the AXI bridge.

#### OC\_MBurstLength[2:0]

Number of 64b data transfers, only three values are possible

| Table 3.5 OC_MBurstLength Mapping |  |

|-----------------------------------|--|

|-----------------------------------|--|

| Encoding                          | Number of Transfers | AXI Mapping                                                                                                                         |

|-----------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1                                 | 1, single transfer  | ARLEN[3:0] = 4'b0000 (Read, 1 transfer, 64-bit AXI data paths)<br>AWLEN[3:0] = 4'b0000 (Write, 1 transfer, 64-bit AXI data paths)   |

| 4                                 | 4-beat burst        | ARLEN[3:0] = 4'b0011 (Read, 4 transfers, 64-bit AXI data paths)<br>AWLEN[3:0] = 4'b0011 (Write, 4 transfers, 64-bit AXI data paths) |

| 8                                 | 8-beat burst        | ARLEN[3:0] = 4'b0111 (Read, 8transfers, 64-bit AXI data paths)<br>AWLEN[3:0] = 4'b0111(Write, 8 transfers, 64-bit AXI data paths)   |

| [k]<br>(xth bit in<br>OC_MByteEn) | [9*k-1:8*k]         | OC_MByteEn['MBB_BUS_DEFTYPE*8-1:0] = 'x    (1 << (k + 1))><br>lower-bits of ARADDR = 'd(k)                                          |

| others                            | Unused by core      | -                                                                                                                                   |

I

### OC\_MByteEn['MBB\_BUS\_DEFTYPE\*8-1:0]

Byte enables for reads. Includes data alignment, endianness and address. The correlation of each bit in the *OC\_MByteEn* field to the returned read data bytes is shown in the following table. Note that the byte enables are used to determine the starting byte address on the AXI side.

| OC_MByteEn | Requested byte to be returned<br>on OC_SData bus | AXI Mapping                                                                                                                        |

|------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| [0]        | [7:0]                                            | OC_MByteEn['MBB_BUS_DEFTYPE*8-1:0] =x1 -> ARADDR[2:0] = 3'b000                                                                     |

| [1]        | [15:8]                                           | OC_MByteEn['MBB_BUS_DEFTYPE*8-1:0] =x10 -> ARADDR[2:0]<br>= 3'b001                                                                 |

| [2]        | [23:16]                                          | OC_MByteEn['MBB_BUS_DEFTYPE*8-1:0] =x100 -><br>ARADDR[2:0] = 3'b010                                                                |

| [3]        | [31:24]                                          | OC_MByteEn['MBB_BUS_DEFTYPE*8-1:0] =x1000 -><br>ARADDR[2:0] = 3'b011                                                               |

| [4]        | [39:32]                                          | OC_MByteEn['MBB_BUS_DEFTYPE*8-1:0] =x10000 -><br>ARADDR[2:0] = 3'b100                                                              |

| [5]        | [47:40]                                          | OC_MByteEn['MBB_BUS_DEFTYPE*8-1:0] =x100000 -><br>ARADDR[2:0] = 3'b101                                                             |

| [6]        | [55:48]                                          | OC_MByteEn['MBB_BUS_DEFTYPE*8-1:0] =x1000000 -><br>ARADDR[2:0] = 3'b110                                                            |

| [7]        | [63:56]                                          | OC_MByteEn['MBB_BUS_DEFTYPE*8-1:0] =x10000000 -><br>ARADDR[2:0] = 3'b111                                                           |

| [k]        | [9*k-1:8*k]                                      | OC_MByteEn['MBB_BUS_DEFTYPE*8-1:0] = 'x    (1 << (k + 1))><br>lower-bits of ARADDR = 'd(k)<br>where k is the xth bit in OC_MByteEn |

#### Table 3.6 OC\_MByteEn Mapping

#### 3.1.5.2 Write Data OCP Signals

The write data OCP signals map directly to their AXI counterparts.

#### Table 3.7 OCP Write Data Bus Mappings

| OCP Signal Description                  |            | AXI Mapping |

|-----------------------------------------|------------|-------------|

| OC_MData                                | Write data | WDATA       |

| OC_MDataByteEn Byte enables for writes. |            | WSTRB       |

| OC_MDataValid Valid write data          |            | WVALID      |

| OC_MDataTaglD Write data tag identifier |            | WID         |

| OC_MDataLast Last data in a write burst |            | WLAST       |

#### 3.1.5.3 OCP 2.1 Response Signals

In this section, we discuss how the AXI response signals are mapped back into OCP. To start off, the read data and tag identifier, and last data indicators map back directly to their OCP equivalents:

| AXI Signal | Description | OCP Mapping  |  |

|------------|-------------|--------------|--|

| RID        | Read ID Tag | OC_STagID    |  |

| RDATA      | Read Data   | OC_SData     |  |

| RLAST      | Read Last   | OC_SRespLast |  |

#### Table 3.8 Response Data Mapping

The AXI response signal RRESP[1:0] maps back to the OC\_SResp[1:0] and OC\_SRespInfo[1:0] as follows:

| AXI Signal          | Description | OCP Mapping                                                     |

|---------------------|-------------|-----------------------------------------------------------------|

| RRESP[1:0] == 2'b00 | OKAY        | OC_SRESP[1:0] = 2'b01 (Data valid)                              |

| RRESP[1:0] == 2'b01 | EXOKAY      | N/A (AXI bridge does not make exclusive accesses)               |

| RRESP[1:0] == 2'b10 | SLVERR      | OC_SResp[1:0] = 2'b11 (Error), OC_SRespInfo = 2'b00 (Bus Error) |

| RRESP[1:0] == 2'b11 | DECERR      | OC_SResp[1:0] = 2'b11 (Error), OC_SRespInfo = 2'b00 (Bus Error) |

#### Table 3.9 RRESP Mapping

#### 3.1.5.4 Unmapped Signals

There remains some signals on AXI side that are not mapped from OCP. Those assume some default values and are listed in this section.

#### AXI Write Response Signals

The OCP interface on MIPS cores does not use write responses. So all the write response signals from AXI are not passed through. Those include the following: *BID*, *BRESP*, *BVALID*, and *BREADY*. The AXI write responses are used internally in the bridge for SYNC handling as well as RAW (read-after-write) hazard handling.

#### AWLOCK and ARLOCK Handling

The AXI bridge will not make any locked or exclusive accesses, so these signals are hardwired to normal access value, i.e.: AWLOCK[1:0] = 2 'b00, ARLOCK[1:0] = 2 'b00.

#### ARPROT and AWPROT Handling

These signals are used to communicate some additional information about the request:

- ARPROT[0] and AWPROT[0]: Normal or privileged access (0 is normal access)

- *ARPROT*[1] and *AWPROT*[1]: Secure or non-secure (1 is non-secure)

- ARPROT[2] and AWPROT[2]: Instruction or data (0 is data access)\_

The only bit that is mapped by the bridge it bit [2] since we can deduce the instruction/data type of the request from the tag identified on the OCP side. Note however that the information is valid only when the bridge is connected directly to the processor core.

The lower two bits are user selectable using the port AXI\_CMD\_PROT[1:0]. The user can set the value for these statically or through some external logic to the bridge. The bridge associates the AXI\_CMD\_PROT[1:0] with the current OCP request and passes that information over when it remaps the request to the AXI side.

#### ARBURST and AWBURST

The burst type on the AXI will be set to one of the following values based on the burst length:

- Burst length of 1: ARBURST[1:0] = AWBURST[1:0] = 2'b01 (INCR)

- Burst length of 4 or 8: ARBURST[1:0] = AWBURST[1:0] = 2'b10 (WRAP)

#### ARSIZE and AWSIZE

The burst size will be hardwired to use the full AXI data bus width for burst transfers, i.e:

• ARSIZE[2:0] = ARSIZE[2:0] = 3 'b011 (8 bytes, for AXI with 64-bit data path)

### 3.1.6 Special Topics

#### 3.1.6.1 SYNC Handling

The AXI bridge supports externalized SYNC requests. An external SYNC request is actually an OCP read command with the following characteristics:

| Signal             | Value for Sync Transaction                                                                                                |

|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| OC_MAddr           | OC_MAddr['MBB_ADDR_WIDTH-1:8] is always 0x1fc000.<br>OC_MAddr[7:3] holds the stype bits [10:6] from the SYNC instruction. |

| OC_MByteEn         | Always 0                                                                                                                  |

| OC_MBurstLength    | Always 1                                                                                                                  |

| OC_MReqInfo[3:0]   | Always 0xA<br>OC_MReqInfo[3] identifies the SYNC, while OC_MReqInfo[2:0] specify an<br>uncached CCA.                      |

| OC_MAddrSpace[1:0] | Always 2'b00 (Normal address space)                                                                                       |

| Table 3.10 | SYNC | Transaction | Signals |

|------------|------|-------------|---------|

|------------|------|-------------|---------|

When the AXI bridge decodes a SYNC request on the OCP interface, it will perform the most complete set of synchronization operations that are defined. This means the bridge does a completion barrier that affects both load and stores preceding the SYNC instruction and both loads and stores that are subsequent to the SYNC instruction. Specifically, when the bridge detects a SYNC transaction it will:

- 1. Decline any additional requests from the processor core.

- 2. Wait until all pending read/write transactions are completed.

3. Issue the read command (SYNC) to the AXI bus. When the response returns, the bridge resumes acceptance of requests from the OCP master.

#### 3.1.6.2 L2/L3 cacheops

The execution of the CACHE instruction, allowing privileged software to manage an L2 or L3 external cache, also results in transactions on the OCP interface. Again, these L2/L3 cache operations are not defined by the OCP interface, and are basically proprietary. However, these operations can only occur when an L2/L3 cache has been enabled, and a CACHE instruction intended for an L2/L3 cache is executed.