# MIPS® Architecture for Programmers Volume IV-j: The MIPS32® SIMD Architecture Module

Document Number: MD00866 Revision 1.12 February 3, 2016

| Public: This publication contains proprietary information which is subject to change without notice and is supplied 'as is', without any warranty of any kind. |                                                                                                                                                                |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                | Public. This publication contains proprietary information which is subject to change without notice and is supplied 'as is', without any warranty of any kind. |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                                                |  |

# **Contents**

| Chapter 1: About This Book                                              | 12 |

|-------------------------------------------------------------------------|----|

| 1.1: Typographical Conventions                                          |    |

| 1.1.1: Italic Text                                                      |    |

| 1.1.2: Bold Text                                                        |    |

| 1.1.3: Courier Text                                                     |    |

| 1.2: UNPREDICTABLE and UNDEFINED                                        |    |

| 1.2.1: UNPREDICTABLE                                                    |    |

| 1.2.2: UNDEFINED                                                        |    |

| 1.2.3: UNSTABLE                                                         |    |

| 1.3: Special Symbols in Pseudocode Notation                             |    |

| 1.4: For More Information                                               |    |

| Chapter 2: Guide to the Instruction Set                                 | 18 |

| 2.1: Understanding the Instruction Fields                               |    |

| 2.1.1: Instruction Fields                                               |    |

| 2.1.2: Instruction Descriptive Name and Mnemonic                        |    |

| 2.1.3: Format Field                                                     |    |

| 2.1.4: Purpose Field                                                    |    |

| 2.1.5: Description Field                                                |    |

| 2.1.6: Restrictions Field.                                              |    |

| 2.1.7: Operation Field                                                  | 22 |

| 2.1.8: Exceptions Field                                                 |    |

| 2.1.9: Programming Notes and Implementation Notes Fields                |    |

| 2.2: Operation Section Notation and Functions                           |    |

| 2.2.1: Instruction Execution Ordering                                   |    |

| 2.2.2: Pseudocode Functions                                             |    |

| 2.3: Op and Function Subfield Notation                                  | 32 |

| 2.4: FPU Instructions                                                   |    |

| Chapter 3: The MIPS32® SIMD Architecture                                | 34 |

| 3.1: Overview                                                           |    |

| 3.2: MSA Software Detection                                             |    |

| 3.3: MSA Vector Registers                                               |    |

| 3.3.1: Registers Layout                                                 |    |

| 3.3.2: Floating-Point Registers Mapping                                 |    |

| 3.4: MSA Control Registers                                              |    |

| 3.4.1: MSA Implementation Register (MSAIR, MSA Control Register 0)      | 40 |

| 3.4.2: MSA Control and Status Register (MSACSR, MSA Control Register 1) | 41 |

| 3.4.3: MSA Access Register (MSAAccess, MSA Control Register 2)          |    |

| 3.4.4: MSA Save Register (MSASave, MSA Control Register 3)              |    |

| 3.4.5: MSA Modify Register (MSAModify, MSA Control Register 4)          |    |

| 3.4.6: MSA Request Register (MSARequest, MSA Control Register 5)        |    |

| 3.4.7: MSA Map Register (MSAMap, MSA Control Register 6)                |    |

| 3.4.8: MSA Unmap Register (MSAUnmap, MSA Control Register 7)            |    |

| 3.5: Exceptions                                                         |    |

| 3.5.1: Handling the MSA Disabled Exception                              |    |

| 3.5.2: Handling the MSA Floating Point Exception                        |    |

| 3.5.3: NaN Propagation                                 |               |

|--------------------------------------------------------|---------------|

| 3.5.4: Flush to Zero and Exception Signaling           | 54            |

| 3.6: Instruction Syntax                                | 54            |

| 3.6.1: Vector Element Selection                        | 55            |

| 3.6.2: Load/Store Offsets                              |               |

| 3.6.3: Instruction Examples                            | 56            |

| 3.7: Instruction Encoding                              |               |

| 3.7.1: Data Format and Index Encoding                  |               |

| 3.7.2: Instruction Formats                             |               |

| 3.7.3: Instruction Bit Encoding                        |               |

|                                                        |               |

| Chapter 4: The MIPS32® SIMD Architecture Instruction S | et 7 <i>4</i> |

| 4.1: Instruction Set Descriptions                      |               |

| 4.1.1: Instruction Set Summary by Category             |               |

| 4.1.2: Alphabetical List of Instructions               |               |

| ADD_A.df                                               |               |

| ADD_A.df                                               |               |

| ADDS_A.dl                                              |               |

|                                                        |               |

| ADDS_U.df.                                             |               |

| ADDV.df                                                |               |

| ADDVI.df                                               |               |

| AND.V                                                  |               |

| ANDI.B                                                 |               |

| ASUB_S.df                                              |               |

| ASUB_U.df                                              |               |

| AVE_S.df                                               |               |

| AVE_U.df                                               |               |

| AVER_S.df                                              |               |

| AVER_U.df                                              |               |

| BCLR.df                                                |               |

| BCLRI.df                                               |               |

| BINSL.df                                               |               |

| BINSLI.df                                              |               |

| BINSR.df                                               |               |

| BINSRI.df                                              |               |

| BMNZ.V                                                 |               |

| BMNZI.B                                                |               |

| BMZ.V                                                  |               |

| BMZI.B                                                 |               |

| BNEG.df                                                | 110           |

| BNEGI.df                                               | 111           |

| BNZ.df                                                 |               |

| BNZ.V                                                  |               |

| BSEL.V                                                 | 114           |

| BSELI.B                                                | 115           |

| BSET.df                                                | 116           |

| BSETI.df                                               |               |

| BZ.df                                                  |               |

| BZ.V                                                   |               |

| CEQ.df.                                                |               |

| CEQI.df.                                               |               |

| CFCMSA                                                 |               |

|                                                        | 195           |

| CLE_U.df   | 126 |

|------------|-----|

| CLEI_S.df  | 127 |

| CLEI_U.df  | 129 |

| CLT_S.df   | 131 |

| CLT U.df   | 132 |

| CLTI_S.df  |     |

| CLTI U.df  |     |

| COPY_S.df  |     |

| COPY_U.df  |     |

| CTCMSA     |     |

| DIV_S.df   |     |

| DIV_G.df   |     |

| DOTP S.df  |     |

| DOTP_S.di  |     |

|            |     |

| DPADD_S.df |     |

| DPADD_U.df |     |

| DPSUB_S.df |     |

| DPSUB_U.df |     |

| FADD.df    |     |

| FCAF.df    |     |

| FCEQ.df    |     |

| FCLASS.df  |     |

| FCLE.df    | 159 |

| FCLT.df    | 160 |

| FCNE.df    | 161 |

| FCOR.df    | 162 |

| FCUEQ.df   | 163 |

| FCULE.df   | 164 |

| FCULT.df   |     |

| FCUN.df    |     |

| FCUNE.df   |     |

| FDIV.df    |     |

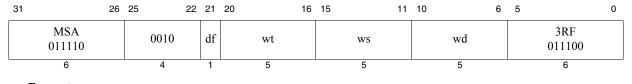

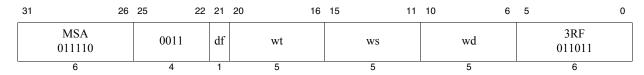

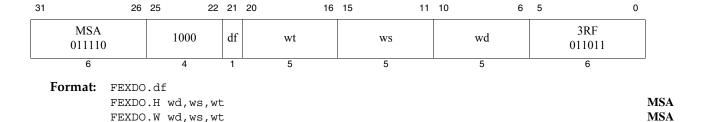

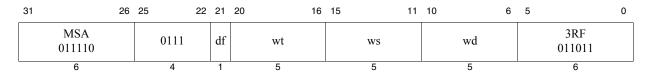

| FEXDO.df   |     |

| FEXP2.df   |     |

| FEXUPL.df  |     |

| FEXUPR.df  |     |

| FFINT_S.df |     |

|            | 175 |

|            |     |

| FFQL.df    |     |

| FFQR.df    |     |

| FILL.df    |     |

| FLOG2.df   |     |

| FMADD.df   |     |

| FMAX.df    |     |

| FMAX_A.df  |     |

| FMIN.df    |     |

| FMIN_A.df  |     |

| FMSUB.df   | 185 |

| FMUL.df    |     |

| FRCP.df    |     |

| FRINT.df.  |     |

| FRSQRT.df  |     |

|            | 191 |

| FSEQ.df          |              |

|------------------|--------------|

| FSLE.df          | . 193        |

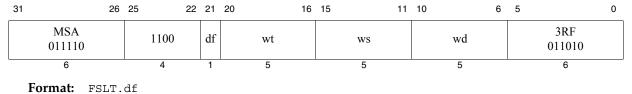

| FSLT.df          | . 194        |

| FSNE.df          | . 195        |

| FSOR.df          |              |

| FSQRT.df         |              |

| FSUB.df.         |              |

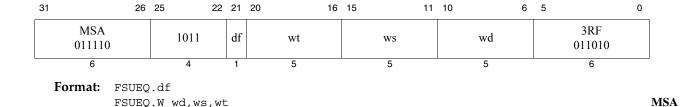

| FSUEQ.df         |              |

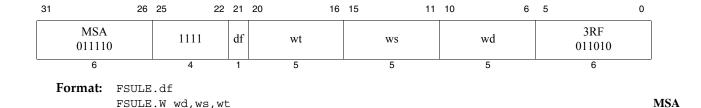

| FSULE.df         |              |

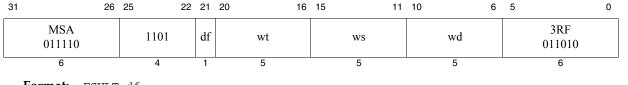

| FSULT.df         |              |

| FSUN.df.         |              |

| FSUNE.df         |              |

| FSUNE.diFSUNE.di |              |

|                  |              |

| FTINT_U.df       |              |

| FTQ.df           |              |

| FTRUNC_S.df      |              |

| FTRUNC_U.df      |              |

| HADD_S.df        |              |

| HADD_U.df        |              |

| HSUB_S.df        | . 213        |

| HSUB_U.df        | . 214        |

| ILVEV.df         | . 215        |

| ILVL.df          | . 217        |

| ILVOD.df         | . 219        |

| ILVR.df          | . 221        |

| INSERT.df        |              |

| INSVE.df         |              |

| LD.df            |              |

| LDI.df           |              |

| LSA.             |              |

| MADD_Q.df        |              |

| MADDR Q.df       |              |

| MADDN_Q.dl       |              |

|                  |              |

| MAX_A.df         |              |

| MAX_S.df         |              |

| MAX_U.df         |              |

| MAXI_S.df        |              |

| <del>-</del>     | . 242        |

| MIN_A.df         |              |

| MIN_S.df         |              |

| MIN_U.df         |              |

| MINI_S.df        |              |

| MINI_U.df        | . 252        |

| MOD_S.df         | . 254        |

| MOD_U.df         | . 255        |

| MOVE.V           |              |

| MSUB_Q.df        |              |

| MSUBR_Q.df       |              |

| MSUBV.df         |              |

| MUL_Q.df         |              |

| MULR_Q.df        |              |

| MULV.df          |              |

| NI OC df         | . 205<br>266 |

|                  |              |

| NLZC.df                                                  | 268 |

|----------------------------------------------------------|-----|

| NOR.V                                                    | 270 |

| NORI.B                                                   | 271 |

| OR.V                                                     | 272 |

| ORI.B.                                                   | 273 |

| PCKEV.df                                                 |     |

| PCKOD.df.                                                | 276 |

| PCNT.df.                                                 | 278 |

| SAT_S.df                                                 | 279 |

| SAT_U.df                                                 |     |

| SHF.df                                                   | 283 |

| SLD.df                                                   | 284 |

| SLDI.df                                                  |     |

| SLL.df                                                   |     |

| SLLI.df                                                  | 289 |

| SPLAT.df                                                 |     |

| SPLATI.df                                                |     |

| SRA.df                                                   |     |

| SRAI.df                                                  | 293 |

| SRAR.df                                                  |     |

| SRARI.df                                                 |     |

| SRL.df                                                   |     |

| SRLI.df                                                  |     |

| SRLR.df.                                                 |     |

| SRLRI.df                                                 |     |

| ST.df                                                    |     |

| SUBS_S.df                                                |     |

| SUBS_U.df                                                |     |

| SUBSUS_U.df                                              |     |

| SUBSUU_S.df.                                             |     |

| SUBV.df.                                                 |     |

| SUBVI.df.                                                |     |

| VSHF.df                                                  |     |

| XOR.V.                                                   |     |

| XORI.B                                                   |     |

|                                                          |     |

| endix A: Vector Registers Partitioning                   | 320 |

| v.1: Vector Registers Mapping                            |     |

| A.2: Saving/Restoring Vector Registers on Context Switch |     |

| A.3: Re-allocating Physical Vector Registers             |     |

| A.4: Heuristic for Vector Register Allocation            |     |

| 1.4. Houristic for voctor riegister Allocation.          | 020 |

| endix B: Revision History                                | 324 |

# **List of Figures**

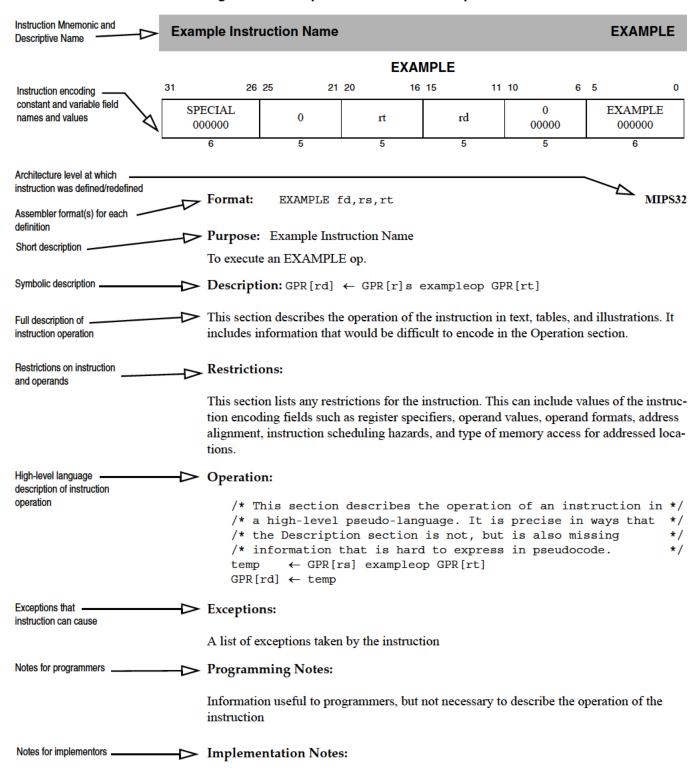

| Figure 2.1: Example of Instruction Description                                                 | 19 |

|------------------------------------------------------------------------------------------------|----|

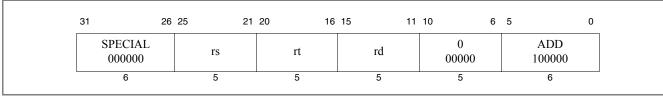

| Figure 2.2: Example of Instruction Fields                                                      | 20 |

| Figure 2.3: Example of Instruction Descriptive Name and Mnemonic                               | 20 |

| Figure 2.4: Example of Instruction Format                                                      |    |

| Figure 2.5: Example of Instruction Purpose                                                     | 21 |

| Figure 2.6: Example of Instruction Description                                                 | 21 |

| Figure 2.7: Example of Instruction Restrictions                                                |    |

| Figure 2.8: Example of Instruction Operation                                                   |    |

| Figure 2.9: Example of Instruction Exception                                                   |    |

| Figure 2.10: Example of Instruction Programming Notes                                          | 23 |

| Figure 2.11: COP_LW Pseudocode Function                                                        |    |

| Figure 2.12: COP_LD Pseudocode Function                                                        |    |

| Figure 2.13: COP_SW Pseudocode Function                                                        |    |

| Figure 2.14: COP_SD Pseudocode Function                                                        |    |

| Figure 2.15: CoprocessorOperation Pseudocode Function                                          |    |

| Figure 2.16: AddressTranslation Pseudocode Function                                            |    |

| Figure 2.17: LoadMemory Pseudocode Function                                                    |    |

| Figure 2.18: StoreMemory Pseudocode Function                                                   |    |

| Figure 2.19: Prefetch Pseudocode Function                                                      |    |

| Figure 2.20: SyncOperation Pseudocode Function                                                 |    |

| Figure 2.21: ValueFPR Pseudocode Function                                                      |    |

| Figure 2.22: StoreFPR Pseudocode Function                                                      |    |

| Figure 2.23: CheckFPException Pseudocode Function                                              |    |

| Figure 2.24: FPConditionCode Pseudocode Function                                               |    |

| Figure 2.25: SetFPConditionCode Pseudocode Function                                            |    |

| Figure 2.26: SignalException Pseudocode Function                                               |    |

| Figure 2.27: SignalDebugBreakpointException Pseudocode Function                                |    |

| Figure 2.28: SignalDebugModeBreakpointException Pseudocode Function                            |    |

| Figure 2.29: NullifyCurrentInstruction PseudoCode Function                                     |    |

| Figure 2.30: JumpDelaySlot Pseudocode Function                                                 |    |

| Figure 2.31: PolyMult Pseudocode Function                                                      |    |

| Figure 3-1: Config3 (CP0 Register 16, Select 3) MSA Implementation Present Bit                 |    |

| Figure 3-2: Config5 (CP0 Register 16, Select 5) MSA Enable Bit                                 | 35 |

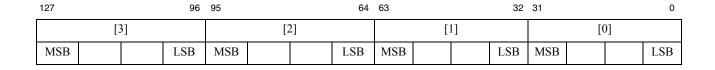

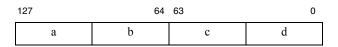

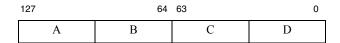

| Figure 3-3: MSA Vector Register Byte Elements                                                  | 36 |

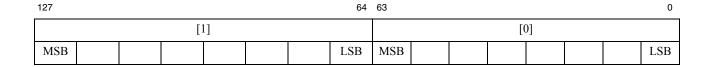

| Figure 3-4: MSA Vector Register Halfword Elements                                              |    |

| Figure 3-5: MSA Vector Register Word Elements                                                  |    |

| Figure 3-6: MSA Vector Register Doubleword Elements                                            |    |

| Figure 3-7: MSA Vector Register as 2-Row Byte Array                                            |    |

| Figure 3-8: MSA Vector Register as 4-Row Byte Array                                            |    |

| Figure 3-9: MSA Vector Register as 8-Row Byte Array                                            |    |

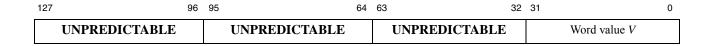

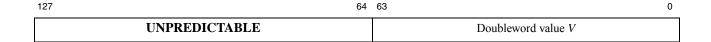

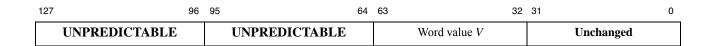

| Figure 3-10: FPU Word Write Effect on the MSA Vector Register (Status <sub>FR</sub> set)       |    |

| Figure 3-11: FPU Doubleword Write Effect on the MSA Vector Register (Status <sub>FR</sub> set) |    |

| Figure 3-12: FPU High Word Write Effect on the MSA Vector Register (Status <sub>FR</sub> set)  |    |

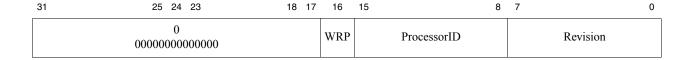

| Figure 3-13: MSAIR Register Format                                                             |    |

| Figure 3-14: MSAIR Register Field Descriptions                                                 |    |

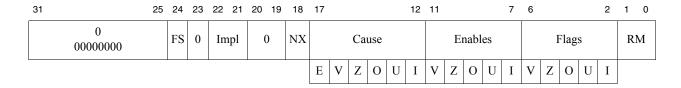

| Figure 3-15: MSACSR Register Format                                                            |    |

| Figure 3-16: MSACSR Register Field Descriptions                                                | 42 |

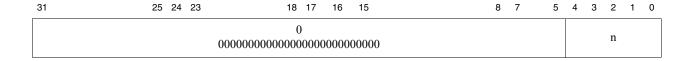

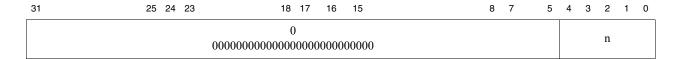

| <b>Figure</b> | 3-17: | MSAAccess Register Format                             | 46 |

|---------------|-------|-------------------------------------------------------|----|

| Figure        | 3-18: | MSASave Register Format                               | 46 |

|               |       | MSAModify Register Format                             |    |

| Figure        | 3-20: | MSARequest Register Format                            | 47 |

|               |       | MSAMap Register Format                                |    |

| Figure        | 3-22: | MSAMap Register Field Descriptions                    | 48 |

| Figure        | 3-23: | MSAUnmap Register Format                              | 48 |

|               |       | MSAUnmap Register Field Descriptions                  |    |

| Figure        | 3-25: | Output Format for Faulting Elements when NX is set    | 50 |

| Figure        | 3.26: | MSACSRCause Update Pseudocode                         | 52 |

| Figure        | 3.27: | MSACSRFlags Update and Exception Signaling Pseudocode | 53 |

|               |       | Source Vector \$w1 Values                             |    |

| Figure        | 3-29: | Source Vector \$w2 Values                             | 56 |

| Figure        | 3-30: | Source GPR \$2 Value                                  | 56 |

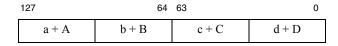

| Figure        | 3-31: | Destination Vector \$w5 Value for ADDV.W Instruction  | 56 |

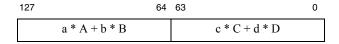

| Figure        | 3-35: | Destination Vector \$w9 Value for DOTP_S Instruction  | 57 |

| Figure        | 3-32: | Destination Vector \$w6 Value for FILL.W Instruction  | 57 |

| Figure        | 3-33: | Destination Vector \$w7 Value for ADDVI.W Instruction | 57 |

|               |       | Destination Vector \$w8 Value for SPLAT.W Instruction |    |

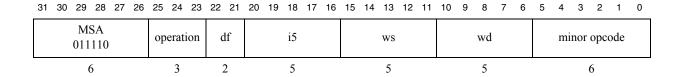

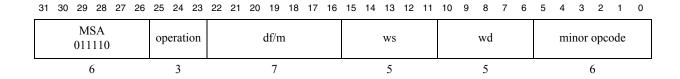

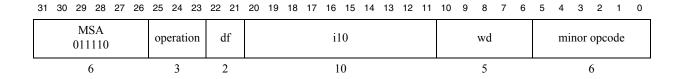

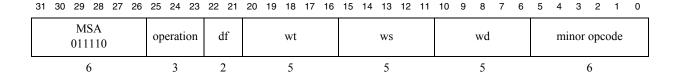

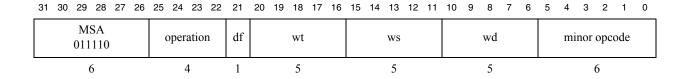

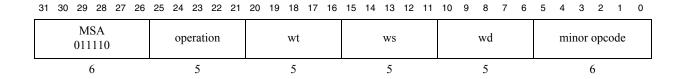

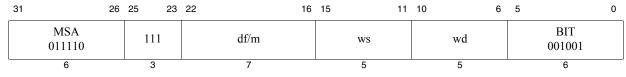

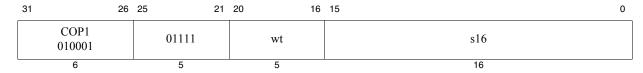

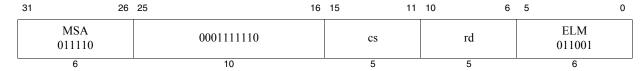

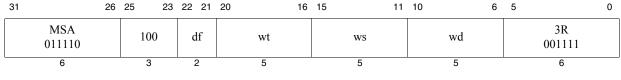

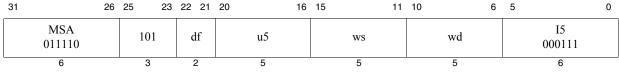

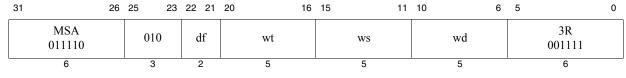

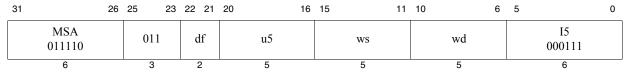

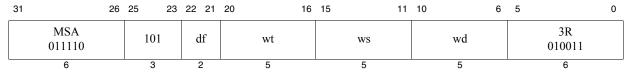

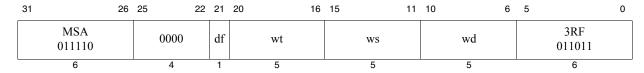

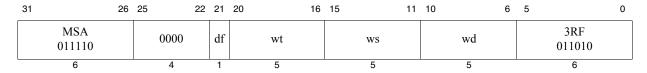

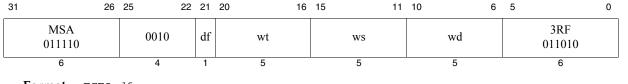

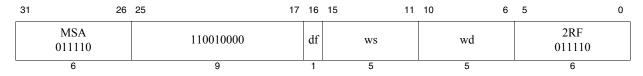

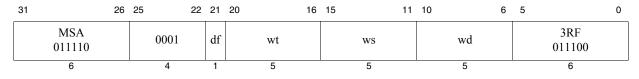

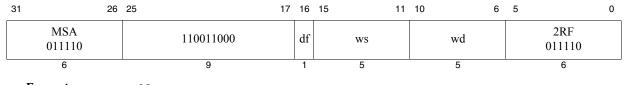

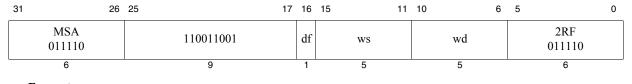

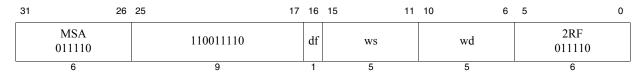

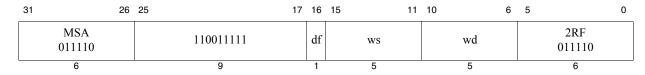

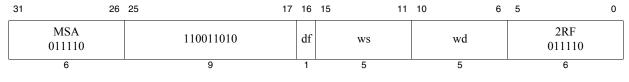

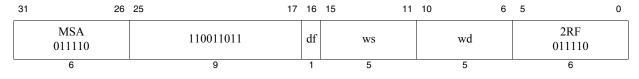

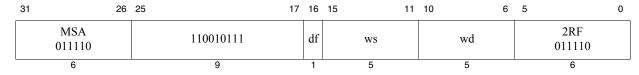

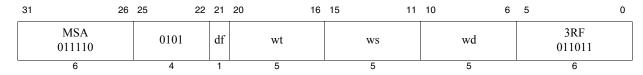

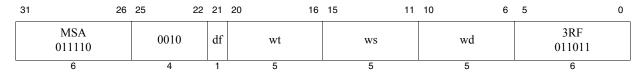

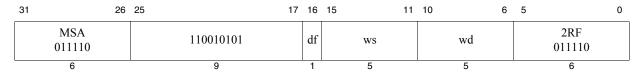

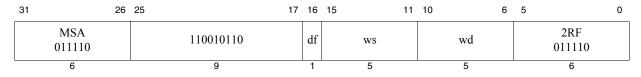

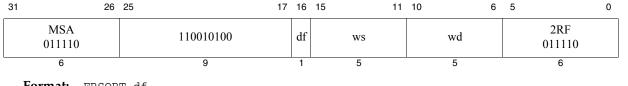

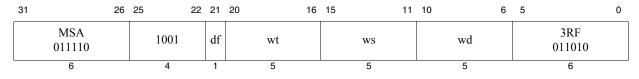

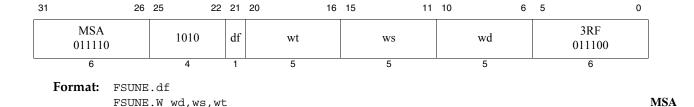

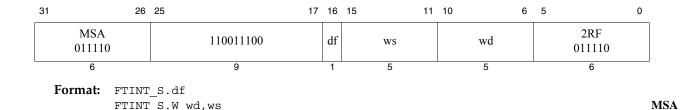

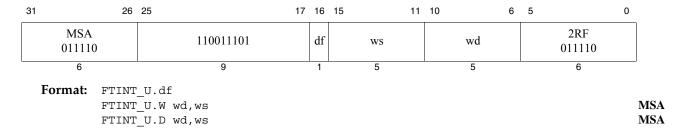

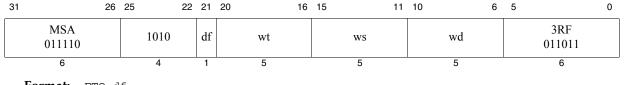

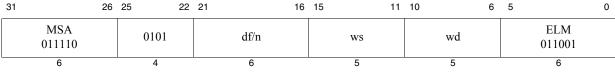

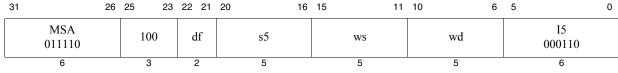

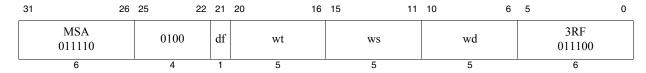

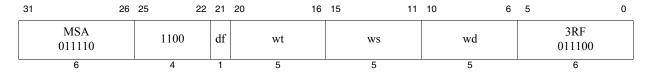

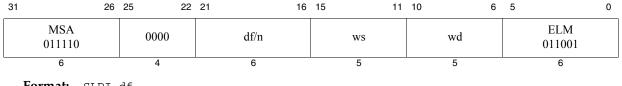

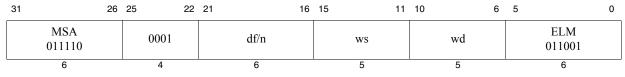

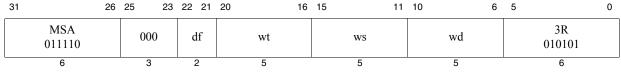

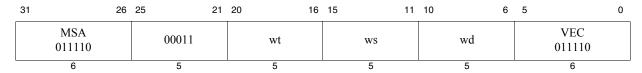

|               |       | 18 Instruction Format                                 |    |

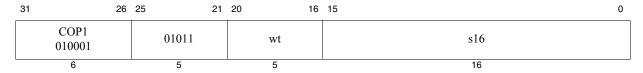

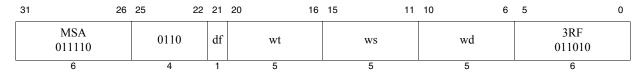

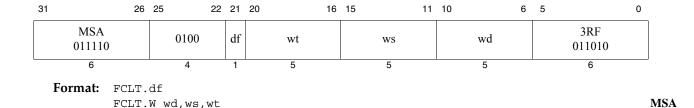

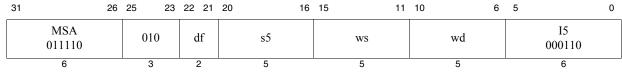

| Figure        | 3-37: | 15 Instruction Format                                 | 60 |

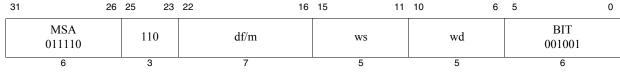

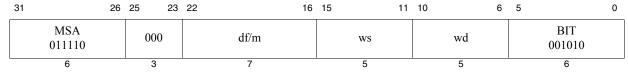

| Figure        | 3-38: | BIT Instruction Format                                | 60 |

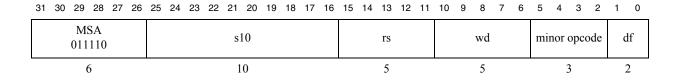

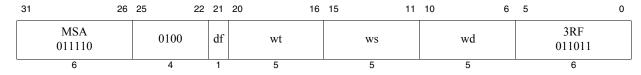

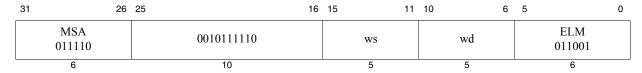

| Figure        | 3-39: | I10 Instruction Format                                | 60 |

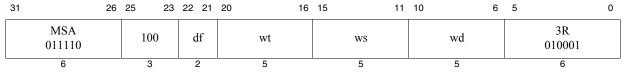

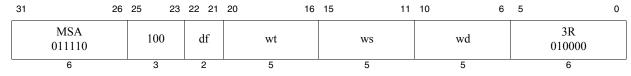

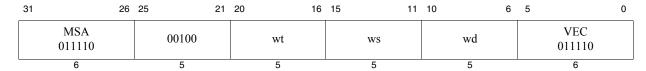

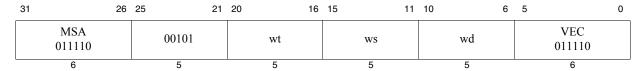

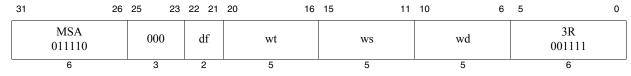

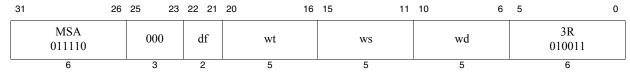

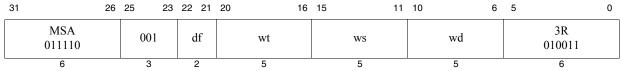

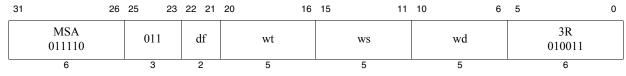

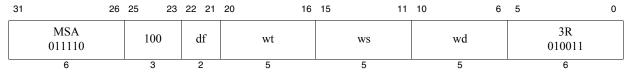

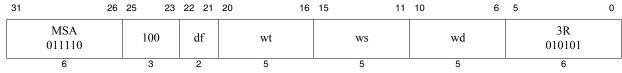

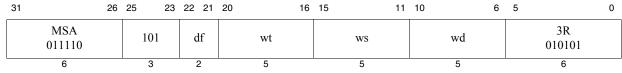

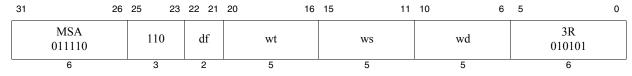

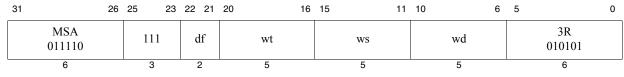

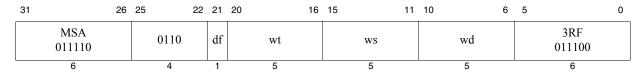

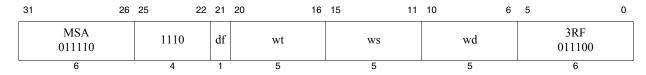

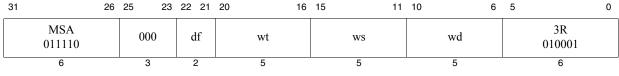

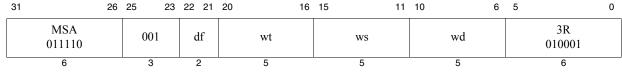

| Figure        | 3-40: | 3R Instruction Format                                 | 60 |

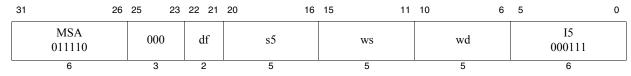

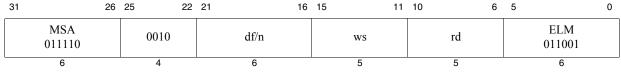

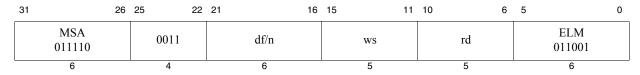

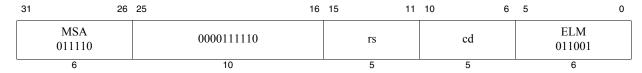

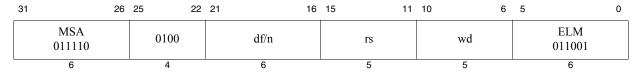

| Figure        | 3-41: | ELM Instruction Format                                | 61 |

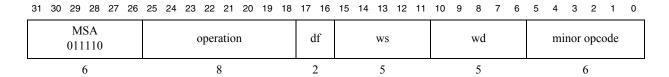

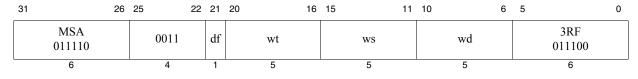

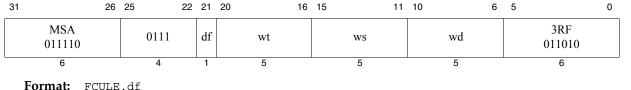

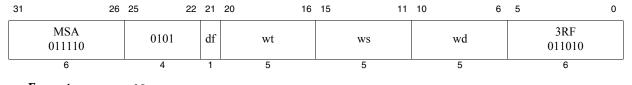

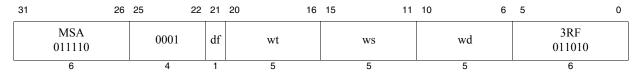

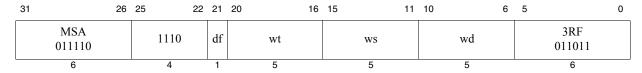

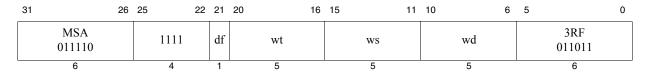

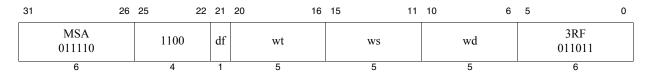

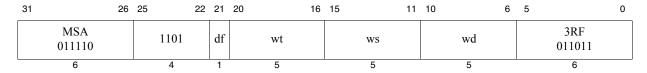

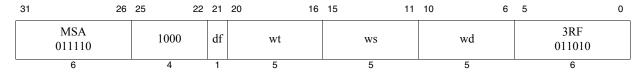

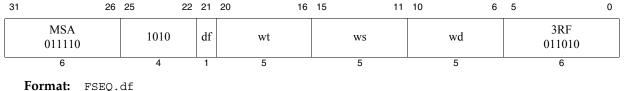

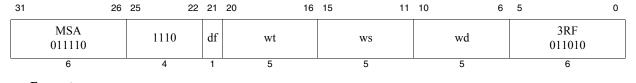

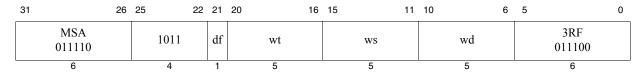

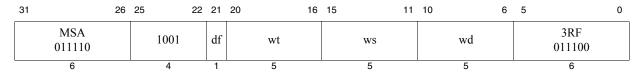

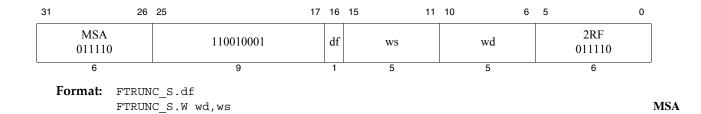

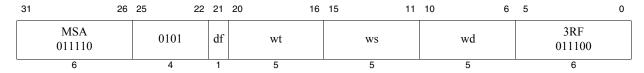

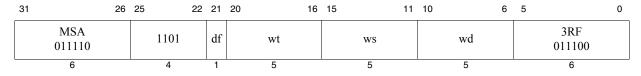

| Figure        | 3-42: | 3RF Instruction Format                                | 61 |

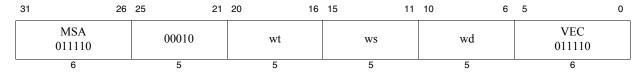

| Figure        | 3-43: | VEC Instruction Format                                | 61 |

| Figure        | 3-44: | MI10 Instruction Format                               | 61 |

|               |       | 2R Instruction Format                                 |    |

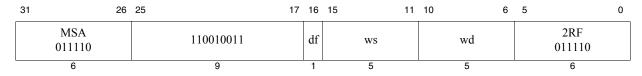

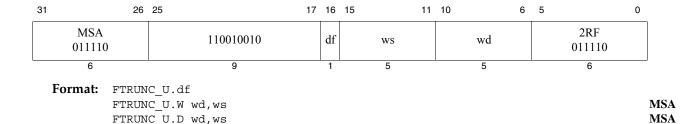

|               |       | 2RF Instruction Format                                |    |

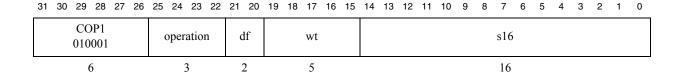

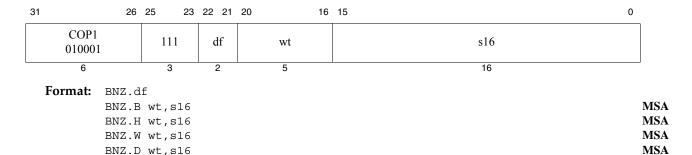

|               |       | Branch Instruction Format                             |    |

| Figure        | 3.48: | Sample Bit Encoding Table                             | 63 |

# **List of Tables**

| Table 1.1: Symbols Used in Instruction Operation Statements                               | 14  |

|-------------------------------------------------------------------------------------------|-----|

| Table 2.1: AccessLength Specifications for Loads/Stores                                   | 27  |

| Table 3.1: Word Vector Memory Representation                                              | 38  |

| Table 3.2: MSA Control Registers                                                          |     |

| Table 3.3: Cause, Enable, and Flag Bit Definitions                                        |     |

| Table 3.4: Rounding Modes Definitions                                                     | 45  |

| Table 3.5: MSA Exception Code (ExcCode) Values                                            |     |

| Table 3.6: Default Values for Floating Point Exceptions                                   | 51  |

| Table 3.7: Default NaN Encodings                                                          |     |

| Table 3.8: Data Format Abbreviations                                                      |     |

| Table 3.9: Valid Element Index Values                                                     |     |

| Table 3.10: Two-bit Data Format Field Encoding                                            |     |

| Table 3.11: Halfword/Word Data Format Field Encoding                                      |     |

| Table 3.12: Word/Doubleword Data Format Field Encoding                                    |     |

| Table 3.13: Data Format and Element Index Field Encoding                                  |     |

| Table 3.14: Data Format and Bit Index Field Encoding                                      |     |

| Table 3.15: Symbols Used in the Instruction Encoding Tables                               | 63  |

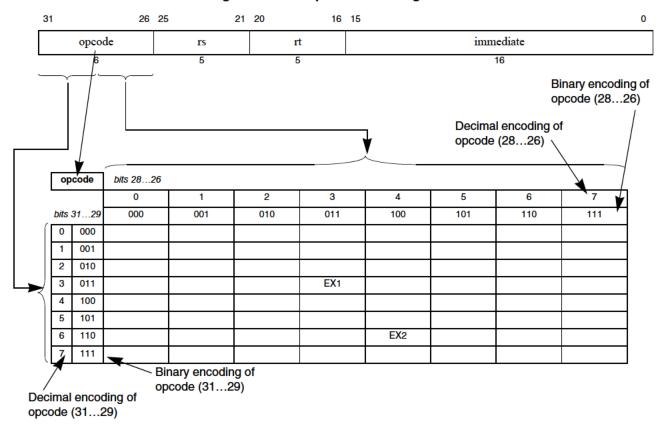

| Table 3.16: MIPS32 Encoding of the Opcode Field                                           | 64  |

| Table 3.17: MIPS32 COP1 Encoding of rs Field for MSA Branch Instructions                  | 64  |

| Table 3.18: Encoding of MIPS MSA Minor Opcode Field                                       |     |

| Table 3.19: Encoding of Operation Field for MI10 Instruction Formats                      |     |

| Table 3.20: Encoding of Operation Field for I5 Instruction Format                         |     |

| Table 3.21: Encoding of Operation Field for I8 Instruction Format                         |     |

| Table 3.22: Encoding of Operation Field for VEC/2R/2RF Instruction Formats                |     |

| Table 3.23: Encoding of Operation Field for 2R Instruction Formats                        |     |

| Table 3.24: Encoding of Operation Field for 2RF Instruction Formats                       |     |

| Table 3.25: Encoding of Operation Field for 3R Instruction Format                         |     |

| Table 3.26: Encoding of Operation Field for ELM Instruction Format                        |     |

| Table 3.27: Encoding of Operation Field for 3RF Instruction Format                        | 71  |

| Table 3.28: Encoding of Operation Field for BIT Instruction Format                        | 72  |

| Table 4.1: MSA Integer Arithmetic Instructions                                            |     |

| Table 4.2: MSA Bitwise Instructions                                                       |     |

| Table 4.3: MSA Floating-Point Arithmetic Instructions                                     |     |

| Table 4.4: MSA Floating-Point Non Arithmetic Instructions                                 |     |

| Table 4.5: MSA Floating-Point Compare Instructions                                        |     |

| Table 4.6: MSA Floating-Point Conversion Instructions                                     |     |

| Table 4.7: MSA Fixed-Point Instructions                                                   |     |

| Table 4.8: MSA Branch and Compare Instructions                                            |     |

| Table 4.9: MSA Load/Store and Move Instructions                                           |     |

| Table 4.10: MSA Element Permute Instructions                                              |     |

| Table 4.11: Base Architecture Instructions                                                |     |

| Table A.1: Physical-to-Thread Context Vector Register Mapping (Hardware Internal)         |     |

| Table A.2: Updated Physical-to-Thread Context Vector Register Mapping (Hardware Internal) |     |

| Table A.3: Context Mapping Table (OS Internal)                                            |     |

| Table A.4: Register Usage Table (OS Internal)                                             | 322 |

| Table A.5: Updated Context Mapping Table (OS Internal)                                    |     |

| Table A.6: Updated Register Usage Table (OS Internal)                                     | 323 |

# **About This Book**

The MIPS® Architecture for Programmers Volume IV-j: The MIPS32® SIMD Architecture Module comes as part of a multi-volume set.

- Volume I-A describes conventions used throughout the document set, and provides an introduction to the MIPS32® Architecture

- Volume I-B describes conventions used throughout the document set, and provides an introduction to the microMIPS32<sup>TM</sup> Architecture

- Volume II-A provides detailed descriptions of each instruction in the MIPS32® instruction set

- Volume II-B provides detailed descriptions of each instruction in the microMIPS32<sup>TM</sup> instruction set

- Volume III describes the MIPS32® and microMIPS32<sup>TM</sup> Privileged Resource Architecture which defines and governs the behavior of the privileged resources included in a MIPS® processor implementation

- Volume IV-a describes the MIPS16e<sup>TM</sup> Application-Specific Extension to the MIPS32® Architecture. Beginning with Release 3 of the Architecture, microMIPS is the preferred solution for smaller code size.

- Volume IV-b describes the MDMX<sup>TM</sup> Application-Specific Extension to the MIPS64® Architecture and microMIPS64<sup>TM</sup>. It is not applicable to the MIPS32® document set nor the microMIPS32<sup>TM</sup> document set. With Release 5 of the Architecture, MDMX is deprecated. MDMX and MSA can not be implemented at the same time.

- Volume IV-c describes the MIPS-3D® Application-Specific Extension to the MIPS® Architecture

- Volume IV-d describes the SmartMIPS®Application-Specific Extension to the MIPS32® Architecture and the microMIPS32™ Architecture .

- Volume IV-e describes the MIPS® DSP Module to the MIPS® Architecture

- Volume IV-f describes the MIPS® MT Module to the MIPS® Architecture

- Volume IV-h describes the MIPS® MCU Application-Specific Extension to the MIPS® Architecture

- Volume IV-i describes the MIPS® Virtualization Module to the MIPS® Architecture

- Volume IV-j describes the MIPS® SIMD Architecture Module to the MIPS® Architecture

# 1.1 Typographical Conventions

This section describes the use of *italic*, **bold** and courier fonts in this book.

#### 1.1.1 Italic Text

- is used for *emphasis*

- is used for *bits*, *fields*, *registers*, that are important from a software perspective (for instance, address bits used by software, and programmable fields and registers), and various *floating point instruction formats*, such as *S*, *D*, and *PS*

- is used for the memory access types, such as cached and uncached

#### 1.1.2 Bold Text

- represents a term that is being defined

- is used for **bits** and **fields** that are important from a hardware perspective (for instance, **register** bits, which are not programmable but accessible only to hardware)

- is used for ranges of numbers; the range is indicated by an ellipsis. For instance, **5..1** indicates numbers 5 through

- is used to emphasize UNPREDICTABLE and UNDEFINED behavior, as defined below.

#### 1.1.3 Courier Text

Courier fixed-width font is used for text that is displayed on the screen, and for examples of code and instruction pseudocode.

### 1.2 UNPREDICTABLE and UNDEFINED

The terms **UNPREDICTABLE** and **UNDEFINED** are used throughout this book to describe the behavior of the processor in certain cases. **UNDEFINED** behavior or operations can occur only as the result of executing instructions in a privileged mode (i.e., in Kernel Mode or Debug Mode, or with the CP0 usable bit set in the Status register). Unprivileged software can never cause **UNDEFINED** behavior or operations. Conversely, both privileged and unprivileged software can cause **UNPREDICTABLE** results or operations.

#### 1.2.1 UNPREDICTABLE

**UNPREDICTABLE** results may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. Software can never depend on results that are **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause a result to be generated or not. If a result is generated, it is **UNPREDICTABLE**. **UNPREDICTABLE** operations may cause arbitrary exceptions.

**UNPREDICTABLE** results or operations have several implementation restrictions:

- Implementations of operations generating **UNPREDICTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

- UNPREDICTABLE operations must not read, write, or modify the contents of memory or internal state which

is inaccessible in the current processor mode. For example, UNPREDICTABLE operations executed in user

mode must not access memory or internal state that is only accessible in Kernel Mode or Debug Mode or in

another process

UNPREDICTABLE operations must not halt or hang the processor

#### 1.2.2 UNDEFINED

**UNDEFINED** operations or behavior may vary from processor implementation to implementation, instruction to instruction, or as a function of time on the same implementation or instruction. **UNDEFINED** operations or behavior may vary from nothing to creating an environment in which execution can no longer continue. **UNDEFINED** operations or behavior may cause data loss.

**UNDEFINED** operations or behavior has one implementation restriction:

• **UNDEFINED** operations or behavior must not cause the processor to hang (that is, enter a state from which there is no exit other than powering down the processor). The assertion of any of the reset signals must restore the processor to an operational state

#### 1.2.3 UNSTABLE

+, -

**UNSTABLE** results or values may vary as a function of time on the same implementation or instruction. Unlike **UNPREDICTABLE** values, software may depend on the fact that a sampling of an **UNSTABLE** value results in a legal transient value that was correct at some point in time prior to the sampling.

**UNSTABLE** values have one implementation restriction:

• Implementations of operations generating **UNSTABLE** results must not depend on any data source (memory or internal state) which is inaccessible in the current processor mode

# 1.3 Special Symbols in Pseudocode Notation

In this book, algorithmic descriptions of an operation are described as pseudocode in a high-level language notation resembling Pascal. Special symbols used in the pseudocode notation are listed in Table 1.1.

**Symbol** Meaning Assignment Tests for equality and inequality =, ≠ Bit string concatenation A y-bit string formed by y copies of the single-bit value x  $\mathbf{x}^{\mathbf{y}}$ b#n A constant value n in base b. For instance 10#100 represents the decimal value 100, 2#100 represents the binary value 100 (decimal 4), and 16#100 represents the hexadecimal value 100 (decimal 256). If the "b#" prefix is omitted, the default base is 10. 0bn A constant value n in base 2. For instance 0b100 represents the binary value 100 (decimal 4). 0xnA constant value n in base 16. For instance 0x100 represents the hexadecimal value 100 (decimal 256). Selection of bits y through z of bit string x. Little-endian bit notation (rightmost bit is 0) is used. If y is less  $x_{y\ z}$

**Table 1.1 Symbols Used in Instruction Operation Statements**

than z, this expression is an empty (zero length) bit string.

2's complement or floating point arithmetic: addition, subtraction

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol        | Meaning                                                                                                                                                                                                                                                                                       |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *, ∞          | 2's complement or floating point multiplication (both used for either)                                                                                                                                                                                                                        |

| div           | 2's complement integer division                                                                                                                                                                                                                                                               |

| mod           | 2's complement modulo                                                                                                                                                                                                                                                                         |

| /             | Floating point division                                                                                                                                                                                                                                                                       |

| <             | 2's complement less-than comparison                                                                                                                                                                                                                                                           |

| >             | 2's complement greater-than comparison                                                                                                                                                                                                                                                        |

| ≤             | 2's complement less-than or equal comparison                                                                                                                                                                                                                                                  |

| ≥             | 2's complement greater-than or equal comparison                                                                                                                                                                                                                                               |

| nor           | Bitwise logical NOR                                                                                                                                                                                                                                                                           |

| xor           | Bitwise logical XOR                                                                                                                                                                                                                                                                           |

| and           | Bitwise logical AND                                                                                                                                                                                                                                                                           |

| or            | Bitwise logical OR                                                                                                                                                                                                                                                                            |

| not           | Bitwise inversion                                                                                                                                                                                                                                                                             |

| &&            | Logical (non-Bitwise) AND                                                                                                                                                                                                                                                                     |

| <<            | Logical Shift left (shift in zeros at right-hand-side)                                                                                                                                                                                                                                        |

| >>            | Logical Shift right (shift in zeros at left-hand-side)                                                                                                                                                                                                                                        |

| GPRLEN        | The length in bits (32 or 64) of the CPU general-purpose registers                                                                                                                                                                                                                            |

| GPR[x]        | CPU general-purpose register $x$ . The content of $GPR[0]$ is always zero. In Release 2 of the Architecture, $GPR[x]$ is a short-hand notation for $SGPR[SRSCtl_{CSS}, x]$ .                                                                                                                  |

| SGPR[s,x]     | In Release 2 of the Architecture and subsequent releases, multiple copies of the CPU general-purpose registers may be implemented. SGPR[s,x] refers to GPR set s, register x.                                                                                                                 |

| FPR[x]        | Floating Point operand register x                                                                                                                                                                                                                                                             |

| FCC[CC]       | Floating Point condition code CC. FCC[0] has the same value as COC[1].                                                                                                                                                                                                                        |

| FPR[x]        | Floating Point (Coprocessor unit 1), general register <i>x</i>                                                                                                                                                                                                                                |

| CPR[z,x,s]    | Coprocessor unit z, general register x, select s                                                                                                                                                                                                                                              |

| CP2CPR[x]     | Coprocessor unit 2, general register x                                                                                                                                                                                                                                                        |

| CCR[z,x]      | Coprocessor unit z, control register x                                                                                                                                                                                                                                                        |

| CP2CCR[x]     | Coprocessor unit 2, control register <i>x</i>                                                                                                                                                                                                                                                 |

| COC[z]        | Coprocessor unit z condition signal                                                                                                                                                                                                                                                           |

| Xlat[x]       | Translation of the MIPS16e GPR number x into the corresponding 32-bit GPR number                                                                                                                                                                                                              |

| BigEndianMem  | Endian mode as configured at chip reset (0 →Little-Endian, 1 → Big-Endian). Specifies the endianness of the memory interface (see LoadMemory and StoreMemory pseudocode function descriptions), and the endianness of Kernel and Supervisor mode execution.                                   |

| BigEndianCPU  | The endianness for load and store instructions (0 $\rightarrow$ Little-Endian, 1 $\rightarrow$ Big-Endian). In User mode, this endianness may be switched by setting the <i>RE</i> bit in the <i>Status</i> register. Thus, BigEndianCPU may be computed as (BigEndianMem XOR ReverseEndian). |

| ReverseEndian | Signal to reverse the endianness of load and store instructions. This feature is available in User mode only, and is implemented by setting the <i>RE</i> bit of the <i>Status</i> register. Thus, ReverseEndian may be computed as (SR <sub>RE</sub> and User mode).                         |

**Table 1.1 Symbols Used in Instruction Operation Statements (Continued)**

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                                                                                                                                                                                 |                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| LLbit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | set when a linked load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | occurs and | y operation for instructions that provide atomic read-mo<br>is tested by the conditional store. It is cleared, during ot<br>d no longer be atomic. In particular, it is cleared by exce         | her CPU operation,                                                                                                                         |

| I:, I+n:, This occurs as a prefix to <i>Operation</i> description lines and functions as a label. It indicates the instruct during which the pseudocode appears to "execute." Unless otherwise indicated, all effects of the cur instruction appear to occur during the instruction time of the current instruction. No label is equivaled time label of I. Sometimes effects of an instruction appear to occur either earlier or later — that is, durinstruction time of another instruction. When this happens, the instruction operation is written in second labeled with the instruction time, relative to the current instruction I, in which the effect of that pseudoppears to occur. For example, an instruction may have a result that is not available until after the nexinstruction. Such an instruction has the portion of the instruction operation description that writes the register in a section labeled I+1.  The effect of pseudocode statements for the current instruction labelled I+1 appears to occur "at the time" as the effect of pseudocode statements labeled I for the following instruction. Within one pseudocode, the effects of the statements take place in order. However, between sequences of statement ferent instructions that occur "at the same time," there is no defined order. Programs must not dependent particular order of evaluation between such sections. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | s of the current l is equivalent to a — that is, during the ritten in sections of that pseudocode after the next at writes the result ccur "at the same in one pseudocode f statements for dif- |                                                                                                                                            |

| PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PC The <i>Program Counter</i> value. During the instruction time of an instruction, this is the address of the tion word. The address of the instruction that occurs during the next instruction time is determined by ing a value to <i>PC</i> during an instruction time. If no value is assigned to <i>PC</i> during an instruction time pseudocode statement, it is automatically incremented by either 2 (in the case of a 16-bit MIPS16e tion) or 4 before the next instruction time. A taken branch assigns the target address to the <i>PC</i> during instruction time of the instruction in the branch delay slot.  In the MIPS Architecture, the PC value is only visible indirectly, such as when the processor stores the address into a GPR on a jump-and-link or branch-and-link instruction, or into a Coprocessor 0 regists exception. The PC value contains a full 32-bit address all of which are significant during a memory ence.  ISA Mode  In processors that implement the MIPS16e Application Specific Extension or the microMIPS base at tures, the <i>ISA Mode</i> is a single-bit register that determines in which mode the processor is executing lows: |            |                                                                                                                                                                                                 | termined by assign-<br>ruction time by any<br>MIPS16e instruc-<br>e <i>PC</i> during the<br>sor stores the restart<br>sor 0 register on an |

| ISA Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |                                                                                                                                                                                                 |                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ncoding    | Meaning                                                                                                                                                                                         |                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0          | The processor is executing 32-bit MIPS instructions                                                                                                                                             |                                                                                                                                            |