# MIPS32® interAptiv™ Multiprocessing System Software User's Manual

Document Number: MD00904 Revision 02.01 June 15, 2016

| suppli |

|--------|

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

# **Table of Contents**

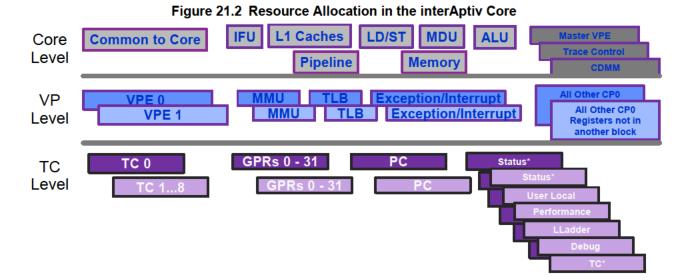

| Chapter 1: Architecture Overview                | 27 |

|-------------------------------------------------|----|

| 1.1: Features                                   |    |

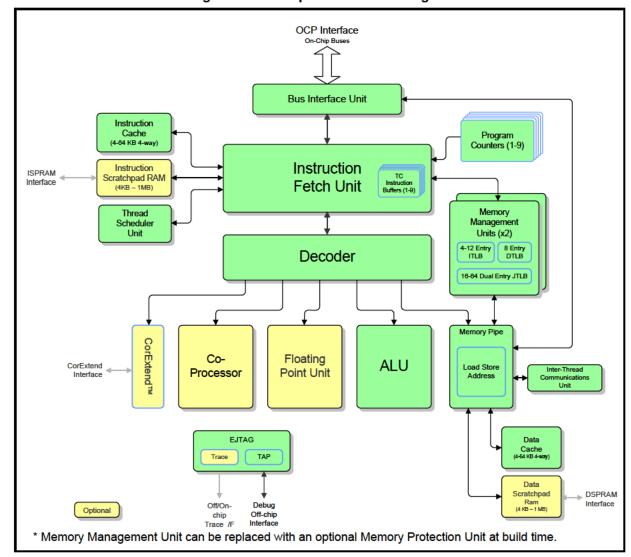

| 1.1.1: System Level Features                    | 28 |

| 1.1.2: Core Level Features                      | 29 |

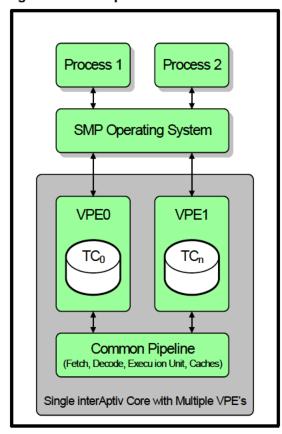

| 1.2: interAptiv Core                            | 30 |

| 1.2.1: MIPS Multi-Thread Technology             |    |

| 1.2.2: Instruction Fetch Unit                   |    |

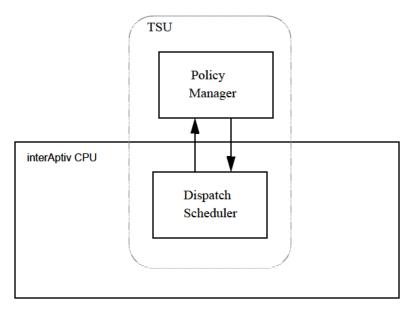

| 1.2.3: Thread Scheduling Unit (TSU)             |    |

| 1.2.4: Policy Manager                           |    |

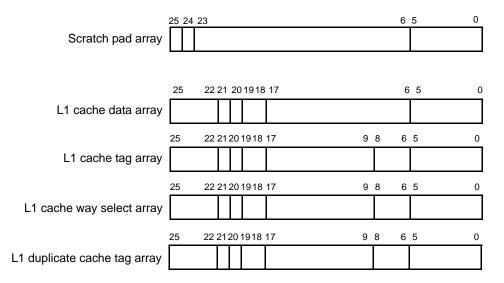

| 1.2.5: interAptiv L1 Caches                     |    |

| 1.2.5.1: Level 1 Instruction Cache              |    |

| 1.2.5.2: Level 1 Data Cache                     | 33 |

| 1.2.5.3: Level 1 Cache Memory Configuration     |    |

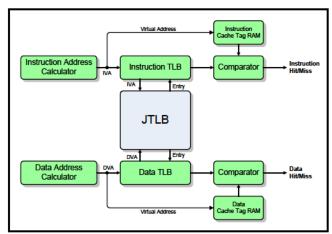

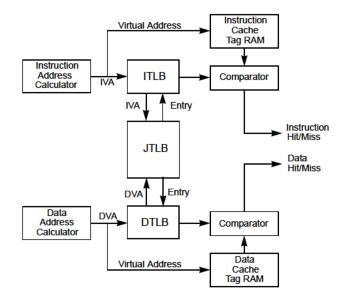

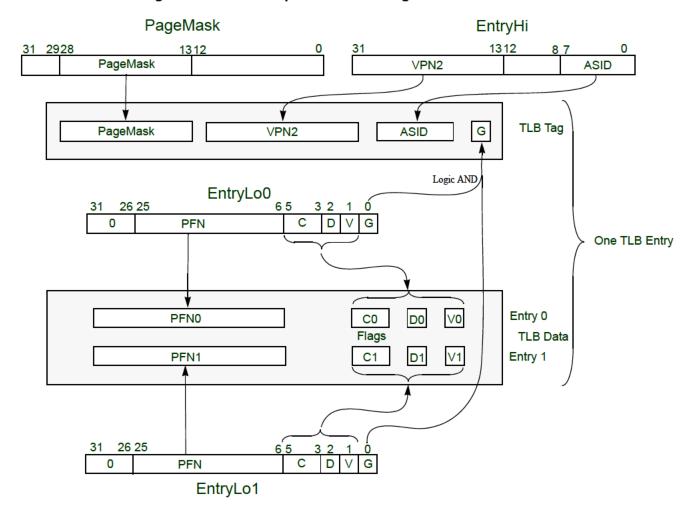

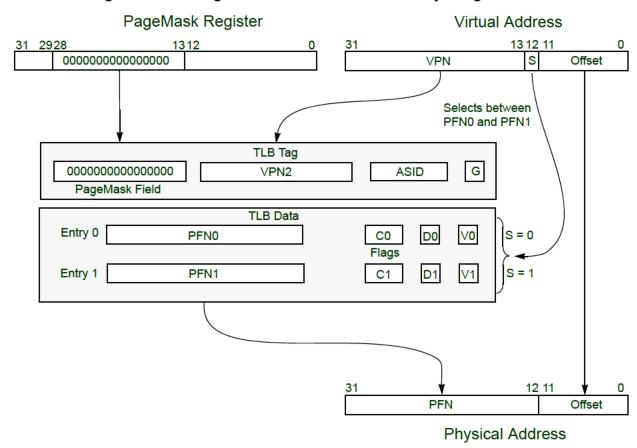

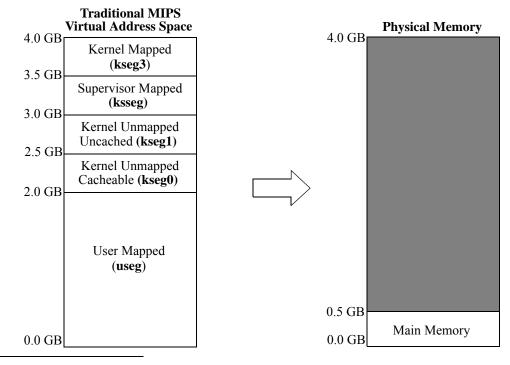

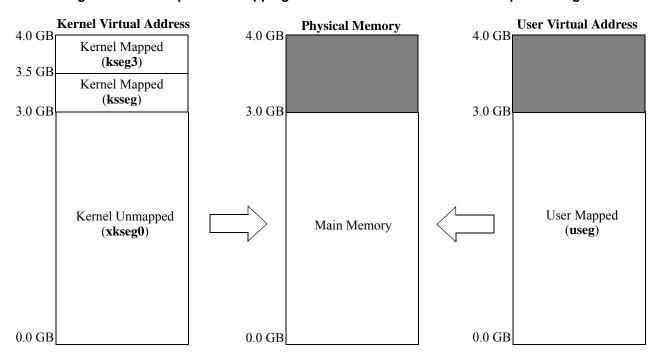

| 1.2.6: Memory Management Unit (MMU)             | 34 |

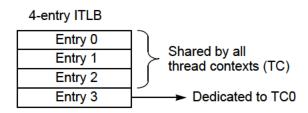

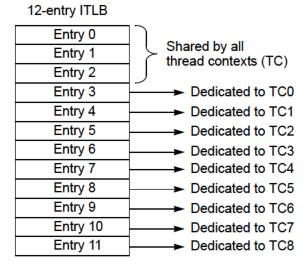

| 1.2.6.1: Instruction TLB (ITLB)                 |    |

| 1.2.6.2: Data TLB (DTLB)                        |    |

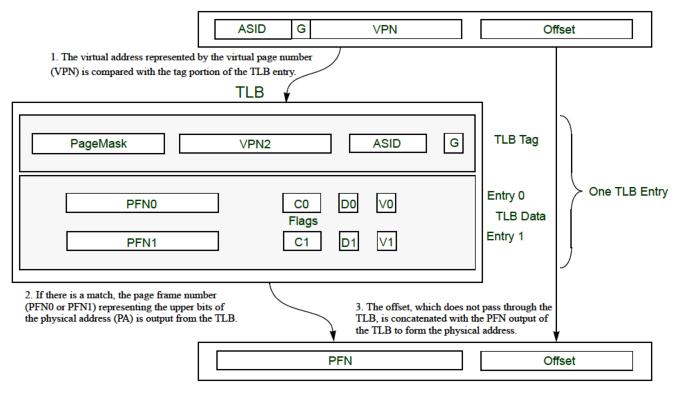

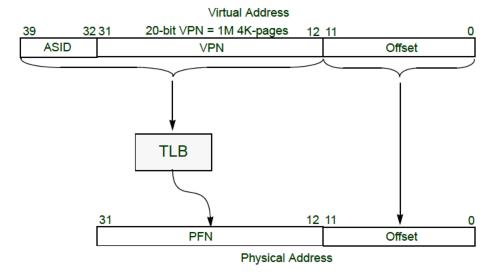

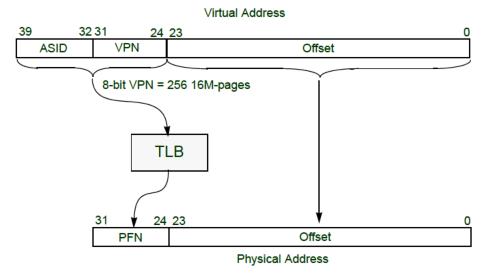

| 1.2.6.3: Translation Lookaside Buffer (TLB)     |    |

| 1.2.6.4: Joint TLB (JTLB)                       | 35 |

| 1.2.7: Memory Protection Unit                   | 36 |

| 1.2.8: Execution Pipelines                      | 36 |

| 1.2.9: Instruction and Data Scratch Pad RAM     | 36 |

| 1.2.10: Inter-thread Communication Unit (ITU)   | 36 |

| 1.2.11: Bus Interface (BIU)                     |    |

| 1.2.11.1: Write Buffer                          | 37 |

| 1.2.11.2: SimpleBE Mode                         |    |

| 1.2.12: System Control Coprocessor (CP0)        |    |

| 1.2.13: Interrupt Handling                      |    |

| 1.2.14: Modes of Operation                      |    |

| 1.2.15: Floating Point Unit (FPU)               |    |

| 1.2.15.1: FPU Performance                       |    |

| 1.2.16: interAptiv Core Power Management        |    |

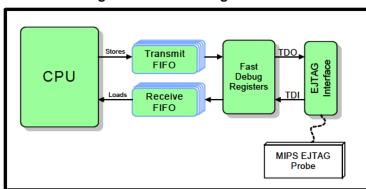

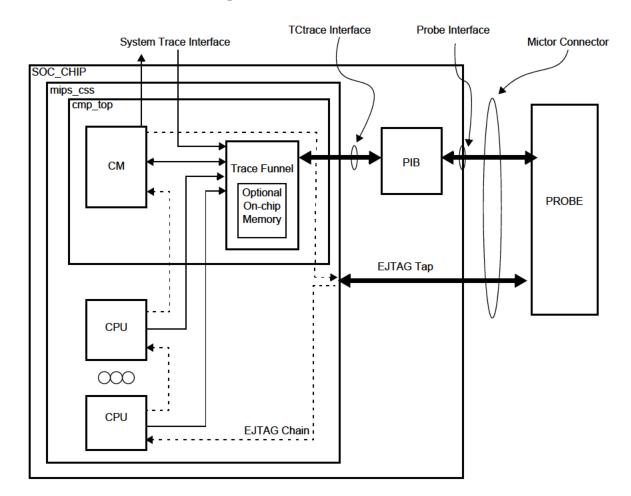

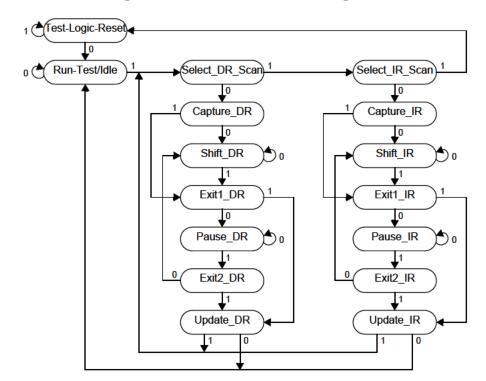

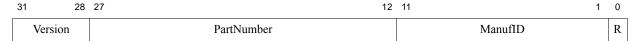

| 1.2.17: EJTAG Debug Support                     |    |

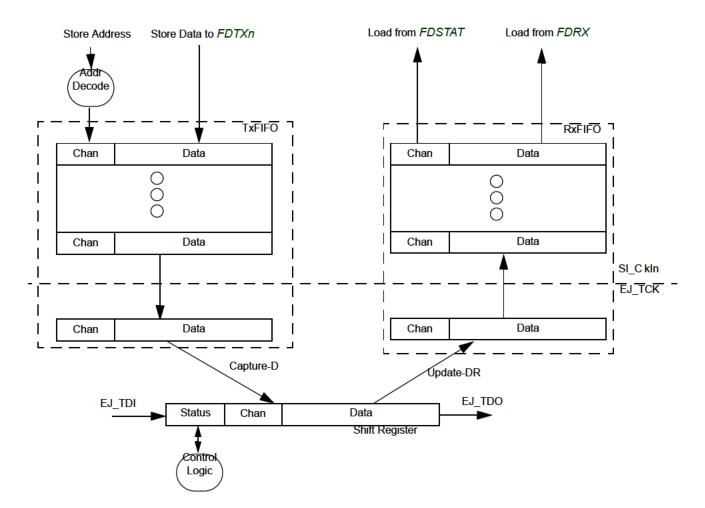

| 1.2.18: Fast Debug Channel                      |    |

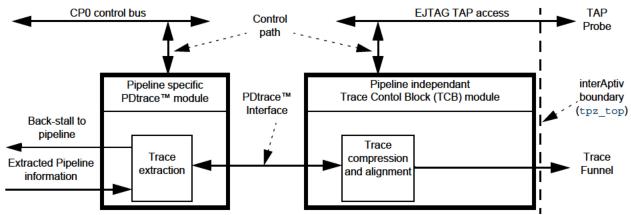

| 1.2.19: PDtrace™                                |    |

| 1.2.20: MIPS16e2 Application Specific Extension |    |

| 1.2.21: CorExtend® Unit                         |    |

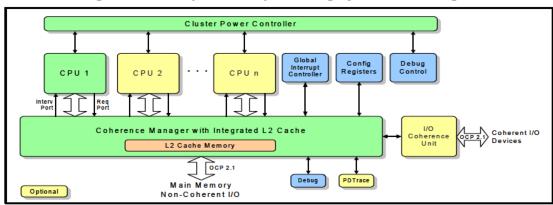

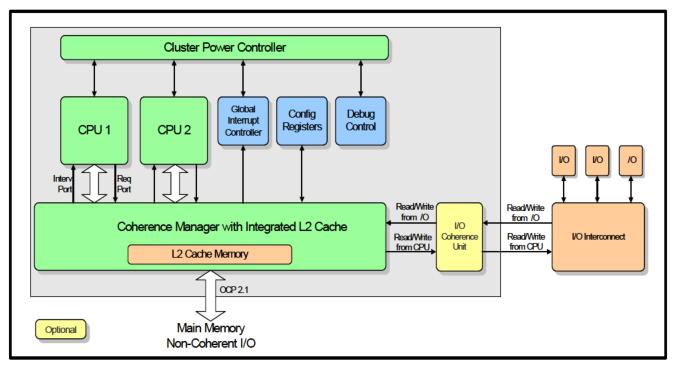

| 1.3: Multiprocessing System                     |    |

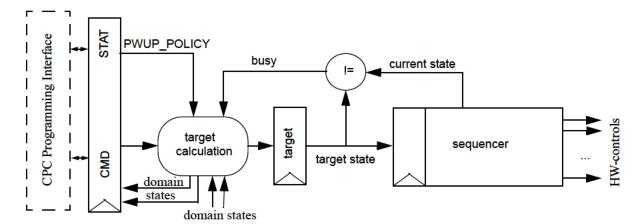

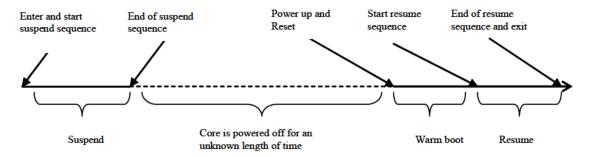

| 1.3.1: Cluster Power Controller (CPC)           | 41 |

| 1.3.1.1: Cluster Power Controller Reset Control |    |

| 1.3.1.2: Optional CPC-basic Power Controller    |    |

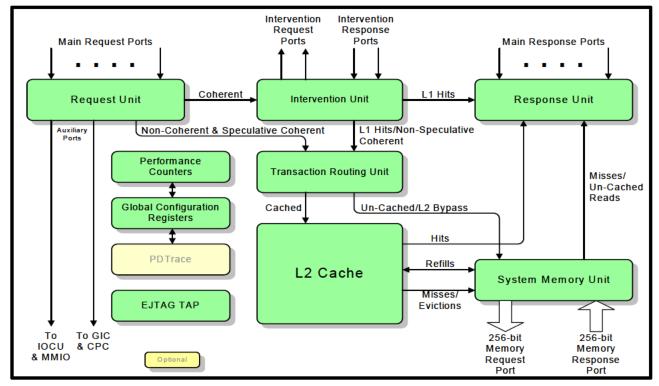

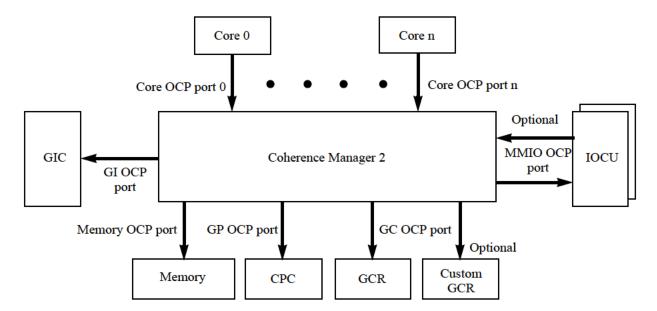

| 1.3.2: Coherence Manager (CM2)                  |    |

| 1.3.2.1: Request Unit (RQU)                     |    |

| 1.3.2.2: Intervention Unit (IVU)                |    |

| 1.3.2.3: System Memory Unit (SMU)               |    |

| 1.3.2.4: Response Unit (RSU)                    |    |

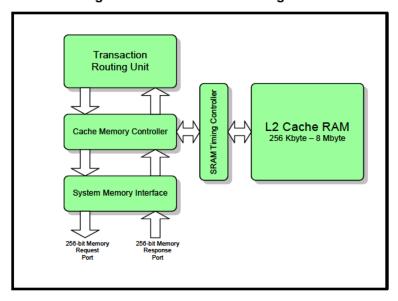

| 1.3.2.5: Transaction Routing Unit               |    |

| 1.3.2.6: Level 2 Cache                          | 44 |

| 1.3.2.7: CM2 Configuration Registers                                      |     |

|---------------------------------------------------------------------------|-----|

| 1.3.2.8: PDTrace Unit                                                     |     |

| 1.3.2.9: Performance Counter Unit                                         |     |

| 1.3.2.10: Coherence Manager Performance                                   |     |

| 1.3.3: I/O Coherence Unit (IOCU)                                          |     |

| 1.3.3.1: Software I/O Coherence                                           |     |

| 1.3.3.2: Hardware I/O Coherence                                           |     |

| 1.3.4: Global Interrupt Controller                                        | 48  |

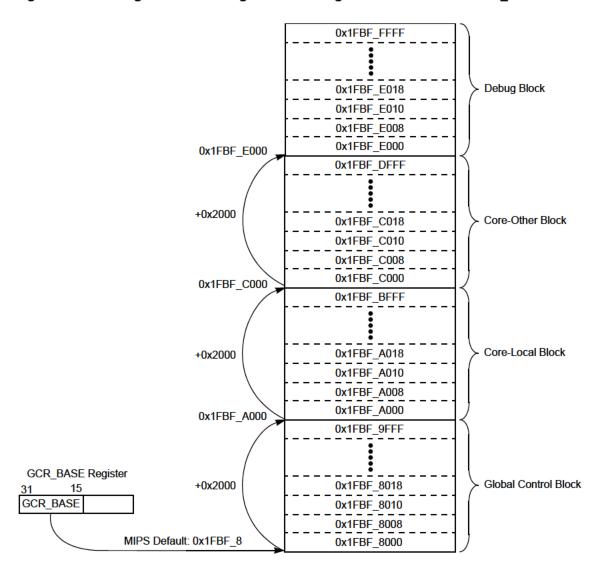

| 1.3.5: Global Configuration Registers (GCR)                               |     |

| 1.3.5.1: Reset Control                                                    |     |

| 1.3.5.2: Inter-CPU Debug Breaks                                           |     |

| 1.3.5.3: CM2 Control Registers                                            |     |

| 1.3.6: Clocking Options                                                   |     |

| 1.3.7: Design For Test (DFT) Features                                     |     |

| 1.3.7.1: Internal Scan                                                    |     |

| 1.3.7.2: Memory BIST                                                      |     |

| 1.4: Build-Time Configuration Options                                     | 51  |

| Chapter 2: CP0 Registers                                                  | 53  |

| 2.1: CP0 Register Summary                                                 | 53  |

| 2.1.1: CP0 Registers Grouped by Function                                  |     |

| 2.1.2: CP0 Registers Grouped by Number                                    | 57  |

| 2.2: CP0 Register Descriptions                                            | 61  |

| 2.2.1: CPU Configuration and Status Registers                             |     |

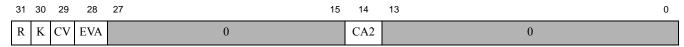

| 2.2.1.1: Device Configuration — Config (CP0 Register 16, Select 0)        |     |

| 2.2.1.2: Device Configuration 1 — Config1 (CP0 Register 16, Select 1)     |     |

| 2.2.1.3: Device Configuration 2 — Config2 (CP0 Register 16, Select 2)     |     |

| 2.2.1.4: Device Configuration 3 — Config3 (CP0 Register 16, Select 3)     |     |

| 2.2.1.5: Device Configuration 4 — Config4 (CP0 Register 16, Select 4)     |     |

| 2.2.1.6: Device Configuration 5 — Config5 (CP0 Register 16, Select 5)     |     |

| 2.2.1.7: Device Configuration 7 — Config7 (CP0 Register 16, Select 7)     |     |

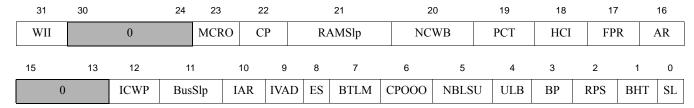

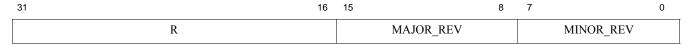

| 2.2.1.8: Processor ID — PRId (CP0 Register 15, Select 0)                  |     |

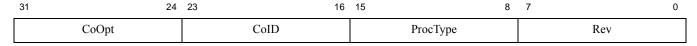

| 2.2.1.9: Exception Base Address — EBase (CP0 Register 15, Select 1)       |     |

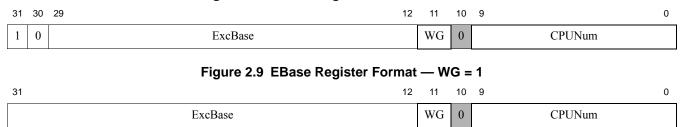

| 2.2.1.10: Status (CP0 Register 12, Select 0)                              |     |

| 2.2.1.11: Interrupt Control — IntCtl (CP0 Register 12, Select 1)          |     |

| 2.2.2: TLB Management Registers                                           |     |

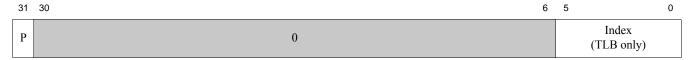

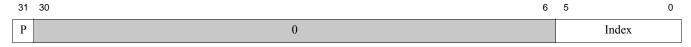

| 2.2.2.1: Index (CP0 Register 0, Select 0)                                 |     |

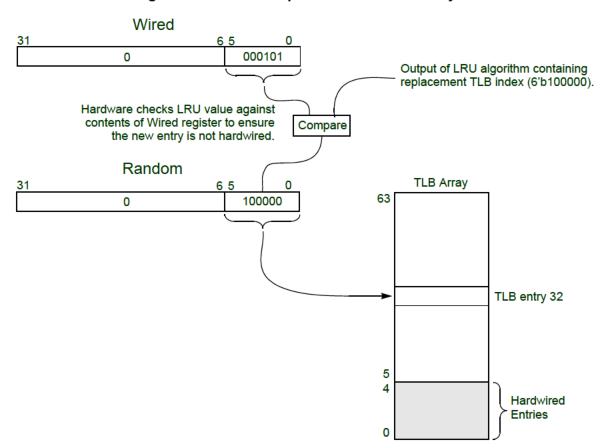

| 2.2.2.2: Random (CP0 Register 1, Select 0)                                | 86  |

| 2.2.2.3: EntryLo0 - EntryLo1 (CP0 Registers 2 and 3, Select 0)            |     |

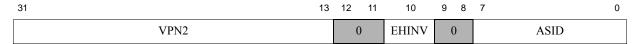

| 2.2.2.4: EntryHi (CP0 Register 10, Select 0)                              |     |

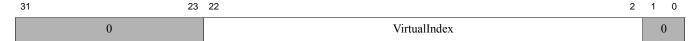

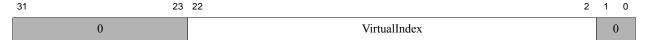

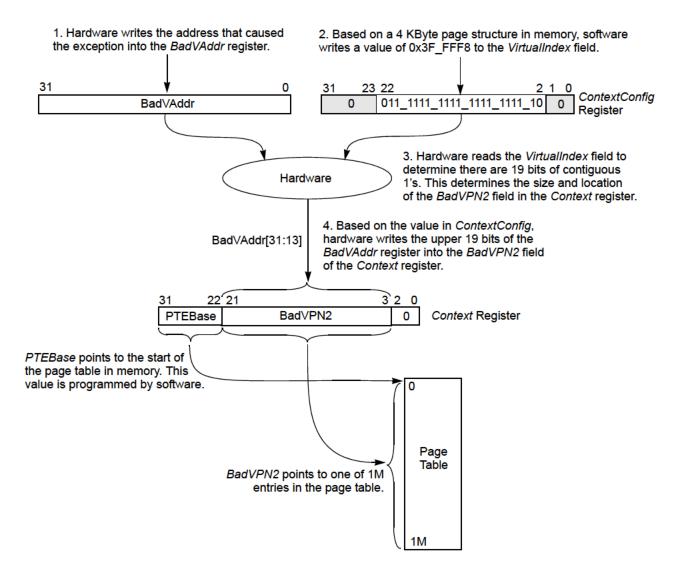

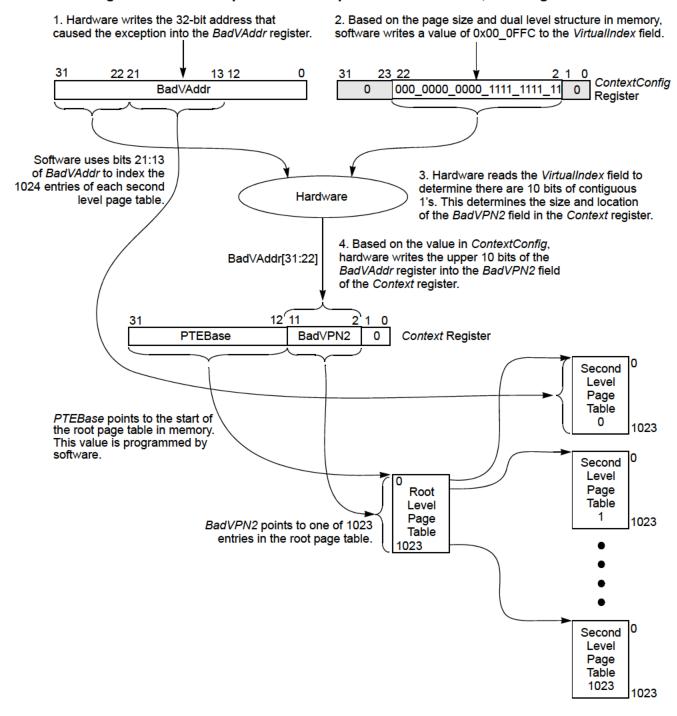

| 2.2.2.5: Context (CP0 Register 4, Select 0)                               |     |

| 2.2.2.6: Context Configuration — ContextConfig (CP0 Register 4, Select 1) |     |

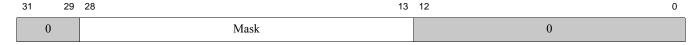

| 2.2.2.7: PageMask (CP0 Register 5, Select 0)                              | 91  |

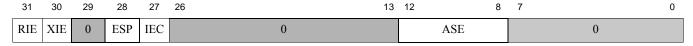

| 2.2.2.8: Page Granularity — PageGrain (CP0 Register 5, Select 1)          | 92  |

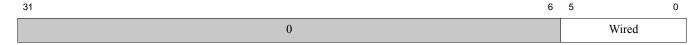

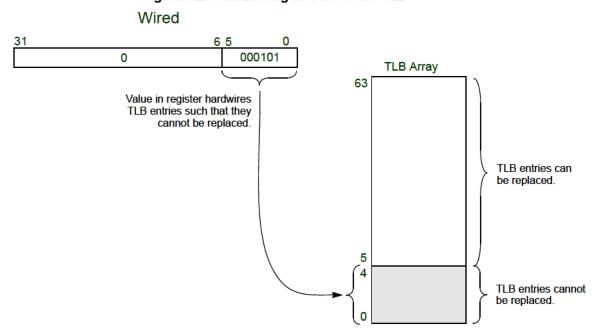

| 2.2.2.9: Wired (CP0 Register 6, Select 0)                                 | 93  |

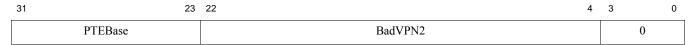

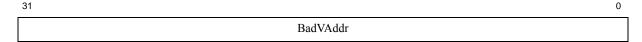

| 2.2.2.10: Bad Virtual Address — BadVAddr (CP0 Register 8, Select 0)       |     |

| 2.2.3: Memory Segmentation Registers                                      |     |

| 2.2.3.1: Segmentation Control 0 — SegCtl0 (CP0 Register 5, Select 2)      |     |

| 2.2.3.2: Segmentation Control 1 — SegCtl1 (CP0 Register 5, Select 3)      |     |

| 2.2.3.3: Segmentation Control 2 — SegCtl2 (CP0 Register 5, Select 4)      |     |

| 2.2.4: Exception Control Registers                                        | 100 |

| 2.2.4.1: Cause (CP0 Register 13, Select 0)                                |     |

| 2.2.4.2: Exception Program Counter — EPC (CP0 Register 14, Select 0)      | 103 |

| 2.2.5.1: Timer Registers   10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.2.4.3: Error Exception Program Counter — ErrorEPC (CP0 Register 30, Select 0)       |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|

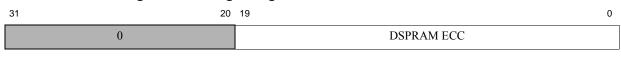

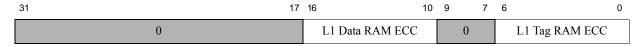

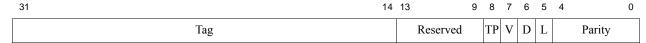

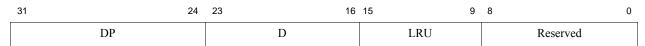

| 2.2.6.2 Compare (CPO Register 11, Select 0) 2.2.6.1 Level 1 Instruction Cache Tag Low — ITagLo (CPO Register 28, Select 0) 2.2.6.2. Level 1 Instruction Cache Data Low — IDataLo (CPO Register 28, Select 1) 1.0 2.2.6.3. Level 1 Instruction Cache Data High — IDataHi (CPO Register 28, Select 1) 2.2.6.4. Level 1 Data Cache Tag Low — DTagLo (CPO Register 28, Select 1) 1.0 2.2.6.5. DTagHi (CPO Register 29, Select 2) 2.2.6.4. Level 1 Data Cache Tag Low — DTagLo (CPO Register 28, Select 2) 1.1 2.2.6.5. DTagHi (CPO Register 29, Select 2) L1 Data Cache and DSPRAM ECC 1.1 2.2.6.6. Level 1 Data Cache Data Low — DDataLo (CPO Register 28, Select 3) 1.1 2.2.6.7. Level 2/3 Cache Tag Low — L23TagLo (CPO Register 28, Select 3) 1.1 2.2.6.8. Level 2/3 Cache Data Low — L23DataLo (CPO Register 28, Select 4) 1.2.2.6.9. Level 2/3 Cache Data Low — L23DataLo (CPO Register 28, Select 4) 1.2.2.6.10. ErrCit (CPO Register 26, Select 0) 1.2.2.6.11. Cache Error — CacheErr (CPO Register 27, Select 0) 1.2.2.7.1. Thead Context and Shadow Control Registers 1.2.2.7.1. TCStatus Register (CPO Register 2, Select 1) 1.2.2.7.1. TCStatus Register (CPO Register 2, Select 3) 1.2.2.7.1. TCRestar Register (CPO Register 12, Select 5) 1.2.2.7.1. SRSColn (POR Register 12, Select 3) 1.2.2.7. TCOschef Back Register (CPO Register 12, Select 5) 1.2.2.7.1. SRSColn (POR Register 12, Select 3) 1.2.2.7. TCSchef Back Register (CPO Register 1, Select 5) 1.2.2.2.1. SRSColn (POR Register (POR Register 1, Select 1) 1.2.2.8.  |                                                                                       |     |

| 2.2.6.1: Level 1 Instruction Cache Tag Low — ITagLo (CPO Register 28, Select 0). 2.2.6.2: Level 1 Instruction Cache Data Low — IDataLo (CPO Register 28, Select 1). 10. 2.2.6.3: Level 1 Instruction Cache Data Low — IDataLo (CPO Register 29, Select 1). 10. 2.2.6.4: Level 1 Data Cache Tag Low — DTagLo (CPO Register 29, Select 1). 11. 2.2.6.5: DTagHi (CPO Register 29, Select 2): L1 Data Cache and DSPRAM ECC. 11. 2.2.6.6: Level 1 Data Cache Tag Low — DTagLo (CPO Register 28, Select 2). 11. 2.2.6.7: Level 2/3 Cache Data Low — DDataLo (CPO Register 28, Select 3). 11. 2.2.6.7: Level 2/3 Cache Data Low — L23TagLo (CPO Register 28, Select 3). 11. 2.2.6.9: Level 2/3 Cache Data Low — L23DataLo (CPO Register 28, Select 4). 11. 2.2.6.9: Level 2/3 Cache Data High — L23DataHi (CPO Register 28, Select 5). 11. 2.2.6.10: ErrCit (CPO Register 26, Select 0). 11. 2.2.6.11: Cache Error — CacheErr (CPO Register 27, Select 0). 11. 2.2.7: Thead Context and Shadow Control Registers. 12. 2.2.7.1: TCStatus Register (CPO Register 2, Select 1). 12. 2.2.7.2: TCBind Register (CPO Register 2, Select 2). 12. 2.2.7.3: TCRestart Register (CPO Register 2, Select 2). 12. 2.2.7.3: TCRestart Register (CPO Register 2, Select 3). 13. 2.2.7.6: TCSchedule Register (CPO Register 2, Select 5). 13. 2.2.7.6: TCSchedule Register (CPO Register 2, Select 5). 13. 2.2.7.6: TCSchedule Register (CPO Register 2, Select 5). 13. 2.2.7.1: SRSConfi (CPO Register 6, Select 1). 2.2.7.1: SRSConfi (CPO Register 1, Select 3). 2.2.7.1: SRSConfi (CPO Register 1, Select 2). 2.2.8.1: VPE Control Register (CPO Register 1, Select 1). 2.2.8.2: VPE Confi Register (CPO Register 1, Select 1). 2.2.8.3: VPE Confi Register (CPO Register 1, Select 1). 2.2.8.3: VPE Confi Register (CPO Register 1, Select 1). 2.2.8.3: VPE | 2.2.5.1: Count (CP0 Register 9, Select 0)                                             | 105 |

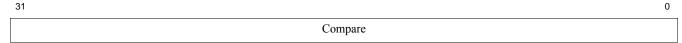

| 2.2.6.1: Level 1 Instruction Cache Tag Low — ITagLo (CPO Register 28, Select 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.2.5.2: Compare (CP0 Register 11, Select 0)                                          | 106 |

| 2.2.6.1: Level 1 Instruction Cache Tag Low — ITagLo (CPO Register 28, Select 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.2.6: Cache Management Registers                                                     | 106 |

| 2.2.6.2: Level 1 Instruction Cache Data Llow — IDataLi (CPO Register 28, Select 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                       |     |

| 2.2.6.3: Level 1 Instruction Cache Data High — IDataH (CPO Register 28, Select 1).  2.2.6.4: Level 1 Data Cache Tag Low — DTagLo (CPO Register 28, Select 2).  111. 2.2.6.5: DTagHi (CPO Register 29, Select 2): L1 Data Cache and DSPRAM ECC.  112. 2.6.6: Level 1 Data Cache Data Low — DDataLo (CPO Register 28, Select 3).  114. 2.2.6.7: Level 2/3 Cache Tag Low — L23TagLo (CPO Register 28, Select 4).  115. 2.2.6.8: Level 2/3 Cache Data Low — L23DataHo (CPO Register 28, Select 5).  116. 2.2.6.9: Level 2/3 Cache Data High — L23DataHi (CPO Register 28, Select 5).  117. 2.2.6.10: ErrCit (CPO Register 26, Select 0).  118. 2.2.6.11: Cache Error — CacheErr (CPO Register 27, Select 0).  119. 2.2.6.11: Cache Error — CacheErr (CPO Register 27, Select 0).  110. 2.2.7.1: TCStatus Register (CPO Register 2, Select 2).  111. 2.2.7.1: TCStatus Register (CPO Register 2, Select 2).  112. 2.2.7.2: TCBind Register (CPO Register 2, Select 2).  112. 2.2.7.3: TCGestar Register (CPO Register 2, Select 3).  113. 2.2.7.4: TCHalt Register (CPO Register 2, Select 3).  114. 2.2.7.5: TCContext Register (CPO Register 2, Select 4).  115. 2.2.7.5: TCContext Register (CPO Register 2, Select 5).  117. 2.2.7.7: TCSchedule Register (CPO Register 2, Select 5).  118. 2.2.7.8: TCOpt Register (CPO Register 2, Select 7).  119. 2.2.7.9: SRSConf0 (CPO Register 6, Select 7).  119. 2.2.7.10: SRSConf1-4 (CPO Register 6, Select 7).  120. 2.2.7.10: SRSConf1-4 (CPO Register 6, Select 7).  121. 2.2.7.11: TSSCUR Register (CPO Register 12, Select 3).  122. 2.7.11: TSSCUR Register (CPO Register 12, Select 3).  122. 2.7.12: SRSMap Register (CPO Register 12, Select 3).  122. 2.7.12: SRSMap Register (CPO Register 1, Select 2).  122. 2.8: VIPE Control Register (CPO Register 1, Select 3).  122. 2.8: VPE Conf1 Register (CPO Register 1, Select 3).  122. 2.8: VPE Conf1 Register (CPO Register 1, Select 3).  122. 2.8: VPE Conf1 Register (CPO Register 1, Select 3).  122. 2.8: VPE Conf1 Register (CPO Register 1, Select 3).  122. 2.8: VPE Control Register (CPO Register 1, Select 3). |                                                                                       |     |

| 2 2.6.4: Level 1 Data Cache Tag Low — DTagLo (CPO Register 28, Select 2).  111 2.2.6.6: Level 1 Data Cache Data Low — DDataLo (CPO Register 28, Select 3).  112.2.6.7: Level 2/3 Cache Tag Low — L23TagLo (CPO Register 28, Select 3).  114.2.6.8: Level 2/3 Cache Data Low — DDataLo (CPO Register 28, Select 4).  115.2.6.9: Level 2/3 Cache Data Low — L23DataLo (CPO Register 28, Select 5).  111 2.2.6.9: Level 2/3 Cache Data High — L23DataLo (CPO Register 28, Select 5).  111 2.2.6.10: ErrCil (CPO Register 26, Select 0).  112.2.6.11: Cache Error — CacheErr (CPO Register 27, Select 0).  112.2.6.11: Cache Error — CacheErr (CPO Register 28, Select 1).  112.2.7: Thead Context and Shadow Control Registers.  112 2.2.7.1: TCStaltus Register (CPO Register 2, Select 1).  112.2.7: TCBind Register (CPO Register 2, Select 1).  112.2.7.3: TCRestart Register (CPO Register 2, Select 3).  113.2.7.4: TCHalt Register (CPO Register 2, Select 3).  113.2.7.5: TCContext Register (CPO Register 2, Select 4).  113.2.7.6: TCSchefback Register (CPO Register 2, Select 5).  113.2.7.7: TCSchefback Register (CPO Register 2, Select 6).  113.2.7.7: TCSchefback Register (CPO Register 2, Select 7).  113.2.7.7: SRSConfl 4 (CPO Register 3, Select 7).  113.2.7.7: SRSConfl 4 (CPO Register 6, Select 1).  114.2.7.7: SRSConfl 4 (CPO Register 6, Select 1).  115.2.7.7: SRSConfl 4 (CPO Register 6, Select 1).  116.2.7.7: SRSConfl 4 (CPO Register 12, Select 3).  117.2.7.7: SRSConfl 4 (CPO Register 12, Select 2).  118.2.7.7: SRSConfl 4 (CPO Register 12, Select 2).  119.2.7.7: SRSConfl 4 (CPO Register 12, Select 2).  120.7.7: SRSConfl 4 (CPO Register 14, Select 2).  121.3: 2.2.7: SRSMap Register (CPO Register 12, Select 3).  122.8: Virtual Processing Element (VPE) Register 15.  122.8: Virtual Processing Element (VPE) Register 14, Select 3).  122.8: Virtual Processing Element (VPE) Register 15.  122.8: Virtual Processing Element (VPE) Register 15.  122.8: Virtual Processing Element (VPE) Register 17, Select 10.  122.8: Virtual Processing Element (VPE) Register 17, Selec |                                                                                       |     |

| 2 2.6.5: DTaghl (CPO Register 29, Select 2): £1 Data Cache and DSPRAM ECC. 11: 22.6.6: Level 1 Data Cache Data Low — DDataLo (CPO Register 28, Select 3). 11: 22.6.7: Level 2/3 Cache Data Low — L23TagLo (CPO Register 28, Select 4). 11: 22.6.8: Level 2/3 Cache Data Low — L23TagLo (CPO Register 28, Select 5). 11: 22.6.9: Level 2/3 Cache Data High — L23DataHi (CPO Register 28, Select 5). 11: 22.6.10: ErrCit (CPO Register 26, Select 0). 11: 22.6.11: Cache Error — CacheErr (CPO Register 27, Select 0). 11: 22.6.11: Cache Error — CacheErr (CPO Register 27, Select 0). 11: 22.7: Thead Context and Shadow Control Registers. 12: 22.7: TroStatus Register (CPO Register 2, Select 1). 12: 27.7: TCStatus Register (CPO Register 2, Select 1). 12: 27.7: TCStatus Register (CPO Register 2, Select 3). 13: 22.7.4: TCHalt Register (CPO Register 2, Select 3). 13: 22.7.5: TCContext Register (CPO Register 2, Select 4). 13: 22.7.5: TCContext Register (CPO Register 2, Select 5). 13: 22.7.6: TCSchedule Register (CPO Register 2, Select 5). 13: 22.7.6: TCSchedule Register (CPO Register 2, Select 7). 13: 22.7.7: TCScheFBack Register (CPO Register 2, Select 7). 13: 22.7.8: TCOpt Register (CPO Register 1, Select 1). 13: 22.7.10: SRSConfl 4 (CPO Register 6, Select 1). 13: 22.7.10: SRSConfl 4 (CPO Register 12, Select 3). 13: 22.7.11: SRSCI Register (CPO Register 12, Select 3). 13: 22.7.11: SRSCI Register (CPO Register 12, Select 3). 13: 22.7.12: SRSMap Register (CPO Register 1, Select 2). 13: 22.7.12: SRSMap Register (CPO Register 1, Select 1). 13: 22.8.1: VPE Control Register (CPO Register 1, Select 1). 13: 22.8.2: VPE Confl Register (CPO Register 1, Select 1). 13: 22.8.2: VPE Confl Register (CPO Register 1, Select 1). 14: 22.8.3: WPE Control Register (CPO Register 1, Select 3). 14: 22.8.4: WPE ScheEBack Register (CPO Register 1, Select 5). 14: 22.8.5: WPE ScheEBack Register (CPO Register 1, Select 5). 14: 22.8.5: WPE ScheEBack Register (CPO Register 1, Select 5). 14: 22.8.6: WPE Opt Register (CPO Register 1, Select 3). 14: 22.9: Performance Counte |                                                                                       |     |

| 2.2.6.6: Level 2/3 Cache Data Low — DDataLo (CPO Register 28, Select 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                       |     |

| 2 2.6.7: Level 2/3 Cache Tag Low — L23TagLo (CP0 Register 28, Select 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                       |     |

| 2.2.6.8: Level 2/3 Cache Data Low — L23DataLo (CPO Register 28, Select 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                       |     |

| 22.6.9: Level 2/3 Cache Data High — L23DataHi (CP0 Register 29, Select 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                       |     |

| 2.2.6.10: ErrCtl (CPO Register 26, Select 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                       |     |

| 2.2.6.11: Cache Error — CacheErr (CP0 Register 27, Select 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                       |     |

| 2.2.7.1 Thead Context and Shadow Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.2.6.11: Cacho Error — Cacho Err (CD0 Pagister 27, Solaet 0)                         | 110 |

| 2.2.7.1: TCStatus Register (CP0 Register 2, Select 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                       |     |

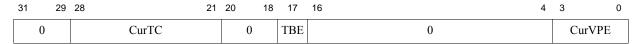

| 2.2.7.2: TCBind Register (CP0 Register 2, Select 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                       |     |

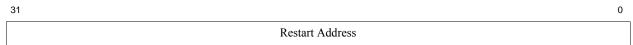

| 2.2.7.3: TCRestart Register (CP0 Register 2, Select 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |     |

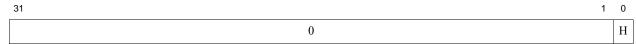

| 2.2.7.4: TCHalt Register (CP0 Register 2, Select 4) 2.2.7.5: TCContext Register (CP0 Register 2, Select 5) 13 2.2.7.6: TCSchedule Register (CP0 Register 2, Select 6) 13. 2.2.7.7: TCScheFBack Register (CP0 Register 2, Select 7) 13. 2.2.7.8: TCOpt Register (CP0 Register 2, Select 7) 13. 2.2.7.9: SRSConf0 (CP0 Register 6, Select 7) 13. 2.2.7.10: SRSConf1 (CP0 Register 6, Select 1) 2.2.7.11: SRSConf1-4 (CP0 Register 6, Select 2-5) 13. 2.2.7.12: SRSMap Register (CP0 Register 12, Select 2) 13. 2.2.7.12: SRSMap Register (CP0 Register 12, Select 3) 13. 2.2.8: Virtual Processing Element (VPE) Register 1, Select 3) 13. 2.2.8: VPE Conf1 Register (CP0 Register 1, Select 1) 13. 2.2.8: VPE Conf1 Register (CP0 Register 1, Select 2) 13. 2.2.8: VPE Conf1 Register (CP0 Register 1, Select 2) 13. 2.2.8: VPE Schedule Register (CP0 Register 1, Select 5) 14. 2.2.8: VPE Schedule Register (CP0 Register 1, Select 5) 14. 2.2.8: VPE Schedule Register (CP0 Register 1, Select 5) 14. 2.2.8: VPE Opt Register (CP0 Register 1, Select 7) 14. 2.2.8: WPE Opt Register (CP0 Register 1, Select 7) 14. 2.2.8: MVPControl Register (CP0 Register 0, Select 1) 14. 2.2.8: MVPControl Register (CP0 Register 0, Select 1) 14. 2.2.8: MVPControl Register (CP0 Register 0, Select 1) 14. 2.2.9: Performance Monitoring Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                       |     |

| 2.2.7.5: TCContext Register (CP0 Register 2, Select 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |     |

| 2.2.7.6: TCSchedule Register (CP0 Register 2, Select 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                       |     |

| 2.2.7.7: TCScheFBack Register (CP0 Register 2, Select 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |     |

| 2.2.7.8: TCOpt Register (CP0 Register 3, Select 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                       |     |

| 2.2.7.9: SRSConf0 (CP0 Register 6, Select 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                       |     |

| 2.2.7.10: SRSConf1-4 (CP0 Register 6, Select 2-5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                       |     |

| 2.2.7.11: SRSCtl Register (CP0 Register 12, Select 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                       |     |

| 2.2.7.12: SRSMap Register (CP0 Register 12, Select 3)       13         2.2.8: Virtual Processing Element (VPE) Registers       13         2.2.8.1: VPE Control Register (CP0 Register 1, Select 1)       13         2.2.8.2: VPE Conf0 Register (CP0 Register 1, Select 2)       13         2.2.8.3: VPE Conf1 Register (CP0 Register 1, Select 3)       14         2.2.8.4: VPE Schedule Register (CP0 Register 1, Select 5)       14         2.2.8.5: VPE ScheFBack Register (CP0 Register 1, Select 6)       14         2.2.8.6: VPE Opt Register (CP0 Register 0, Select 7)       14         2.2.8.7: MVPControl Register (CP0 Register 0, Select 1)       14         2.2.8.8: MVPConf1 Register (CP0 Register 0, Select 2)       14         2.2.8.9: MVPConf1 Register (CP0 Register 0, Select 3)       14         2.2.9.1: Performance Monitoring Registers.       14         2.2.9.1: Performance Counter 0 and 1 Control Registers (CP0 Register 25, select 0, 2)       14         2.2.9.1: Performance Counter 0 and 1 Count Registers (CP0 Register 25, select 1, 3)       15         2.2.10.1: Debug Registers       15         2.2.10.2: Debug Exception Program Counter — DEPC (CP0 Register 24, Select 0)       16         2.2.10.3: Debug Save — DESAVE (CP0 Register 31, Select 0)       16         2.2.10.5: Watch High 0 - 3 — WatchHo-3 (CP0 Register 18, Select 0-3)       16         2.2.11: PDTrace Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                       |     |

| 2.2.8: Virtual Processing Element (VPE) Registers       13         2.2.8.1: VPE Control Register (CP0 Register 1, Select 1)       13         2.2.8.2: VPE Conf0 Register (CP0 Register 1, Select 2)       13         2.2.8.3: VPE Conf1 Register (CP0 Register 1, Select 3)       14         2.2.8.4: VPE Schedule Register (CP0 Register 1, Select 5)       14         2.2.8.5: VPE ScheFBack Register (CP0 Register 1, Select 6)       14         2.2.8.6: VPE Opt Register (CP0 Register 0, Select 7)       14         2.2.8.7: MVPControl Register (CP0 Register 0, Select 1)       14         2.2.8.8: MVPConf0 Register (CP0 Register 0, Select 2)       14         2.2.8.9: MVPConf1 Register (CP0 Register 0, Select 3)       14         2.2.9.1: Performance Monitoring Registers       14         2.2.9.2: Performance Counter 0 and 1 Control Registers (CP0 Register 25, select 0, 2)       14         2.2.9.1: Performance Counter 0 and 1 Count Registers (CP0 Register 25, select 1, 3)       15         2.2.10.1: Debug Registers       15         2.2.10.2: Debug Exception Program Counter — DEPC (CP0 Register 24, Select 0)       16         2.2.10.3: Debug Save — DESAVE (CP0 Register 31, Select 0)       16         2.2.10.4: Watch Low 0 - 3 — WatchLo0-3 (CP0 Register 18, Select 0-3)       16         2.2.11: PDTrace Registers       16         2.2.11.1: Trace Control Register — TraceControl (CP0 Registe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                       |     |

| 2.2.8.1: VPE Control Register (CP0 Register 1, Select 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |     |

| 2.2.8.2: VPE Conf0 Register (CP0 Register 1, Select 2)       133         2.2.8.3: VPE Conf1 Register (CP0 Register 1, Select 3)       144         2.2.8.4: VPE Schedule Register (CP0 Register 1, Select 5)       14         2.2.8.5: VPE ScheFBack Register (CP0 Register 1, Select 6)       142         2.2.8.6: VPE Opt Register (CP0 Register 1, Select 7)       143         2.2.8.7: MVPControl Register (CP0 Register 0, Select 1)       144         2.2.8.8: MVPConf1 Register (CP0 Register 0, Select 2)       144         2.2.8.9: MVPConf1 Register (CP0 Register 0, Select 3)       144         2.2.9: Performance Monitoring Registers       144         2.2.9.1: Performance Counter 0 and 1 Control Registers (CP0 Register 25, select 0, 2)       144         2.2.9.2: Performance Counter 0 and 1 Count Registers (CP0 Register 25, select 1, 3)       150         2.2.10: Debug Registers       15         2.2.10: Debug Exception Program Counter — DEPC (CP0 Register 24, Select 1)       16         2.2.10.2: Debug Exception Program Counter — DEPC (CP0 Register 24, Select 0)       16         2.2.10.4: Watch Low 0 - 3 — WatchLo0-3 (CP0 Register 18, Select 0-3)       16         2.2.10.5: Watch High 0 - 3 — WatchHi0-3 (CP0 Register 19, Select 0-3)       16         2.2.11: PDTrace Registers       16         2.2.11: Trace Control Register — TraceControl (CP0 Register 23, Select 1)       16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                       |     |

| 2.2.8.3: VPE Conf1 Register (CP0 Register 1, Select 3)       14         2.2.8.4: VPE Schedule Register (CP0 Register 1, Select 5)       14         2.2.8.5: VPE ScheFBack Register (CP0 Register 1, Select 6)       14         2.2.8.6: VPE Opt Register (CP0 Register 1, Select 7)       14         2.2.8.7: MVPControl Register (CP0 Register 0, Select 1)       14         2.2.8.8: MVPConf0 Register (CP0 Register 0, Select 2)       14         2.2.8.9: MVPConf1 Register (CP0 Register 0, Select 3)       14         2.2.9: Performance Monitoring Registers       14         2.2.9.1: Performance Counter 0 and 1 Control Registers (CP0 Register 25, select 0, 2)       14         2.2.9.2: Performance Counter 0 and 1 Count Registers (CP0 Register 25, select 1, 3)       15         2.2.10: Debug Registers       15         2.2.10: Debug (CP0 Register 23, Select 0)       15         2.2.10.2: Debug Exception Program Counter — DEPC (CP0 Register 24, Select 0)       16         2.2.10.3: Debug Save — DESAVE (CP0 Register 31, Select 0)       16         2.2.10.4: Watch Low 0 - 3 — WatchLo0-3 (CP0 Register 18, Select 0-3)       16         2.2.10.5: Watch High 0 - 3 — WatchHi0-3 (CP0 Register 19, Select 0-3)       16         2.2.11: PDTrace Registers       16         2.2.11: Trace Control Register — TraceControl (CP0 Register 23, Select 1)       16         2.2.11.2: Trace Control 2 Register — Tra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                       |     |