# MIPS64® I6500 Multiprocessing System Programmer's Guide

<u>Public</u>. This publication contains proprietary information which is subject to change without notice and is supplied 'as is', without any warranty of any kind.

Document Number: MD01179

| Chapter 1: Architecture Overview                       | 9  |

|--------------------------------------------------------|----|

| 1.1: Product Overview                                  | 11 |

| 1.1.1: Single-Cluster Configuration                    | 11 |

| 1.1.2: Multi-Cluster Configuration                     |    |

| 1.2: I6500 Features                                    |    |

| 1.2.1: MIPS64® Release 6 Architecture                  |    |

| 1.2.2: MIPS® SIMD Architecture                         |    |

| 1.2.3: MIPS® Virtualization                            |    |

| 1.2.4: System-level Features                           |    |

| 1.2.5: Core-level Features                             |    |

| 1.3: I6500 Core Block Diagram                          |    |

| 1.4: CP0 Register to Assembler Mapping                 |    |

| 1.5: MIPS Software Tools                               |    |

| 1.5.1: MIPS Linux                                      |    |

| 1.5.2: MIPS Android                                    |    |

| 1.5.3: Codescape MIPS SDK                              |    |

| 1.5.4: Codescape Debugger                              |    |

| 1.5.5: Compilers                                       |    |

| 1.5.6: Boot Loader                                     |    |

| 1.5.7: MIPS RTOS and IoT Support                       |    |

| 1.5.8: Developer Resources                             | 19 |

|                                                        |    |

| Chapter 2: Memory Management Unit                      |    |

| 2.1: Overview                                          |    |

| 2.1.1: TLB Types                                       |    |

| 2.1.2: TLB Instructions                                |    |

| 2.1.3: Shared FTLB Translations                        |    |

| 2.1.4: Global TLB Invalidate                           |    |

| 2.2: MMU Programming                                   |    |

| 2.2.1: Assembly Language Conventions                   |    |

| 2.2.2: Determining the VTLB Size                       |    |

| 2.2.3: FTLB Page Size Configuration                    |    |

| 2.2.4: VTLB and FTLB Initialization                    |    |

| 2.2.5: Indexing the VTLB and FTLB                      |    |

| 2.2.6: Programming a TLB Entry                         |    |

| 2.2.7: Hardwiring VTLB Entries                         |    |

| 2.2.8: FTLB Hashing Scheme and the TLBWI Instruction   |    |

| 2.3: TLB Exception Handler                             |    |

| 2.4: Additional Information                            |    |

|                                                        |    |

| Chapter 3: Caches                                      |    |

| 3.1: Cache Subsystem Overview                          |    |

| 3.1.1: L1 Instruction Cache                            |    |

| 3.1.2: L1 Data Cache                                   |    |

| 3.1.3: L2 Cache                                        |    |

| 3.1.4: Cache Instructions                              |    |

| 3.2: Cache Coherency                                   |    |

| 3.3: Self-modified Code                                |    |

| 3.4: Register Interface                                |    |

| 3.4.1: L1 Instruction Cache Control Registers          |    |

| 3.4.1.1: Config Register (CP0 register 16, Select 0)   |    |

| 3.4.1.2: Config1 Register (CP0 register 16, Select 1)  |    |

| 3.4.1.3: CacheErr Register (CP0 register 27, Select 0) |    |

MIPS64® I6500 Multiprocessing System Programmer's Guide, Revision 1.00

| 3.4.1.4: L1 Instruction Cache TagLo Register (CP0 register 28, Select 0)                                           | 43 |

|--------------------------------------------------------------------------------------------------------------------|----|

| 3.4.1.5: L1 Instruction Cache DataLo Register (CP0 register 28, Select 1)                                          | 43 |

| 3.4.1.6: L1 Instruction Cache DataHi Register (CP0 register 29, Select 1)                                          | 43 |

| 3.4.2: L1 Data Cache Control Registers                                                                             |    |

| 3.4.2.1: Config Register (CP0 register 16, Select 0)                                                               |    |

| 3.4.2.2: Config1 Register (CP0 register 16, Select 1)                                                              |    |

| 3.4.2.3: CacheErr Register (CP0 register 27, Select 0)                                                             |    |

| 3.4.2.4: L1 Data Cache TagLo Register (CP0 register 28, Select 2)                                                  |    |

| 3.4.2.5: L1 Data Cache DataLo Register (CP0 register 28, Select 3)                                                 |    |

| 3.4.2.6: L1 Data Cache DataHi Register (CP0 register 29, Select 3)                                                 |    |

| 3.4.3: L2 Cache CM GCR Control Registers                                                                           |    |

| 3.4.3.1: GCR_ERR_CONTROL (Offset 0x0038)                                                                           |    |

| 3.4.3.2: L2_Config Register (Offset 0x0130)                                                                        | 45 |

| 3.4.3.3: L2_RAM_Config Register (Offset 0x0240)                                                                    |    |

| 3.4.3.4: L2_PFT_Control Register (Offset 0x0300)                                                                   |    |

| 3.4.3.5: L2_PFT_Control_B Register (Offset 0x0308)                                                                 |    |

| 3.4.3.6: L2_TAG_ADDR Register (Offset 0x0600)                                                                      |    |

| 3.4.3.7: L2_TAG_STATE Register (Offset 0x0608)                                                                     |    |

| 3.4.3.8: L2_DATA Register (Offset 0x0610)                                                                          |    |

| 3.4.3.9: L2_DATA_ECC Register (Offset 0x0618)                                                                      |    |

| 3.4.3.10: L2SM_COP Register (Offset 0x0620)                                                                        |    |

| 3.4.3.11: L2SM_TAG_ADDR_COP Register (Offset 0x0628)                                                               |    |

| 3.4.3.12: CPC_CL_STAT_CONF Register (Offset 0x0008)                                                                |    |

| 3.5: L2 Cache Initialization Options                                                                               |    |

| 3.5.1: Automatic Hardware Cache Initialization                                                                     |    |

| 3.5.2: Manual Hardware Cache Initialization.                                                                       |    |

| 3.5.3: Software Cache Initialization                                                                               |    |

| 3.6: L2 Cache Flush, Burst, and Abort                                                                              |    |

| 3.6.1: L2 Cache Flush                                                                                              |    |

| 3.6.2: L2 Cache Burst Operations.                                                                                  |    |

| 3.6.3: Abort Operations                                                                                            |    |

| 3.7: Cache Initialization Routines<br>3.7.1: Initializing the Instruction Cache                                    |    |

|                                                                                                                    |    |

| 3.7.1.1: L1 Instruction Cache Invalidation Using the GINVI Instruction<br>3.7.1.2: L1 Cache Initialization Routine |    |

| 3.7.2: Initializing the Data Cache                                                                                 |    |

| 3.7.3: Initializing the Level 2 Cache                                                                              |    |

| 3.8: Flushing the L1 Data Cache                                                                                    |    |

| 3.9: Setting the KSEG0 Memory Space Cache Coherency                                                                |    |

|                                                                                                                    |    |

| Chapter 4: Exceptions                                                                                              | 59 |

| 4.1: Overview of Exception Processing                                                                              |    |

| 4.1.1: Exception Types                                                                                             |    |

| 4.1.2: Detecting an Exception                                                                                      |    |

| 4.1.3: Exception Conditions                                                                                        |    |

| 4.2: Defining the Exception Vector Locations                                                                       |    |

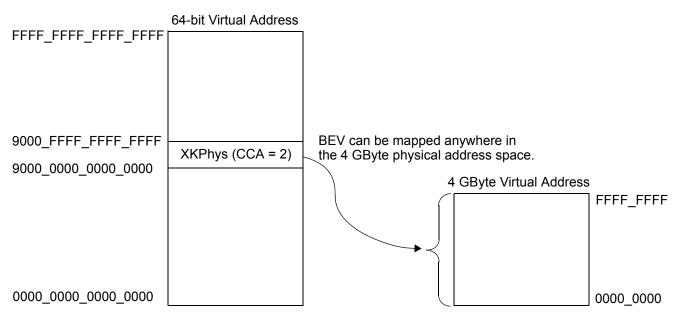

| 4.2.1: Mapping the BEV to the Lower 512 MBytes of the Physical Address                                             |    |

| 4.2.2: Mapping the BEV to the Lower 4 GBytes of the Physical Address                                               |    |

| 4.2.3: Mapping the Reset Vector to the Lower 512 MBytes of the Physical Address                                    |    |

| 4.2.4: Mapping the Reset Vector to the Lower 4 GBytes of the Physical Address                                      |    |

| 4.2.5: Selecting Between the BEV and Reset Exception Vectors                                                       |    |

| 4.2.6: Exception Vector Base Address per Exception Type                                                            |    |

| 4.3: Core-Level Exception Priorities                                                                               |    |

|                                                                                                                    |    |

| 4.4: Hypervisor Exception Priorities                                                        | 71 |

|---------------------------------------------------------------------------------------------|----|

| 4.5: General Exception Processing                                                           | 72 |

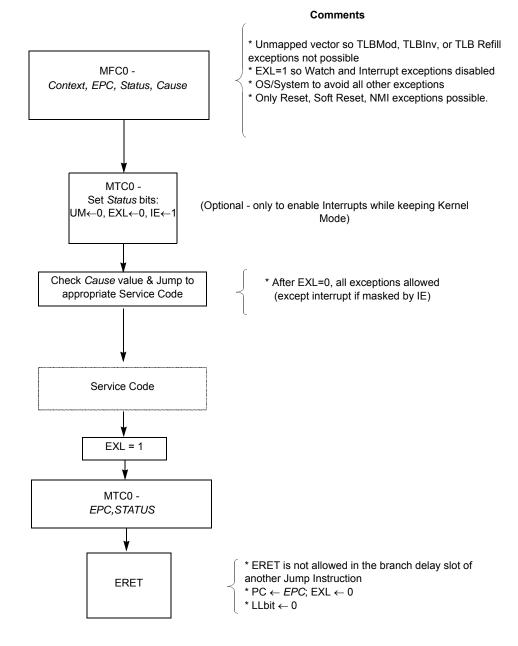

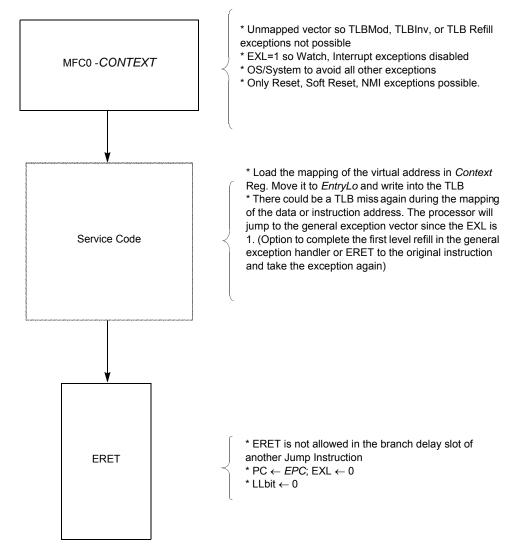

| 4.6: Exception Handling and Servicing Flowcharts                                            | 73 |

| 4.7: Interrupt Mode Code Examples                                                           |    |

| 4.7.1: Interrupt Compatibility Mode                                                         |    |

| 4.7.2: Vectored Interrupt Mode                                                              |    |

| 4.7.3: External Interrupt Controller Mode                                                   |    |

| Chapter 5: Coherence Manager                                                                |    |

| 5.1: CM Overview                                                                            |    |

| 5.1.1: CM Interface — Register Ring Bus and Device ID's                                     |    |

| 5.1.2: CM GCR Register Map                                                                  |    |

| 5.1.3: Core-Local GCRs                                                                      |    |

| 5.1.4: Core-Other GCRs                                                                      |    |

| 5.1.5: Core-Local and Core-Other Register Usage                                             |    |

| 5.1.6: Cluster to Cluster Accesses                                                          |    |

| 5.2: Verifying Overall System Configuration                                                 |    |

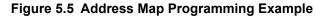

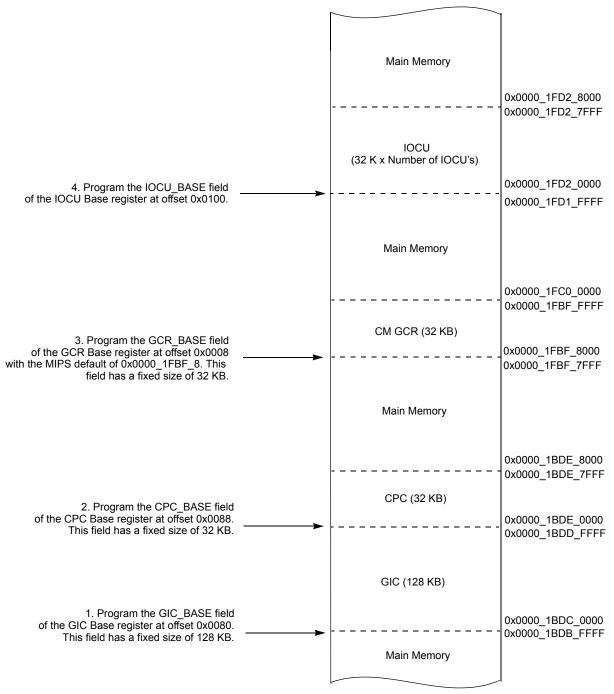

| 5.3: Programming the Base Addresses in Memory                                               |    |

| 5.4: CM Register Access Permissions                                                         |    |

| 5.5: CM Programming Examples                                                                |    |

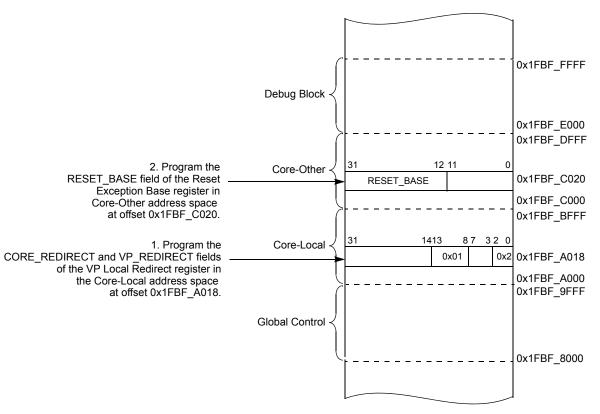

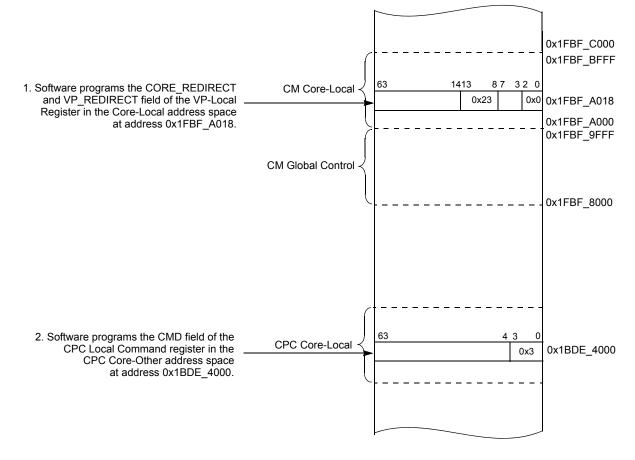

| 5.5.1: Programming Another Virtual Processor (VP) in the Same Core                          |    |

| 5.5.2: Programming Local GCR's Corresponding to Another Core                                |    |

| 5.5.3: Accessing the CPC Local Registers via the CM                                         |    |

| 5.5.4: Powering Up the Debug Unit (DBU) via the CM                                          |    |

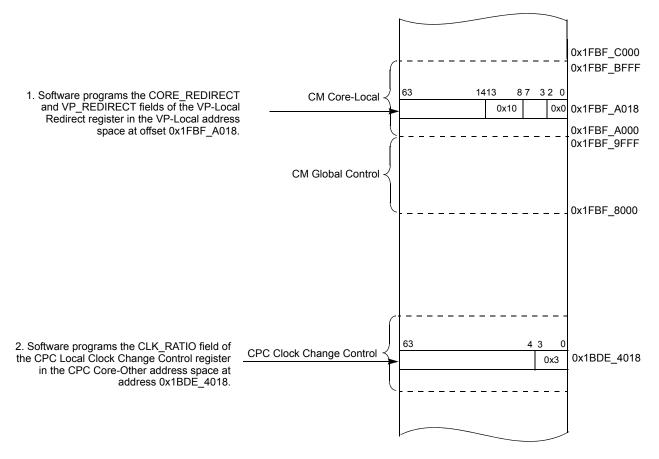

| 5.5.5: Setting the Clock Ratios Between the I6500 System Components                         |    |

| 5.5.6: Cluster to Cluster Access                                                            |    |

| 5.5.7: Accessing the Core-Local and Core-Other Registers in the Global Interrupt Controller |    |

| 5.6: Coherency Enable                                                                       |    |

| 5.7: L2 Cache Prefetch                                                                      |    |

| 5.7.1: Prefetch Enable                                                                      |    |

| 5.7.2: Select Ports for L2 Prefetching                                                      |    |

| 5.7.3: Enabling Code Prefetch                                                               |    |

| 5.8: CM Uncached Semaphore Management                                                       |    |

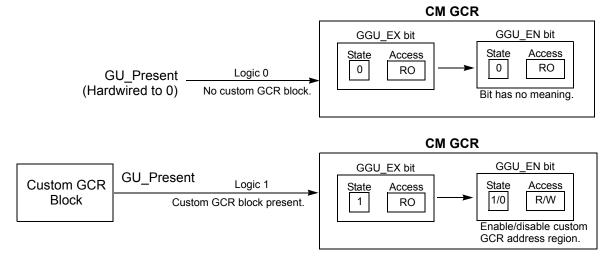

| 5.9: Custom GCR Implementation                                                              |    |

| 5.10: Error Processing                                                                      |    |

| 5.11: IOCU Interface                                                                        |    |

| 5.12: MMIO Address Regions                                                                  |    |

| 5.12.1: CM GPR Register Interface                                                           |    |

| 5.12.2: MMIO Region Control                                                                 |    |

| 5.13: Auxiliary Interfaces                                                                  |    |

| Chapter 6: Power Management                                                                 |    |

| 6.1: Overview                                                                               |    |

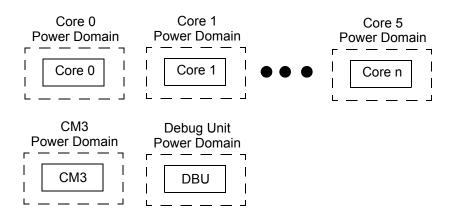

| 6.1.1: Power Domains                                                                        |    |

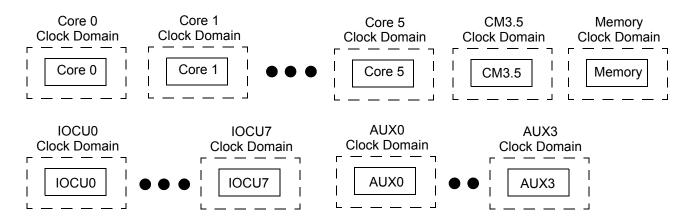

| 6.1.2: Clock Domains                                                                        |    |

| 6.1.3: Core and IOCU Selection.                                                             |    |

| 6.1.4: Overview of Power States                                                             |    |

| 6.2: CPC Register Programming                                                               |    |

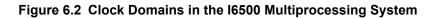

| 6.2.1: Cluster Power Controller Register Address Map                                        |    |

| 6.2.2: CPC Base Address                                                                     |    |

| 6.2.3: Global Control Block Register Map                                                    |    |

| 6.2.4: Local and Core-Other Control Blocks                                                  |    |

| 6.2.5: Requestor Access to CPC Registers                                                    |    |

| 6.2.6: Enabling Coherent Mode                                        | 112 |

|----------------------------------------------------------------------|-----|

| 6.2.7: Master Clock Prescaler                                        |     |

| 6.2.8: Individual Device Clock Ratio Modification                    |     |

| 6.2.8.1: Clock Domain Change Example — Register Programming Sequence |     |

| 6.2.8.2: Clock Change Delay                                          |     |

| 6.2.9: CM Standalone Powerup                                         |     |

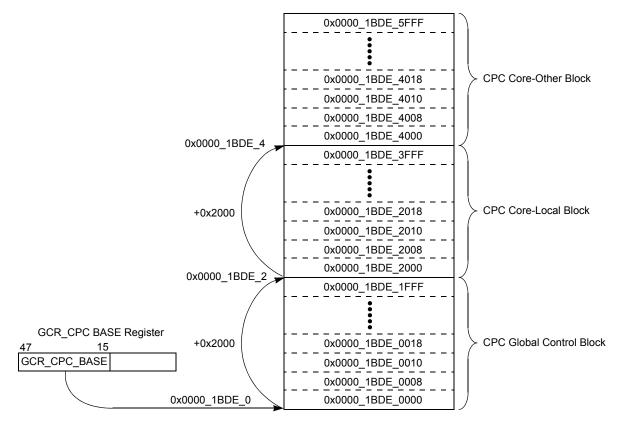

| 6.2.10: Reset Detection                                              |     |

| 6.2.11: VP Run/Suspend.                                              |     |

| 6.2.12: Local RAM Deep Sleep / Shutdown and Wakeup Delay             |     |

| 6.2.12.1: RAM Deep Sleep Mode                                        |     |

| 6.2.12.2: RAM Shut Down Mode                                         |     |

| 6.2.13: Accessing the CPC Registers in Another Power Domain          |     |

| 6.2.14: Fine Tuning Internal and External Signal Delays              |     |

| 6.2.14.1: Global Sequence Delay Count                                |     |

|                                                                      |     |

| 6.2.14.2: Rail Delay<br>6.2.14.3: Reset Delay                        |     |

| 0.2. 14.3. Reset Delay                                               |     |

| Chapter 7: Global Interrupt Controller                               | 123 |

| Chapter 7: Global Interrupt Controller<br>7.1: Overview.             |     |

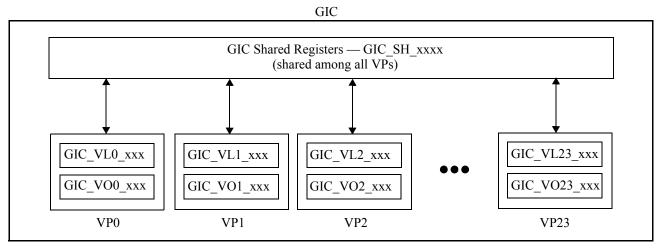

| 7.1.1: GIC Virtualization                                            |     |

|                                                                      |     |

| 7.1.2: GIC Operating Modes                                           |     |

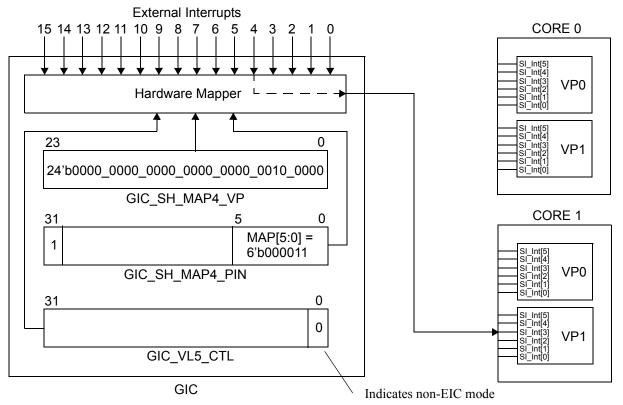

| 7.1.2.1: Non-EIC Mode                                                |     |

| 7.1.2.2: EIC Mode                                                    |     |

| 7.1.3: GIC Register Types                                            |     |

| 7.1.4: GIC Register Distribution                                     |     |

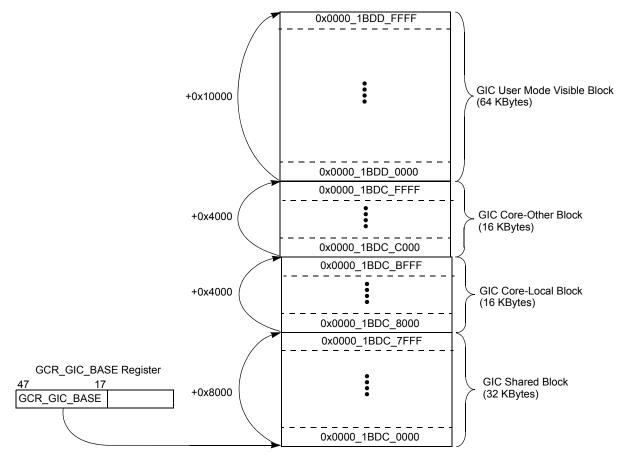

| 7.1.5: GIC Address Space Configuration                               |     |

| 7.2: GIC Programming                                                 |     |

| 7.2.1: Setting the GIC Base Address and Enabling the GIC             |     |

| 7.2.2: Determining the Number of External Interrupts in the System   |     |

| 7.2.3: EIC Mode Setting                                              |     |

| 7.2.4: Configuring Interrupt Sources                                 |     |

| 7.2.4.1: Trigger Type Register Group                                 |     |

| 7.2.4.2: Edge Type Register Group                                    |     |

| 7.2.4.3: Polarity Type Register Group                                |     |

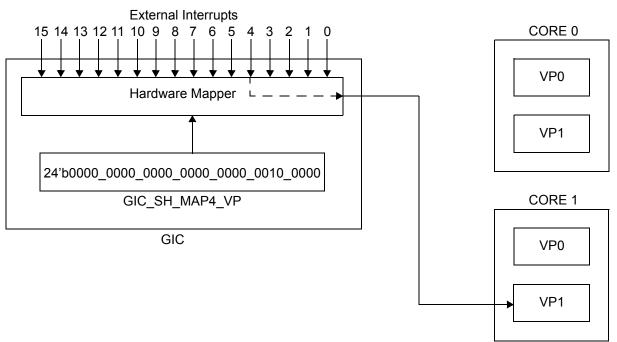

| 7.2.5: Interrupt Routing                                             |     |

| 7.2.5.1: Mapping an Interrupt Source to a VP                         |     |

| 7.2.5.2: Mapping an Interrupt Source to a Specific Processor Pin     |     |

| 7.2.6: Enabling, Disabling, and Polling Interrupts                   |     |

| 7.2.6.1: Enabling External Interrupts                                |     |

| 7.2.6.2: Disabling External Interrupts                               |     |

| 7.2.6.3: Determining the Enabled or Disabled Interrupt State         | 136 |

| 7.2.6.4: Polling for an Active Interrupt                             | 137 |

| 7.2.6.5: Programming Example                                         | 137 |

| 7.2.7: Inter-processor Interrupts                                    | 138 |

| 7.2.7.1: WEDGE Register Programming Example                          | 139 |

| 7.2.8: Local Timer Configuration                                     | 140 |

| 7.2.8.1: GIC Interval Timer                                          |     |

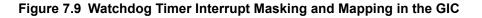

| 7.2.8.2: GIC Watchdog Timer                                          |     |

| 7.2.9: Local Interrupt Routing and Masking                           |     |

| 7.2.9.1: Local Interrupt Routing                                     |     |

| 7.2.9.2: Local Interrupt Masking                                     |     |

| 7.3: Virtualization Support                                          |     |

| 7.3.1: Enabling Virtualization Mode                                  |     |

| ✓                                                                    |     |

| 7.3.2: Routing of Guest External Source Interrupts                             | 147 |

|--------------------------------------------------------------------------------|-----|

| 7.3.3: Qualification of Root or Guest Software Access to GIC registers         |     |

| 7.3.4: Guest Mode Count-Compare Timer Interrupts                               |     |

| 7.3.5: Watchdog (WD) Timer Guest and Root Interrupts                           |     |

| 7.4: GIC User-Mode Visible Section                                             |     |

|                                                                                |     |

| Chapter 8: Floating-Point Unit (FPU)                                           | 151 |

| 8.1: Overview                                                                  |     |

| 8.1.1: IEEE Standard 754                                                       |     |

|                                                                                |     |

| 8.1.2: Floating Point Registers                                                |     |

| 8.2: Enabling the Floating-Point Unit                                          |     |

| 8.3: Setting a Floating Point Exception                                        |     |

| 8.4: Setting the Rounding Mode                                                 |     |

| 8.5: Operation of the FS Bit                                                   |     |

| 8.6: Programming the Floating Point FCSR Register                              |     |

| Chapter 9: MIPS® SIMD Architecture (MSA)                                       | 155 |

| 9.1: Overview of the SIMD Architecture                                         |     |

| 9.1.1: MSA Instruction Formats.                                                |     |

| 9.1.2: SIMD Instructions                                                       |     |

|                                                                                |     |

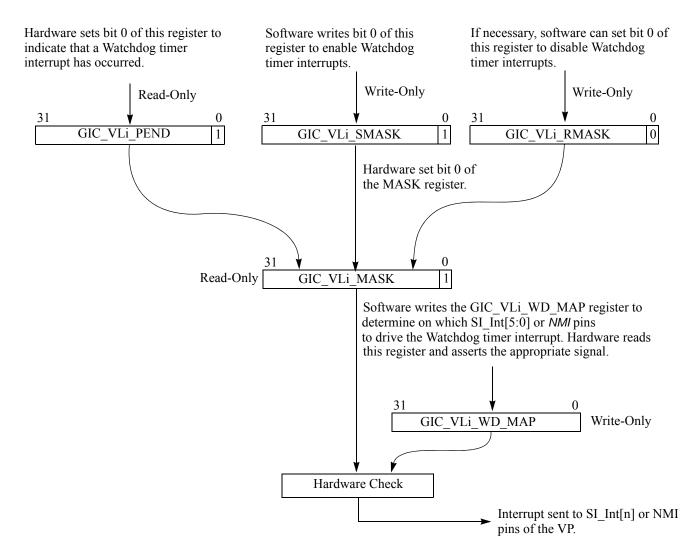

| 9.1.3: MSA Vector Registers<br>9.1.4: Layout of MSA Registers                  |     |

|                                                                                |     |

| 9.1.5: Mapping of Scalar Floating-Point Registers to MSA Vector Registers      |     |

| 9.2: MSA Programming                                                           |     |

| 9.2.1: Enabling MSA                                                            |     |

| 9.2.2: Setting a MSA Exception                                                 |     |

| 9.2.3: Setting the Rounding Mode                                               |     |

| 9.2.4: Operation of the FS Bit.                                                |     |

| 9.2.5: Operation of the NX Bit                                                 |     |

| 9.2.6: Programming the MSA CSR Register                                        |     |

| 9.3: MSA Exceptions                                                            |     |

| 9.3.1: MSA Exception Types                                                     |     |

| 9.3.2: MSA Non-Trapping Exceptions.                                            |     |

| 9.3.3: MSACSR Cause Register Field Update Pseudocode                           |     |

| 9.4: MSA GNU Compiler Support                                                  |     |

| 9.4.1: MSA ABI                                                                 |     |

| 9.4.1.1: ABI Requirements                                                      |     |

| 9.4.1.2: Command Line Options and Function Attributes                          |     |

| 9.4.1.3: Vector and Floating-Point Register Usage for -mmsa and -msimd-abi=msa |     |

| 9.4.1.4: Inter-calling Between MSA and non-MSA Functions                       |     |

| 9.4.1.5: MSA GNU Options and Directives                                        |     |

| 9.4.2: MSA Vector Element Selection                                            |     |

| 9.4.3: Examples                                                                | 169 |

| Chapter 10: Virtualization                                                     | 474 |

| Chapter 10: Virtualization                                                     |     |

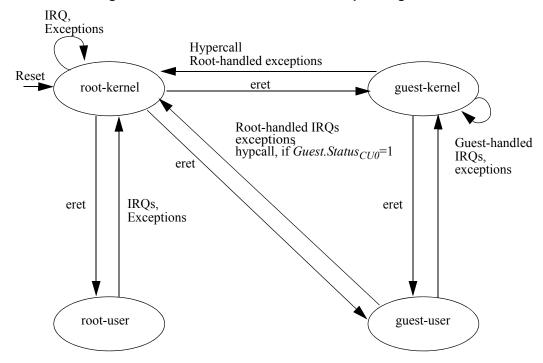

| 10.1.1: Root and Guest Operating Modes                                         |     |

|                                                                                |     |

| 10.1.2: Introduction to the Hypervisor                                         |     |

| 10.1.3: Enabling Guest Mode Translations<br>10.1.4: MMU Considerations         |     |

|                                                                                |     |

| 10.1.5: Guest ID<br>10.1.6: CP0 Structure in Rest and Cuest Mede               |     |

| 10.1.6: CP0 Structure in Root and Guest Mode                                   |     |

| 10.1.7: New CP0 Registers                                                          | 175 |

|------------------------------------------------------------------------------------|-----|

| 10.1.8: New CP0 Instructions                                                       |     |

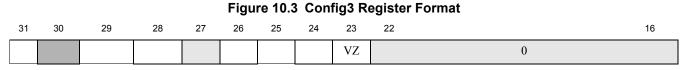

| 10.2: Software Detection of Virtualization.                                        |     |

| 10.3: Modes Of Operation                                                           |     |

| 10.3.1: Root Mode Operation                                                        |     |

| 10.3.2: Guest Mode Operation                                                       |     |

| 10.3.3: Debug Mode                                                                 |     |

| 10.4: Address Translation Pseudocode                                               |     |

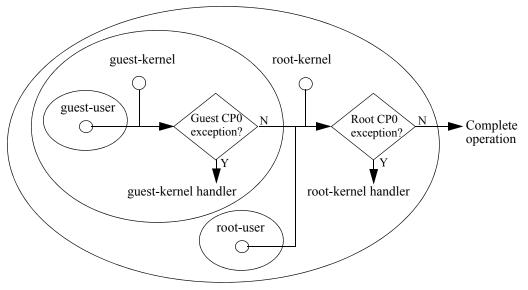

| 10.5: Exception Handling in Root and Guest Mode                                    |     |

| 10.5.1: Root and Guest Shared TLB Operation                                        |     |

| 10.5.1.1: Root and Guest Access to the Shared TLB.                                 |     |

|                                                                                    |     |

| 10.5.1.2: Wired Register Management                                                |     |

| 10.5.1.3: CP0 Register Allocation                                                  |     |

| 10.5.1.4: CP0 Register Access                                                      |     |

| 10.5.1.5: CP0 Register Initialization and Control                                  |     |

| 10.6: Exceptions                                                                   |     |

| 10.6.1: Exceptions in Guest Mode                                                   |     |

| 10.6.2: Faulting Address for Exceptions from Guest Mode                            |     |

| 10.6.3: Guest Initiated Root TLB Exception                                         |     |

| 10.6.4: Exception Priority                                                         |     |

| 10.6.5: Exception Vector Locations                                                 |     |

| 10.6.6: Synchronous and Synchronous Hypervisor Exceptions                          |     |

| 10.6.7: Guest Exception Code in Root Context                                       | 189 |

| 10.7: Interrupts                                                                   | 190 |

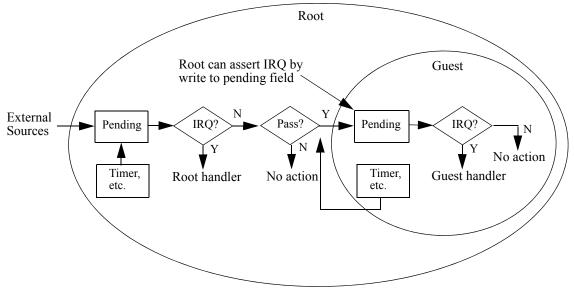

| 10.7.1: External Interrupts                                                        | 192 |

| 10.7.1.1: Non-EIC Interrupt Handling                                               | 192 |

| 10.7.1.2: EIC Interrupt Handling                                                   | 193 |

| 10.7.2: Derivation of Guest.CauseIP/RIPL                                           | 196 |

| 10.7.3: Timer Interrupts                                                           |     |

| 10.7.4: Performance Counter Interrupts                                             |     |

| 10.8: Watchpoint Debug Support                                                     |     |

| 10.9: Guest Mode and Debug Features                                                |     |

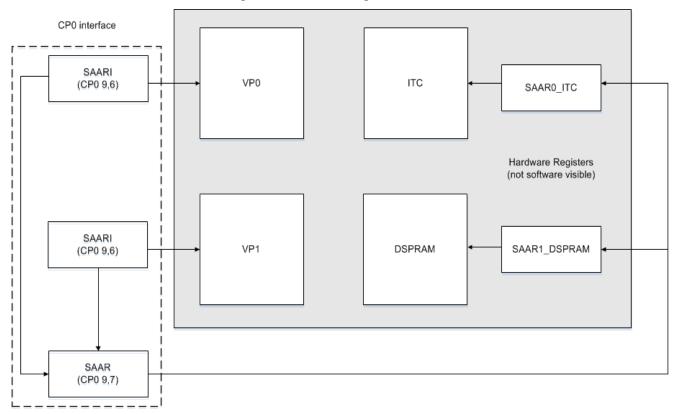

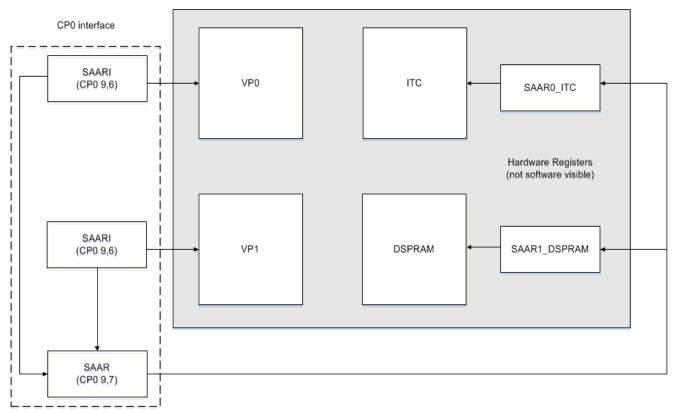

| Chapter 11: Data Scratch Pad RAM                                                   | 202 |

|                                                                                    |     |

| 11.1: Overview                                                                     |     |

| 11.1.1: New CP0 Registers                                                          |     |

| 11.1.1.1: Special Address Access Register Index — SAARI (CP0 Register 9, Select 6) |     |

| 11.1.1.2: Special Address Access Register — SAAR (CP0 Register 9, Select 7)        |     |

| 11.1.2: Changes to Existing CP0 Registers — Error Reporting                        |     |

| 11.1.2.1: Error Control — ErrCtl (CP0 Register 26, Select 0)                       |     |

| 11.1.2.2: Cache Error — CacheErr (CP0 Register 27, Select 0)                       |     |

| 11.2: DSPRAM Software Interface                                                    |     |

| 11.3: Accessing the DSPRAM                                                         |     |

| 11.3.1: Register Programming Sequence                                              | 206 |

| 11.3.2: Programming Constraints                                                    | 207 |

| Chapter 12: Inter-Thread Communication Unit                                        | 209 |

| 12.1: Overview                                                                     |     |

| 12.1.1: New CP0 Registers                                                          |     |

| 12.1.1.1: Special Access Address Register Index — SAARI (CP0 Register 9, Select 6) |     |

| 12.1.1.2: Special Access Address Register — SAAR (CP0 Register 9, Select 0)        |     |

| 12.1.2. ITU Control Register                                                       |     |

| 12.1.2. ITU Control Register                                                       |     |

|                                                                                    |     |

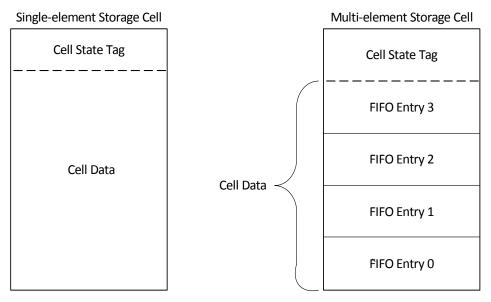

| 12.2.1: ITU Cell Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 12.2.2: Cell Views                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

| 12.2.3: Cell State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

| 12.2.4: ITU Cell Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |

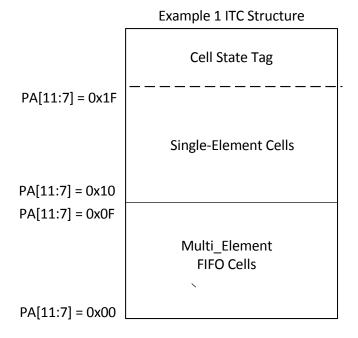

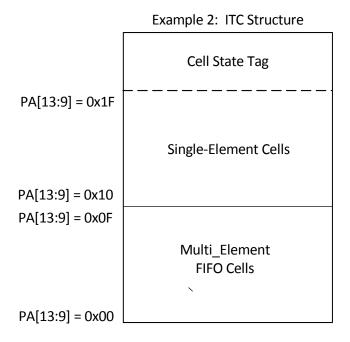

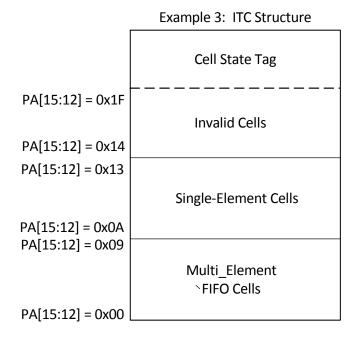

| 12.2.5: Cell Indexing Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

| 12.2.5.1: Example 1: 32 Cells with No Index Shift and No Invalid Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |

| 12.2.5.2: Example 2: 32 Cells with 2-Bit Index Shift and No Invalid Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |

| 12.2.5.3: Example 2: 20 Cells with 4-Bit Index Shift and Invalid Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |

| 12.3: ITU Software Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                    |

| 12.4: Accessing the ITU Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

| 12.4.1: Register Programming Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 220                                                                |

| 12.4.2: Programming Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 221                                                                |

| 12.5: ITU Error Reporting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 221                                                                |

| 12.5.1: AXI Bus Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 221                                                                |

| 12.5.2: Parity Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |

| 12.5.3: Execution Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

| Chapter 13: Multithreading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

| 13.1: Instruction Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |

| 13.2: Data Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

| 13.3: Thread Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

| 13.3.1: Disable Virtual Processor (DVP) Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 225                                                                |

| 13.3.2: Enable Virtual Processor (EVP) Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 225                                                                |

| 13.4: Independent Exception Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

| Chapter 14: MIPS On-Chip Instrumentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 227                                                                |

| Chapter 14: MIPS On-Chip Instrumentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

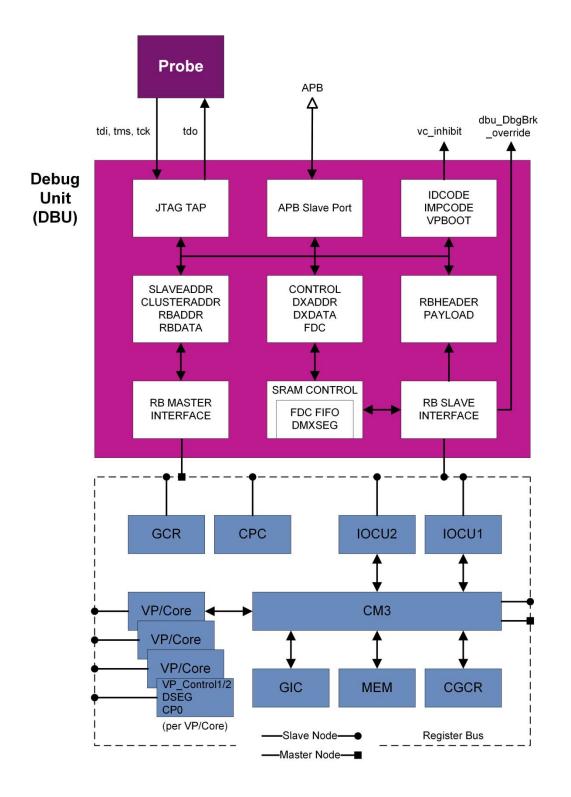

| 14.1: OCI Debug System Overview<br>14.1.1: Debug Unit (DBU)<br>14.1.1.1: APB Slave Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

| 14.1: OCI Debug System Overview<br>14.1.1: Debug Unit (DBU)<br>14.1.1.1: APB Slave Port<br>14.1.1.2: JTAG TAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                    |

| 14.1: OCI Debug System Overview<br>14.1.1: Debug Unit (DBU)<br>14.1.1.1: APB Slave Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

| 14.1: OCI Debug System Overview<br>14.1.1: Debug Unit (DBU)<br>14.1.1.1: APB Slave Port<br>14.1.1.2: JTAG TAP<br>14.1.1.3: Debug Monitor<br>14.1.1.4: RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

| 14.1: OCI Debug System Overview.<br>14.1: Debug Unit (DBU)<br>14.1.1: APB Slave Port.<br>14.1.1.2: JTAG TAP<br>14.1.1.3: Debug Monitor<br>14.1.1.4: RAM.<br>14.1.2: Register Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 227<br>227<br>229<br>229<br>229<br>229<br>229<br>229<br>229        |

| 14.1: OCI Debug System Overview.<br>14.1: Debug Unit (DBU)<br>14.1.1: APB Slave Port.<br>14.1.1.2: JTAG TAP<br>14.1.1.3: Debug Monitor<br>14.1.1.4: RAM.<br>14.1.2: Register Bus<br>14.1.3: Number of Breakpoints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 227<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229 |

| 14.1: OCI Debug System Overview.<br>14.1: Debug Unit (DBU)<br>14.1.1: APB Slave Port.<br>14.1.1.2: JTAG TAP<br>14.1.1.3: Debug Monitor<br>14.1.1.4: RAM.<br>14.1.2: Register Bus.<br>14.1.2: Register Bus.<br>14.1.3: Number of Breakpoints<br>14.1.4: Per Core/VP Resources.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 227<br>227<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229 |

| 14.1: OCI Debug System Overview.<br>14.1.1: Debug Unit (DBU)<br>14.1.1: APB Slave Port.<br>14.1.1.2: JTAG TAP<br>14.1.1.3: Debug Monitor<br>14.1.1.4: RAM.<br>14.1.2: Register Bus.<br>14.1.2: Register Bus.<br>14.1.3: Number of Breakpoints<br>14.1.4: Per Core/VP Resources<br>14.1.4.1: Breakpoint Controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 227<br>227<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229 |

| 14.1: OCI Debug System Overview.<br>14.1.1: Debug Unit (DBU)<br>14.1.1: APB Slave Port.<br>14.1.1.2: JTAG TAP<br>14.1.1.3: Debug Monitor.<br>14.1.1.4: RAM.<br>14.1.2: Register Bus.<br>14.1.2: Register Bus.<br>14.1.3: Number of Breakpoints.<br>14.1.4: Per Core/VP Resources.<br>14.1.4: Breakpoint Controller.<br>14.1.4.2: Dseg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 227<br>227<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229 |

| 14.1: OCI Debug System Overview.<br>14.1.1: Debug Unit (DBU)<br>14.1.1: APB Slave Port.<br>14.1.1.2: JTAG TAP.<br>14.1.1.3: Debug Monitor.<br>14.1.1.4: RAM.<br>14.1.2: Register Bus.<br>14.1.2: Register Bus.<br>14.1.3: Number of Breakpoints.<br>14.1.4: Per Core/VP Resources.<br>14.1.4: Breakpoint Controller.<br>14.1.4.1: Breakpoint Controller.<br>14.1.4.2: Dseg.<br>14.1.4.3: Dmseg.                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

| 14.1: OCI Debug System Overview.<br>14.1.1: Debug Unit (DBU)<br>14.1.1: APB Slave Port.<br>14.1.1.2: JTAG TAP<br>14.1.1.3: Debug Monitor<br>14.1.1.4: RAM.<br>14.1.2: Register Bus.<br>14.1.3: Number of Breakpoints<br>14.1.3: Number of Breakpoints<br>14.1.4: Per Core/VP Resources.<br>14.1.4.1: Breakpoint Controller.<br>14.1.4.2: Dseg<br>14.1.4.3: Dmseg<br>14.1.4.4: Drseg.                                                                                                                                                                                                                                                                                                                                                                                                                                       | 227<br>227<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229 |

| 14.1: OCI Debug System Overview.<br>14.1.1: Debug Unit (DBU)<br>14.1.1: APB Slave Port.<br>14.1.1.2: JTAG TAP<br>14.1.1.3: Debug Monitor<br>14.1.1.4: RAM.<br>14.1.2: Register Bus.<br>14.1.3: Number of Breakpoints<br>14.1.4: Per Core/VP Resources.<br>14.1.4.1: Breakpoint Controller.<br>14.1.4.2: Dseg<br>14.1.4.3: Dmseg<br>14.1.4.4: Drseg.<br>14.1.4.5: CP0 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                             | 227<br>227<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229 |

| 14.1: OCI Debug System Overview.<br>14.1.1: Debug Unit (DBU)<br>14.1.1.1: APB Slave Port.<br>14.1.1.2: JTAG TAP<br>14.1.1.3: Debug Monitor<br>14.1.1.4: RAM.<br>14.1.2: Register Bus.<br>14.1.2: Register Bus.<br>14.1.3: Number of Breakpoints<br>14.1.4: Per Core/VP Resources.<br>14.1.4.1: Breakpoint Controller.<br>14.1.4.2: Dseg.<br>14.1.4.3: Dmseg.<br>14.1.4.3: Dmseg.<br>14.1.4.4: Drseg.<br>14.1.4.5: CP0 Registers<br>14.1.5: Coherence Devices.                                                                                                                                                                                                                                                                                                                                                              | 227<br>227<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229 |

| <ul> <li>14.1: OCI Debug System Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 227<br>227<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229 |

| 14.1: OCI Debug System Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 227<br>227<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229 |

| 14.1: OCI Debug System Overview.14.1.1: Debug Unit (DBU)14.1.1: APB Slave Port.14.1.1.2: JTAG TAP14.1.1.3: Debug Monitor14.1.1.4: RAM.14.1.2: Register Bus.14.1.3: Number of Breakpoints14.1.4: Per Core/VP Resources14.1.4: Breakpoint Controller14.1.4.1: Breakpoint Controller14.1.4.2: Dseg14.1.4.3: Dmseg14.1.4.4: Drseg14.1.5: Coherence Devices14.1.5: Coherence Devices14.1.5.1: GIC (Global Interrupt Controller)14.1.5.3: GCR (Global Configuration Registers)                                                                                                                                                                                                                                                                                                                                                   | 227<br>227<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229 |

| 14.1: OCI Debug System Overview.<br>14.1.1: Debug Unit (DBU)<br>14.1.1: APB Slave Port.<br>14.1.1.2: JTAG TAP<br>14.1.1.3: Debug Monitor.<br>14.1.1.4: RAM.<br>14.1.2: Register Bus.<br>14.1.3: Number of Breakpoints.<br>14.1.4: Per Core/VP Resources.<br>14.1.4: Per Core/VP Resources.<br>14.1.4.1: Breakpoint Controller.<br>14.1.4.2: Dseg.<br>14.1.4.3: Dmseg.<br>14.1.4.3: Dmseg.<br>14.1.4.4: Drseg.<br>14.1.4.5: CP0 Registers.<br>14.1.5: Coherence Devices.<br>14.1.5.1: GIC (Global Interrupt Controller).<br>14.1.5.2: CPC (Cluster Power Controller).<br>14.1.5.3: GCR (Global Configuration Registers).<br>14.1.5.4: CGCR - (Custom Global Configuration Registers).<br>14.1.5.4: CGCR - (Custom Global Configuration Registers).                                                                          |                                                                    |

| 14.1: OCI Debug System Overview.         14.1.1: Debug Unit (DBU)         14.1.1: APB Slave Port.         14.1.1.2: JTAG TAP         14.1.1.3: Debug Monitor         14.1.1.4: RAM.         14.1.2: Register Bus.         14.1.3: Number of Breakpoints         14.1.4: Per Core/VP Resources.         14.1.4: Breakpoint Controller         14.1.4: Dseg         14.1.4: Drseg         14.1.4: Drseg         14.1.4: Drseg         14.1.5: Coherence Devices.         14.1.5.1: GIC (Global Interrupt Controller)         14.1.5.2: CPC (Cluster Power Controller)         14.1.5.3: GCR (Global Configuration Registers)         14.1.5.4: CGCR - (Custom Global Configuration Registers)         14.1.5.5: CM - (Coherence Manager) (v3)                                                                                | 227<br>227<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229 |

| 14.1: OCI Debug System Overview.<br>14.1.1: Debug Unit (DBU).<br>14.1.1.1: APB Slave Port.<br>14.1.1.2: JTAG TAP.<br>14.1.1.3: Debug Monitor.<br>14.1.4: RAM.<br>14.1.2: Register Bus.<br>14.1.3: Number of Breakpoints.<br>14.1.4: Per Core/VP Resources.<br>14.1.4: Per Core/VP Resources.<br>14.1.4.1: Breakpoint Controller.<br>14.1.4.2: Dseg.<br>14.1.4.3: Dmseg.<br>14.1.4.4: Drseg.<br>14.1.4.5: CP0 Registers.<br>14.1.5: Coherence Devices.<br>14.1.5: Coherence Devices.<br>14.1.5.1: GIC (Global Interrupt Controller).<br>14.1.5.2: CPC (Cluster Power Controller).<br>14.1.5.3: GCR (Global Configuration Registers).<br>14.1.5.4: CGCR - (Custom Global Configuration Registers).<br>14.1.5.4: CGCR - (Custom Global Configuration Registers).<br>14.1.5.4: CGCR - (Custom Global Configuration Registers). | 227<br>227<br>229<br>229<br>229<br>229<br>229<br>229<br>229<br>229 |

Chapter 1

## **Architecture Overview**

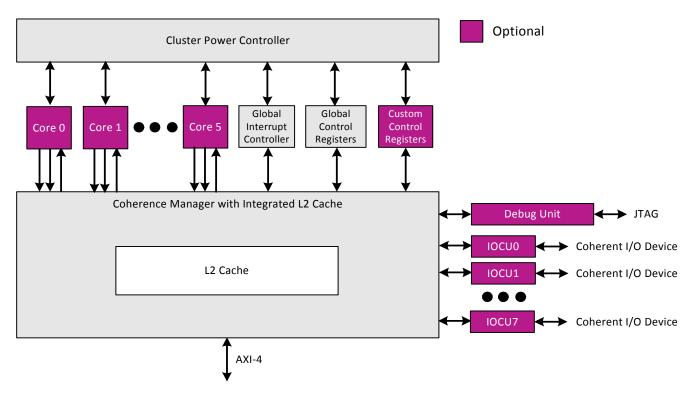

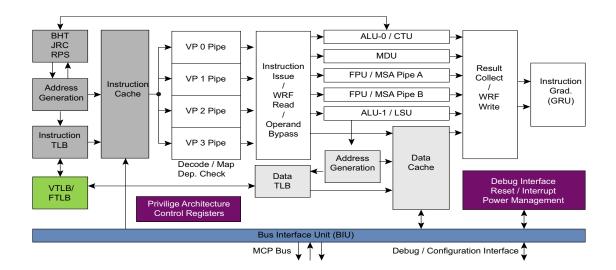

This document describes the software-programmable aspects of the 64-bit MIPS I6500 Multiprocessing System (MPS). The device consists of the logic blocks shown in Figure 1.1. The majority of blocks in the diagram have at least one dedicated chapter that describes how to control the hardware using registers and assembly code. The register-programming examples describe a programming sequence of how to set or change a programmable parameter using registers. The assembly code examples show how the MIPS instruction set can be used to perform the same function.

Each chapter provides the relevant background information required by the programmer in order to understand the examples. Common examples such as enabling and initialization are provided for each block, as well as more in depth examples relative to that block.

An overview of the material provided in this document is as follows:

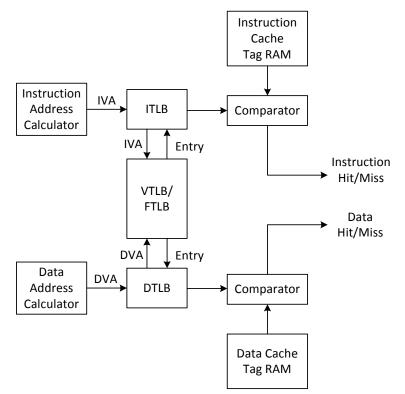

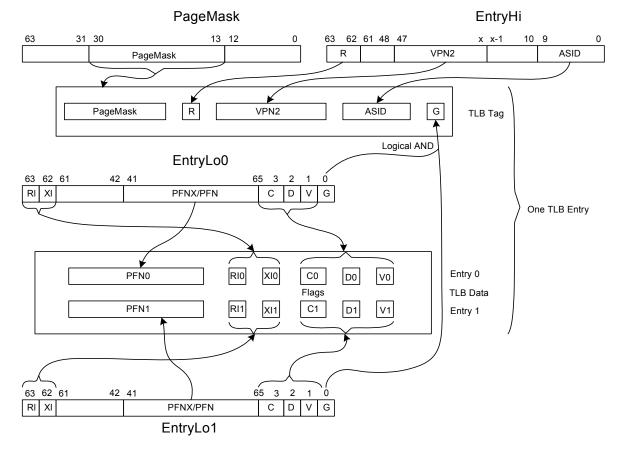

- *Memory Management (MMU)*: This chapter describes the programmable elements of the Translation Lookaside Buffer or TLB of the I6500 Multiprocessing System. The first section gives an overview of the TLB architecture, a description of its functionality and a description of the elements that go into programming the TLB. The sections that follow cover specific information on programming for the Translation Lookaside Buffer (TLB).

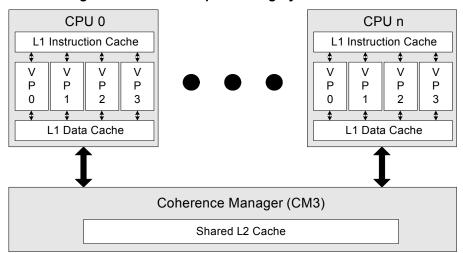

- *Caches*: This chapter provides an overview of the cache architecture, a description of its functionality, and a description of the elements that go into programing the caches. A description of the CP0 register interface to each cache is provided, as well as initialization code for all three caches, setting up cache coherency, handling cache exceptions, and testing the cache RAM.

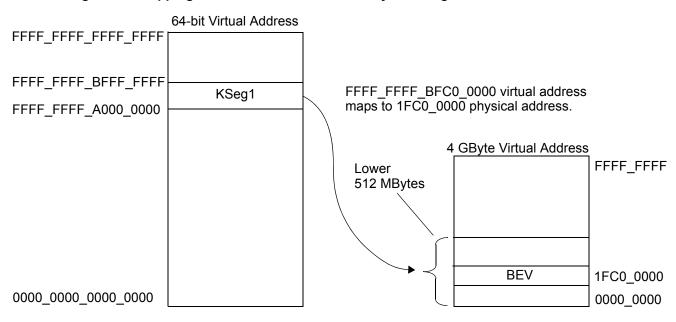

- *Exceptions*: This chapter describes an overview of exception processing and a definition of the interrupt modes. Information on how to program the reset, boot, and general exception vectors in memory is also covered. A list of exception priorities is provided, along with an assembly language example of an exception handler.

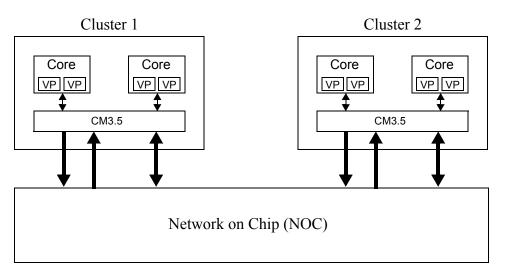

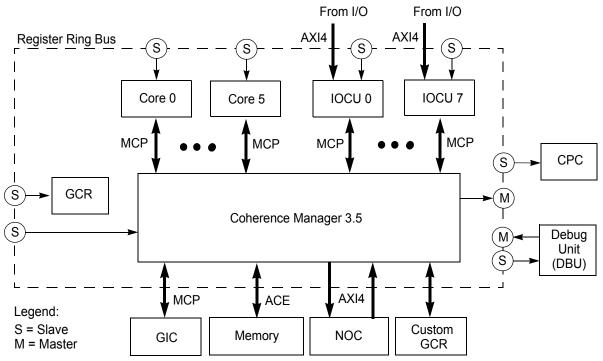

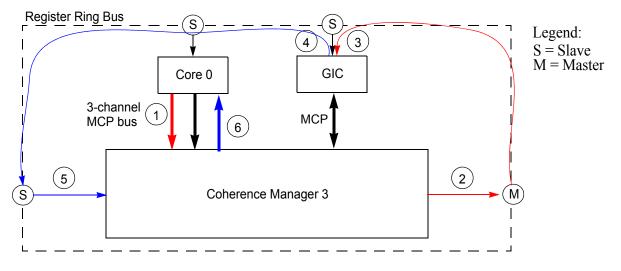

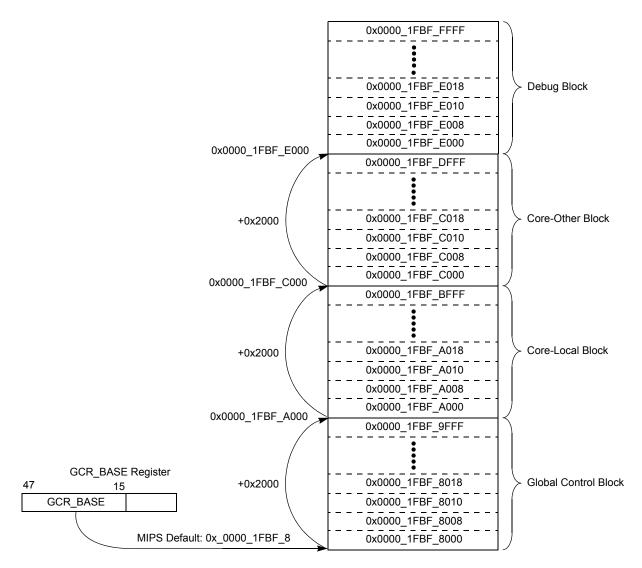

- *Coherence Manager* (CM): The I6500 MPS contains a third generation Coherence Manager. This chapter provides an overview of the CM register ring bus and associated table that lists each device ID on the bus. The programmer uses this information to access these devices. An overview of the CM register address space is also provided. In addition, the chapter describes how to program the CM to perform various functions, including setting the base addresses in memory, accessing another VP in the same core, accessing a VP in another core, accessing the Global Interrupt Controller (GIC), Cluster Power Controller (CPC), and/or Debug Unit (DBU) registers via the CM, and setting the clock ratios between the various I6500 system components. For the exact revision number of the Coherence Manager, refer to the Release Notes.

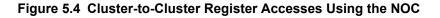

This chapter also introduces the multi-cluster configuration that allows multiple I6500 Multiprocessing Systems to be connected through a Network-On-Chip (NOC) interface. The section describes the registers used to perform a cluster-to-cluster access.

Cluster Power Controller (CPC): This chapter provides an overview of how power is managed in the I6500 Multiprocessing System and identifies the various power and clock domains the programmer can use to manage power consumption in the device. In addition, a procedure on how to set the CPC base address in memory is provided. Other programming principles include setting the device to coherent or non-coherent mode, requestor (core or IOCU) access of CPC registers, system power-up policy, programming examples of a clock domain change and clock delay change, powering up the CPC in standalone mode (no cores enabled), reset detection, VP

run/suspend mechanism, local RAM shutdown and wake-up procedure, accessing registers in another power domain, and fine tuning internal and external signal delays to help the programmer easily integrate the device into a system environment.

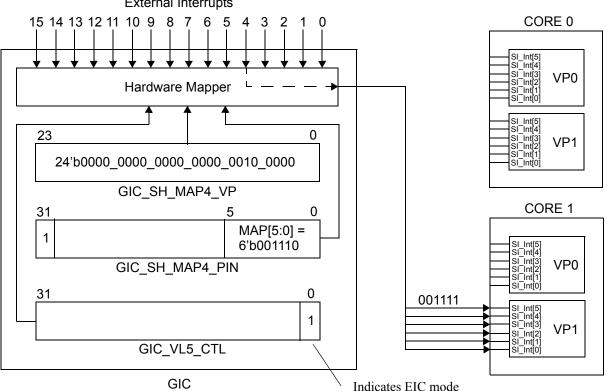

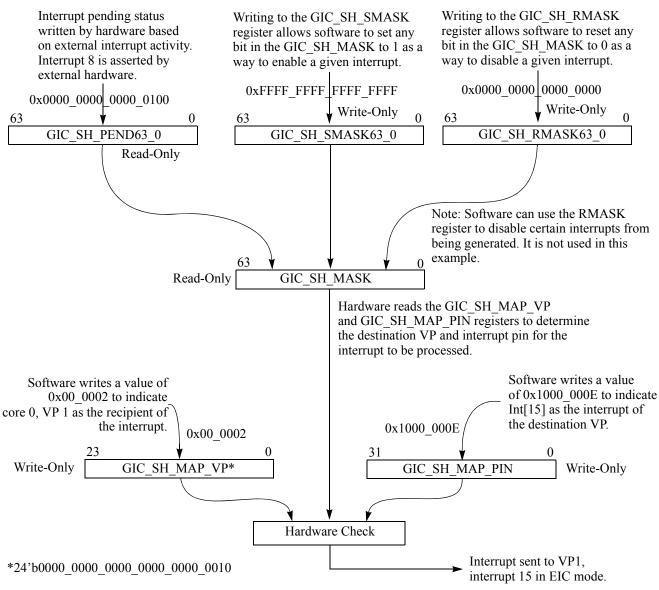

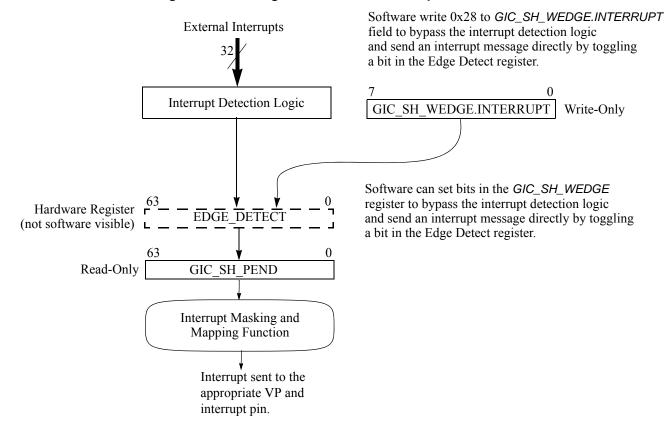

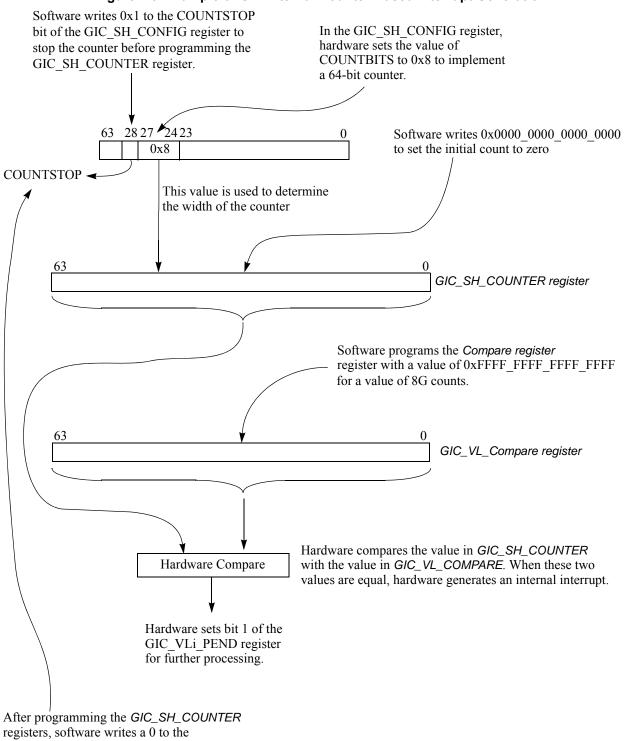

- *Global Interrupt Controller (GIC)*: This chapter describes how to program the various elements of the GIC using both register examples and code examples. Some of these elements include setting the operating mode, setting up the address map, GIC register layout and distribution, setting the GIC base address, determining the number of external interrupts, and configuring individual interrupt sources.

- *Floating Point Unit (FPU)*: This chapter provides information on how to enable the FPU, how to handle floating point exceptions, how to set the rounding mode, and operation of the Flush-to-Zero (FS) function.

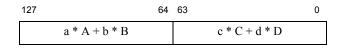

- *MIPS SIMD Architecture (MSA)*: This chapter describes the MIPS Single-Instruction-Multiple-Data (SIMD) architecture. It provides information on how to enable MSA, how to map scalar floating point registers to MSA vector registers, and MSA exception handling.