# Addressing Design Challenges in 32-bit Microcontrollers For Automotive and Industrial Applications

October 2007

## **Next-Generation Microcontrollers**

Microcontrollers (MCUs) connect and control systems ranging from basic household appliances like dishwashers to advanced media-rich consumer devices. For the past 20 years, 8-bit devices have dominated the market, but a broader range of end-user systems with increased levels of functionality are driving a transition from 8- and 16-bit devices toward 32-bit processor-based MCUs with the performance and features needed for more sophisticated applications.

The transition from 8- and 16-bit to 32-bit MCUs is well underway. According to Semico Research, in 2011, total shipments of 32-bit MCUs will exceed 2 billion units, with revenues increasing at an 18 percent annual growth rate.

As the industry transitions to 32-bit MCUs, designers require not only increased functionality, but also a wide range of peripherals, including high-performance IP such as USB and audio codecs.

With a broad array of processor cores and a comprehensive, diverse library of proven analog IP blocks, MIPS Technologies has the largest offering of both processor and peripheral IP from a single supplier providing customers with a total system solution for 32-bit MCU applications.

## The Limitations of 8- and 16-bit MCUs

8- and 16-bit MCUs are a good fit for lower end applications. These applications tend to be monolithic – requiring a single processor that, under control of a simple kernel, need only carry out one simple, specific task. The memory requirement for such an application falls under the maximum addressing range of 8- and 16-bit processors.

The average selling price of an 8- or 16-bit microcontroller with a limited set of basic peripherals is in the range \$1 - \$2, making them effective options for solutions demanding ultra-low cost and minimum performance.

But though 8- and 16-bit MCUs are still suitable at the low-end, limitations of these MCUs make them unsuitable for applications that demand more compute-intensive, feature-rich capabilities. Such limitations include datapath width, maximum addressing range, relatively low power efficiency, limited C code support and lack of available advanced debug-capable development tools. 16-bit microcontrollers also suffer from the lack of a dominant standard architecture, restricting ecosystem support.

# Benefits of 32-bit MCUs

To illustrate the benefits a 32-bit processor has over an 8-bit processor, consider a motor control design, a common application in many industrial and domestic products.

The speed and power of a motor are regulated by the pulse width modulator (PWM) circuitry of the MCU. An 8-bit MCU would typically be able to measure the motor speed and modify the PWM signal accordingly once every 100ms. A 32-bit processor, running at the same clock speed, would be capable of four or five times that rate, allowing for improved accuracy and more efficient control.

The extra headroom afforded by using a 32-bit processor could allow it to run other processes simultaneously, increasing its functionality, such as power factor correction or TCP/IP controlled remote control/diagnostic tasks.

32-bit processors provide the increased computational performance and memory, low power, integrated connectivity and software support needed for many of today's sophisticated MCU-based end-products. And the price of a mid- to high-end 8- or 16-bit MCU is equivalent to that of a 32-bit MCU.

#### Microcontroller System Development Issues

32-bit processors are capable of addressing the higher levels of performance and increased software support required by the next generation of MCUs. The challenge facing developers is determining which MCU architecture best meets the design specification, minimizes system cost and provides the tools needed to reduce risk and time-tomarket.

One issue developers must consider is power management, especially in the design of battery powered devices, industrial control systems and domestic appliances that are required to comply with a maximum power rating standard. Dynamic power is proportional to CV2F, which translated means that power consumption increases as the frequency to achieve the required performance increases. As process geometries shrink to enable operating frequencies, the amount of leakage current increases, further adding to power consumption.

Embedded flash takes a majority of an MCU device's total die area, and therefore has the biggest influence on end-product cost. It is common for MCUs to embed at least 256KBytes of flash memory storage for the software to support the RTOS, complex algorithm code and network protocol stacks that are needed to meet the OEM product specification. The MCU architecture must employ design features that reduce the code size required to execute the application, which in turn will reduce the amount of flash memory and therefore the device cost.

Deterministic operation is critical in many motor control applications. To achieve the desired performance it is common for some 32-bit processors to employ complex, multi-way associative cache architectures and multi-stage pipelines to maximize execution throughput. However, cache misses and pipeline stalls can have an adverse effect on a product's real-time behavior. These types of systems may need to service hundreds of interrupts within a determined time to ensure fail-safe operation (a high speed machine tool or vehicle braking system, for example). It is important therefore that a cached-based processor used in this type of environment employs a high frequency pipeline architecture that effectively deals with potential stalls and exceptions, and a cache design able to achieve a high hit rate.

Other designs don't need such high performance, and operate at a lower frequency without caches, incorporating a non-cached based SRAM design.

To maximize reuse and accommodate different application requirements, it is advantageous to use a standard architecture that has a high degree of configurability and flexibility built in.

By definition, MCUs contain a mix of digital and analog components. Typically, 8-bit MCUs can be manufactured in a low-cost 0.25um process to achieve the performance required for their particular application. The transition to higher-performance systems requires not only the use of 32-bit processors, but also that MCUs be manufactured in smaller 0.13um and 90nm geometries.

# **Overview of Microcontroller Markets and Applications**

The industrial and automotive markets are two of the largest consumers of MCU devices. This section discusses trends and the types of products used within these sectors, as well as how MIPS Technologies' solutions can help developers of MCUs for these markets differentiate and speed their designs to market.

## Industrial

The industrial sector has the widest array of end-products of all MCU markets, with more than 400 million units forecasted to be shipped in 2010. Products range from singlefunction motors, power converters and meters used in factory and domestic appliances to more integrated secure network systems and medical equipment.

A common trend in industrial products is the move toward mechatronic type systems, where more intelligent electronic systems replace or are added to mechanical systems. One example of mechatronics is a home thermostat, where electronics provide a greater level of programmability and accuracy that can result in reduced energy costs.

Incorporating an MCU into a mechatronic design can increase its functionality with the addition of features such as LCD displays, improve its efficiency through techniques such as pulse width modulation (PWM)—to more precisely control system variables, add more user-friendly features and reduce costs. It can also add flexibility in the design process, allowing the same hardware to be used in a

wider range of applications by changing the software to meet the needs of each product.

Today, motor-controlled products are increasingly being produced to conform to "green" energy standards, such as Energy Star<sup>®</sup>, which requires the system to have an optimized balance of performance and power. Performance for MCUs is typically listed in DMIPS (Dhrystone Millions of Instructions Per Second) per MHz, and power efficiency in mW/DMIPS. The higher the DMIPS/MHz rating, the better the power efficiency, and the lower the frequency needed to achieve the required performance.

To achieve a high DMIPS performance rating with minimal operating frequency, MIPS Technologies' processors for the MCU market have extremely efficient micro-architectures built around a 5- or 8-stage pipeline and achieve performance levels greater than 1.5DMIPs/MHz. Additionally, an integer multiply/divide unit (MDU) accelerates the type of math functions commonly used in motor control software.

Industrial devices are becoming more interconnected, externally and internally within buildings, over high-speed wired and wireless networks. In a wired network configuration, the system MCU executes the TCP/IP protocol stack software and data-link firmware to facilitate the transport of data across the network nodes. In a wireless connection such as Zigbee or Bluetooth, the microcontroller controls the link between the air interface and baseband by executing complex medium access control (MAC) layer software. In either of these configurations, a high-performance 32-bit processor with memory management capabilities is required to facilitate the high data rate of the network, and support the RTOS used in this type of environment.

The more sensitive the data that is transferred across networks, the greater the need for MCUs to embed security features for data protection. The MIPS32<sup>®</sup> 4KSd<sup>™</sup> core, part of the 4K<sup>®</sup> core family, provides this protection through an Application Specific Extension (ASE) called SmartMIPS<sup>™</sup>, which adds cryptographic acceleration for algorithms such as RSA, ECC, DES and AES.

SmartMIPS also includes a secure memory management unit (MMU) that scrambles the cache interface, further increasing the level of protection provided. Adding the SmartMIPS extensions increases the core size by less than 10 percent, but provides up to 10 times the performance over a software-only implementation.

To add an even greater level of security, all MIPS Technologies' processor cores are synthesizable, enabling the MCU designer to arrange a custom floorplan of the device. This can reduce the possibility of "spoofing" by avoiding noticeable hotspots that could help identify code activity.

Medical devices normally have a higher level of functionality than most other industrial devices, combining several complex functions and interfaces in one device. Data is acquired from a variety of sensors that convert from analog to digital using delta-sigma converters and is processed using digital signal processing (DSP) techniques that are not normally found in standard microcontrollers. MIPS Technologies' microcontrollers have an option to include a DSP ASE, a set of more than 40 DSP-centric instructions that accelerate DSP algorithms of the type commonly used in medical equipment software: Fast Fourier Transforms (FFT) and Finite (FIR) and Infinite (IIR) Impulse Response Filters.

Multiply and multiply-accumulate (MAC) operations form the basis of many DSP algorithms. The performance required to execute these instructions is accelerated by an integrated integer MDU that is capable of completing a 32x32 multiply or MAC instructions in just two cycles, and a 32-bit wide SRAM or cache data interface that helps to extend dynamic range and precision. Medical devices also have local area network and personal area network communication capabilities similar to those in other industrial devices.

# Automotive

32-bit MCUs have a strong and growing presence in the automotive market. Until recently they have been consigned to be the solution of choice for higher end applications, including powertrain and telematics. This is changing as the automotive sectors that were previously the domain of 8- and 16-bit MCUs (body and convenience) now often require increasing levels of performance to execute more complex software and satisfy higher levels of functionality and safety.

Approximately 50 percent of a car's value is in its electronic content, with an average of more than 50 electronic control units (ECUs) in each vehicle. Today, electronic applications within a vehicle are expanding even further to address transport efficiency improvements and increased safety, and to facilitate the move towards more mechatronic solutions. ECUs are now used in all parts of a vehicle's design,

from basic convenience control functions to more complex engine management and multimedia-rich telematics.

Typical MCU applications within the automotive segments include:

Body and convenience systems

- Power windows

- Heating and ventilation

- Wipers and seat controls

- Smart keyless entry

Safety & Chassis

- Electronic stability

- Airbags

- Anti-lock brakes

- Tire pressure monitoring

Collision avoidance systems

#### Powertrain

- Engine management

- Transmission control

- Hybrid management

- Electronic power steering

Infotainment

- Navigation

- Telematics

- Dashboard control

Powertrain is the most compute-intensive of all the automotive applications, requiring management of a large array of engine sensors and controls within a real-time environment. MCUs used in powertrain applications must be designed for low interrupt latency, support high speed digital/analog interfaces, have DSP acceleration and high IPC performance. The processor core must also be capable of operating at frequencies often exceeding 300MHz.

Automotive systems must have a high level of functional safety and fault tolerance built-in to ensure dependable and predictable operation over the lifetime of the product, which could be 10 years or more.

Safety standards such as the generic-industry IEC 61508 and automotive-specific ISO 26262 define the maximum acceptable failure rates and fault tolerant features that should be included in the design and implemented in the development process. These standards apply to a range of automotive applications such as throttle control, transmission, braking, airbags, cruise control and collision avoidance.

MIPS Technologies' processor cores contain specific features that enable compliance to these safety standards, namely, kernel/supervisor/user modes, MMU, exception handling procedures, built in self test (BIST) and management of memory errors. The high quality and reliability of each processor core is assured as it goes through an extensive set of design verification procedures under the MIPS Verified<sup>™</sup> program. The type and extent of this testing helps to contribute to the complete system meeting the required Safety Integrity Levels (SILs) defined in the IEC 61508 specification.

Body and convenience systems have traditionally been designed using 8- or 16-bit processors. To reduce system complexity and increase reliability, multiple single-function 8- and 16-bit processor systems are now being aggregated into one 32-bit processor device that can execute multiple functions in a single module.

Automotive ECUs must operate in a wide variety of temperature ranges and environmental conditions, depending on the type of application and where within the vehicle they are situated. These devices must be robust, capable of withstanding extremes of voltage/current, have a high mean-time-to-failure (MTTF) and must be able to operate over an extended temperature range up to +125°C.

Devices must be proven in a foundry and manufacturing process that can support these requirements. While the majority of automotive ECUs are manufactured in mature process geometries ranging from 0.25um to 0.13um, more compute-intensive applications are now moving towards a 90nm process. All MIPS Technologies' processor cores are synthesizable, supported by leading EDA tools, and are portable across automotive-grade foundries that conform to these requirements.

#### **MIPS** Technologies' Solutions

MIPS Technologies provides a broad range of 32-bit processor cores that are based on a common MIPS32 standard architecture and are software compatible to the MIPS32<sup>®</sup> ISA (Instruction Set Architecture). Processor cores that are particularly well-suited for the design and development of microcontroller-based systems are the M4K<sup>®</sup>, 4K and 24K<sup>®</sup> core families.

#### Industry leading performance and low power consumption

MIPS Technologies cores for MCU applications have a high operating frequency that meets the most demanding of applications and provides headroom for lower performance critical systems. Bestin-class power efficiency reduces the power supply cost and extends the operating time of battery powered systems.

Example characterization data:

M4K @ 130nm (TSMCG):

- Max performance 228MHz, 1.53MIPs/MHz

- Min power 0.07 mW/MHz

#### 24KE @ 90nm (TSMCG):

- Max performance 575MHz, 1.46 DMIPs/MHz

- Min power 0.41 mW/MHz

## Size reduction features

The MIPS32 architecture was designed from the outset to be clean and efficient, true to RISC design philosophies. The M4K core in its standard configuration can have as few as 35K gates, which translates to a physical area of only 0.19mm<sup>2</sup> in a 0.13um process technology. Even the more advanced 8-stage pipeline 24K core family occupies only 1.1mm<sup>2</sup> of area in a 90nm standard process.

All MIPS Technologies' processor cores are capable of operating in both 32- and 16-bit modes. Execution of 16-bit code is achieved using MIPS16e<sup>™</sup>, a 16 bit re-encoding of the MIPS32 ISA that reduces code size by up to 40 percent that of 32-bit only code, with a minimal reduction in performance. Since embedded flash takes up the largest silicon area in a microcontroller integrated circuit, using MIPS16e to reduce the flash memory size will have a corresponding effect in reducing the product cost.

# **Real-Time operation**

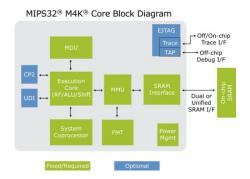

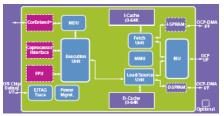

Real-time operation, a fundamental requirement of MCU systems, is achieved in MIPS Technologies' cores through an advanced interrupt controller and SRAM interface. The interrupt handling circuitry is designed using a vectored interrupt controller and multiple sets of 32bit general purpose (GPR) shadow registers. On receiving an interrupt, the internal or external controller provides a prioritized vector to a dedicated handler. Each vector can be assigned to a specific GPR shadow set. The M4K core has a cacheless architecture, designed to interface directly to SRAM memory.

Industrial and automotive systems operate in an environment that receives stimuli in the form of interrupts. These interrupts come from many sources, such as engine sensors and motor actuators, and they must be serviced within a specific, often limited, time to avoid system malfunction. The advanced interrupt handling capabilities and deterministic memory interface in MIPS Technologies' cores ensure these real-time service requirements are met.

# Configurability

MIPS Technologies' cores provide a high level of extensibility and configurability during synthesis, enabling designers to optimize the cores for different applications and performance/cost requirements. Designers can configure cache size and type, number of register sets, debug functionality, power management control, co-processor interface, and instruction set extensions.

MCU semiconductor vendors often provide multiple products that differ only slightly from each other. The differences tend to be in frequency, memory size and integrated peripherals. The level of configurability in MIPS Technologies' cores enables the deployment of optimized, application-specific, cost effective solutions.

# **Memory Protection**

All MIPS Technologies' cores include a Memory Management Unit (MMU). The MMU used in the M4K core is FMT/TLB (Fixed Mapping Translation / Translation Lookaside Buffer) based. The 4K and 24K core families include a 16-, 32- or 64-bit dual-entry joint TLB based MMU.

Virtually all automotive applications, and an increasing number of industrial systems, use an RTOS to control and manage the system software. Most RTOSs require a MMU to provide encapsulation and protection of code. This is an important consideration in automotive system design, especially in braking and drive control applications, to minimize the potential for software crashes and system malfunctions.

# Application Specific Extensions (ASEs)

To further enhance configurability and performance benefits, MIPS Technologies provides several ASEs that are designed to accelerate specific functions in MCU systems. The SmartMIPS ASE incorporates features that accelerate standard cryptographic algorithms and increase system protection. The DSP ASE is a set of instructions and algorithms designed specifically to execute more efficient signal processing functions. CorExtend<sup>™</sup> is an extension to the standard architecture that enables designers to create custom instructions to accelerate application-specific functions.

As described earlier, industrial and automotive systems increasingly require more advanced security and digital processing capabilities. MIPS Technologies' ASEs help in the system development process by instantiating certain features in hardware, thereby reducing the design time and effort required.

# Floating Point Unit (FPU)

The 24KEf<sup>™</sup> core integrates an IEEE 754 compliant floating point unit (FPU) that supports both single and double precision formats. The FPU is an autonomous unit, implemented as a separate fully pipelined unit that also includes its own set of 64-bit registers.

The floating point capabilities of the 24KEf core provide a greater dynamic range and accuracy than fixed point calculations, an important requirement particularly when executing engine management software. Adding the floating point capability enables modeling software such as The Mathworks' Matlab and Simulink to develop models of the powertrain system. Tools such as ASCET-CE or dSPACE Targetlink can then auto-generate code from these models.

A processor with floating point capabilities can reduce development time by taking advantage of this modeling-based, auto-code generation methodology.

# Analog IP

MIPS Technologies offers a broad array of more than 400 proven analog and mixed-signal IP cores developed in geometries ranging from 0.25um to 32nm. These cores fall into four main product areas: audio and power controllers (Sigma Delta audio analog front end [AFE], battery/power management units and DC-DC converters consuming <100uA at a 95% efficiency level); video DACs and AFEs used in a wide array of portable/home consumer devices and wireless networks; wired connectivity solutions (USB 2.0 controllers and PHYs, LVDS and HDMI interfaces); and wireless connectivity solutions (cellular analog baseband and RF transceivers).

Access to these cores early in the development process can reduce risk and integration effort, and their availability in a wide range of geometries and foundry processes can reduce cost and development time. By dealing with expert analog designers and the leading provider of foundry-proven analog IP, developers can have increased confidence in achieving "first-time right design."

## **Development Tools**

Availability of quality development tools is one of the most important criteria MCU system developers consider when choosing a processor for their application. MIPS Technologies offers a comprehensive set of software development and hardware debug tools. The software tools include a GNU-based toolchain and MIPSsim<sup>™</sup> cycle and instruction accurate simulator. The hardware tools include Eclipse-based IDE debug probes that have advanced breakpoint, complex triggers and iFlowtrace<sup>™</sup> debug capabilities with support for both on- or off-chip trace memory.

iFlowtrace traces all instructions with a high degree of compression, helping to reduce required bandwidth, yet can capture all program flow, status and conditions, giving complete visibility into how the software is executing. Non-intrusive cycle accurate code verification and real-time hardware debug capabilities allow capture and analysis of system events in real time, an important consideration for highly interrupt event driven industrial and automotive designs.

Complex triggers, a unique feature offered by MIPS Technologies, enable a more sophisticated level of debugging that gives developers a more accurate view of system dynamics. Embedded trace buffer and control further enhance design verification by capturing pre- and postevent data in real time.

MCU systems, in particular those used in the industrial and automotive sectors, are complex, high-performance systems with an eclectic mix of peripherals and features designed to function in a real-time environment. The integrated software and hardware tools that MIPS Technologies delivers with its processor cores have capabilities that provide an extensive level of design verification, reduce overall

development time and provide a high level of confidence that the product will function as designed when released to production.

Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.

This document contains information that is proprietary to MIPS Tech, LLC, a Wave Computing company ("MIPS") and MIPS' affiliates as applicable. Any copying, reproducing, modifying or use of this information (in whole or in part) that is not expressly permitted in writing by MIPS or MIPS' affiliates as applicable or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines. Any document provided in source format (i.e., in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS (AND MIPS' AFFILIATES AS APPLICABLE) reserve the right to change the information contained in this document to improve function, design or otherwise.

MIPS and MIPS' affiliates do not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Except as expressly provided in any written license agreement from MIPS or an authorized third party, the furnishing of this document does not give recipient any license to any intellectual property rights, including any patent rights, that cover the information in this document.

The information contained in this document shall not be exported, reexported, transferred, or released, directly or indirectly, in violation of the law of any country or international law, regulation, treaty, Executive Order, statute, amendments or supplements thereto. Should a conflict arise regarding the export, reexport, transfer, or release of the information contained in this document, the laws of the United States of America shall be the governing law.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.

MIPS I, MIPS II, MIPS II, MIPS IV, MIPS V, MIPSr3, MIPS32, MIPS64, microMIPS32, microMIPS64, MIPS-3D, MIPS16, MIPS16e, MIPS-Based, MIPSsim, MIPSpro, MIPS-VERIFIED, Aptiv logo, microAptiv logo, interAptiv logo, microMIPS logo, MIPS Technologies logo, MIPS-VERIFIED logo, proAptiv logo, 4K, 4Kc, 4Km, 4Kp, 4KE, 4KEc, 4KEm, 4KEp, 4KS, 4KSc, 4KSd, M4K, M14K, 5K, 5Kc, 5Kf, 24K, 24Kc, 24Kf, 24KE, 24KEc, 24KEf, 34K, 34Kc, 34Kf, 74K, 74Kc, 74Kf, 1004K, 1004Kc, 1004Kf, 1074K, 1074Kc, 1074Kf, R3000, R4000, R5000, Aptiv, ASMACRO, Atlas, "At the core of the user experience.", BusBridge, Bus Navigator, CLAM, CorExtend, CoreFPGA, CoreLV, EC, FPGA View, FS2, FS2 FIRST SILICON SOLUTIONS logo, FS2 NAVIGATOR, HyperDebug, HyperJTAG, IASim, iFlowtrace, interAptiv, JALGO, Logic Navigator, Malta, MDMX, MED, MGB, microAptiv, microMIPS, Navigator, OCI, PDtrace, the Pipeline, proAptiv, Pro Series, SEAD-3, SmartMIPS, SOC-it, and YAMON are trademarks or registered trademarks of MIPS and MIPS' affiliates as applicable in the United States and other countries.

All other trademarks referred to herein are the property of their respective owners.